關鍵詞: GPS中頻信號;USB;信號采集;數據分析

中圖分類號: TN967.1

文獻標識碼: A

DOI:10.16157/j.issn.0258-7998.170792

中文引用格式: 陶夢,李金城. GPS中頻信號采集及分析系統設計[J].電子技術應用,2017,43(9):34-38.

英文引用格式: Tao Meng,Li Jincheng. Design of a system for sampling and analysis of GPS IF signal[J].Application of Electronic Technique,2017,43(9):34-38.

0 引言

隨著GPS全球衛星定位系統在提供定位信息和高精度時間信息上的廣泛應用,國內外越來越多的企業和研究機構深入研究導航、授時芯片,而要實現這些功能,都離不開對GPS衛星信號的分析。因此,自主研發小型化、便攜式GPS中頻信號數據采集設備對導航算法研究及芯片設計非常重要[1]。

USB接口數據傳輸速率高、傳輸模式靈活,支持低速(1.5 Mb/s)、全速(12 Mb/s)和高速(480 Mb/s)3種傳輸速度以及中斷傳輸、控制傳輸、同步傳輸和塊傳輸4種傳輸模式,目前在PC領域中USB接口已廣泛應用[2]。高集成度的GPS接收機射頻前端芯片NJ1006可采集2 bit格式的GPS衛星信號,通過位拼接可將實時采樣率下降至4 MHz左右。USB2.0的傳輸速度完全可以滿足,而從成本和普及率方面綜合考慮,使用USB2.0是一個較好的選擇。

基于上述分析,本論文設計了一種GPS中頻信號采集及分析系統。系統使用FPGA對NJ1006的數字中頻信號進行字節拼接及緩存,通過USB接口芯片(FX2 68013)上傳到PC。在PC端設計了專用的VC++程序,用于PC端的數據接收、格式轉換及分析。

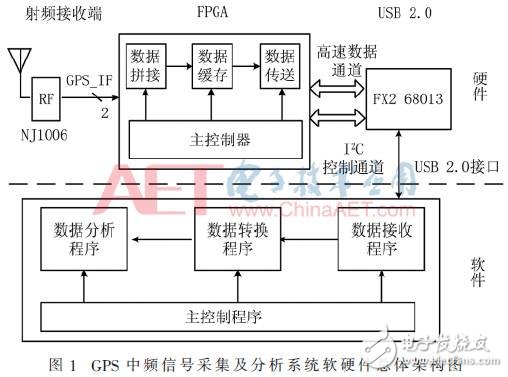

1 系統軟硬件總體架構

本論文的GPS中頻信號采集及分析系統的軟硬件總體架構如圖1所示,由硬件和軟件兩部分組成。其中硬件部分包括GPS射頻接收芯片NJ1006、FPGA(cyclone EP1C12Q240C8N,具有20 060個邏輯單元和52個M4K存儲器)和 USB2.0接口芯片(FX2-68013);軟件部分包括數據接收程序、格式轉換程序、數據分析程序和主控程序組成。

NJ1006是一個高集成度的GPS接收機射頻前端IC,其集成了LNA和本機振蕩器的諧振回路,減少了外部元器件數量和PCB的面積。NJ1006下變頻1 575.42 MHz GPS L1信號,通過2 bit A/D轉換器采樣后,輸出采樣率為16.368 MHz,中頻頻率為4.092 MHz的2 bits數字信號(符號位SGN和大小位MAG)到FPGA。

FX2-68013是由Cypress半導體公司所推出的USB2.0芯片,芯片將USB外圍接口所需要的各種功能包裝成一精簡的集成電路,其內部的8051微處理器方便對芯片的控制與配置[3]。通過對芯片內部8051編程,使USB2.0芯片配置在Slave FIFO模式下工作,異步方式傳輸數據,以支持圖1中的高速數據通道;由于該USB2.0芯片具有I2C接口,支持對外部I2C存儲器的讀寫,為了不影響高速數據傳輸,本論文用FPGA模擬了一個I2C存儲器,上位機通過對I2C存儲器的讀寫實現了對FPGA工作狀態的控制[4]。

FPGA接收NJ1006的數字中頻信號,進行位拼接和緩存,向USB2.0芯片發送數據,并通過USB2.0接口將采集的數據上傳到PC。在PC端接收數據,并進行格式轉換和數據分析。分析的主要任務是對GPS中頻信號進行C/A碼相位和多普勒頻率的二維相關值計算,并由Matlab進行三維立體顯示。

2 FPGA邏輯設計

2.1 數據拼接

GPS衛星信號是在16.368 MHz時鐘下利用射頻前端NJ1006接收得到的,由于該信號的位寬為2 bits,而FPGA與USB之間的數據總線位寬為8 bits,因此需通過“串并轉換”,將串行數據轉換為并行數據。此時,寫入數據速度降低到原來的四分之一(4.092 MHz),將大大降低數據上傳所需的時序要求。

2.2 數據緩存

USB2.0協議擁有較快的數據傳輸速率,但本設計使用Windows系統PC作為上位機,屬于多任務系統,運行時會分出多個時間片給各應用程序,即使只運行本設計中的軟件程序,也無法保證穩定的傳輸速度,將影響數據的實時傳輸性。為解決該問題,可通過增加存儲器以緩存數據。但由于外部增加RAM的成本較大,且前文中提到的數據流采集速率約為穩定不變的4 MHz,而Windows平均的傳輸數據速率高于此采集速率,為了保證數據流的連續性,可利用FPGA 內部52個M4K存儲器資源生成26 KB RAM作為緩沖器,把從位拼接得到的數據暫存在此RAM中,再通過USB2.0傳輸到上位機PC中進行存儲和分析。

本系統中把這26 KB緩存空間分成13個2 KB RAM,將從位拼接得到的數據依次寫進RAM中,同時將寫滿2 KB RAM的緩存數據依次讀出傳送至FX2,之后FX2一次性將2 KB數據通過USB2.0傳輸至上位機,由此對RAM0至RAM12這13個存儲器進行循環操作,完成數據的讀寫操作。該方法能夠最大限度地利用資源,保證了數據流的實時不間斷。

緩存數據寫入RAM的過程如圖2(a)所示。系統在接收到RAM的寫指令后,首先向RAM0寫入采集到的數據。當RAM0寫滿后,若RAM1處于忙狀態(即Rd_en[1]=1,系統從RAM1中讀出數據),則終止寫入,系統回歸初始狀態,等待寫指令,否則無間斷地向RAM1中寫入數據。由此依次對RAM0至RAM12這13個存儲器進行循環操作,完成數據的寫入。該RAM寫操作機制能夠保證數據流的實時、不間斷,符合數據采集要求。而緩存數據的讀出過程如圖2(b)所示。系統在接收到RAM的讀指令后,首先從RAM0中讀出數據,將其傳送至FX2的Slave FIFO。完成RAM0的讀操作后,若RAM1處于空閑狀態(即Wr_en [1]=0,系統未向RAM1寫入數據),則無間斷地讀取RAM1中的緩存數據,否則等待RAM1完成寫操作之后再繼續進行讀操作。對RAM0至RAM12這13個存儲器進行循環讀操作,直到采集結束。

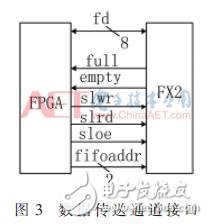

2.3 數據傳送

數據傳送即通過FX2 的Slave FIFO模式,將從RAM中讀出的數據上傳至上位機PC并保存,其高速數據傳送通道接口圖如圖3所示[5]。在開始傳送數據前,需通過Slave FIFO的切換地址fifoaddr配置Slave FIFO為2′b10,使其能夠向FX2的Slave FIFO寫入數據。接收到數據傳送指令后,主程序實時監控Slave FIFO的空滿標志empty、full。當發現Slave FIFO未滿時,通過控制Slave FIFO的寫時鐘slwr,將從RAM讀出的數據傳送至Slave FIFO的雙向數據端口fd,構成了高速數據通道,完成數據上傳。

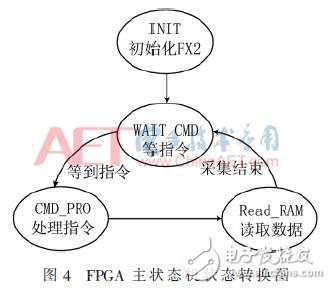

2.4 FPGA狀態轉換

FPGA主狀態機的狀態轉換圖如圖4所示,整個狀態機工作在72 MHz時鐘下,INIT狀態對FX2各接口數據進行初始化,之后進入WAIT_CMD狀態,等待上位機發指令。當上位機發出采集指令后,由USB向FX2內部8051芯片下傳48 B數據發送指令,再由8051將此48 B數據寫入I2C的存儲器,并分析第一字節數據[6]。當第一字節為8′h0a時,狀態機進入CMD_PRO狀態,進行指令處理,向RAM發出寫指令開始數據緩存,然后進入READ_RAM狀態,在識別FX2中Slave FIFO的空滿標志等信號后,讀出RAM緩存數據。關于RAM讀寫調用在上文中有詳細介紹,這里不再贅述。當采集結束后,狀態機重新回到WAIT_CMD狀態,等待下一次采集。

本設計中的采集結束機制分為兩種情況,一種是當要向單個RAM寫入數據時系統正在讀出該RAM中的數據,無法繼續進行寫操作,導致實時傳輸數據中斷。此時上位機長時間接收不到數據,將自動終止接收數據,這是由數據實時傳輸數據速率大于上位機接收數據速率導致的,此時軟件將通知用戶此次數據不可靠;另一種是上位機接收到的數據已經滿足采集數據的大小要求,此時上位機主動停止接收數據,FX2 slave FIFO一直處于滿狀態,FPGA超過規定時間的等待還不能繼續上傳數據,狀態機回到WAIT_CMD狀態,此次采集結束,等待下一次采集。

3 軟件操作

上位機程序使用C語言的MFC編寫,操作界面如圖5所示。USB Connection鍵可對FX2中的8051芯片進行配置,實現USB和FPGA數據通道連接。點擊圖中的Sample鍵,發出采集指令后,上位機開始調用FX2專用的批量端點上傳函數,反復循環128次來接收256 KB數據,等待接收數據,再通過USB傳輸指令,使FPGA與上位機協同工作,采集數據[7]。

數據采集結束后,可通過軟件操作界面的TXT Conversion窗口將數據格式轉換為ASCII碼或對應的0-1二進制序列,方便用戶使用。

通過圖5中的SV-Searching Paramenters窗口可設置參數,進行數據分析。源文件為當前數據采集轉換后的0-1二進制序列文件,通過設置衛星號SV num(1至32號衛星)、毫秒積分ms num(1 ms至10 ms)、量化位LO bits(1 bits至10 bits)和多普勒頻率范圍LO Frequency、CA碼相位C/A Phase以及相對應的頻率步長LO Step、C/A步長C/A Step等參數,點擊Analysis鍵,對其進行CA碼和多普勒頻率的二維搜索。通過時域串行捕獲算法計算得到三維數據,并利用Matlab的surf函數仿真出三維立體圖,從而分析信號的可靠性[8]。

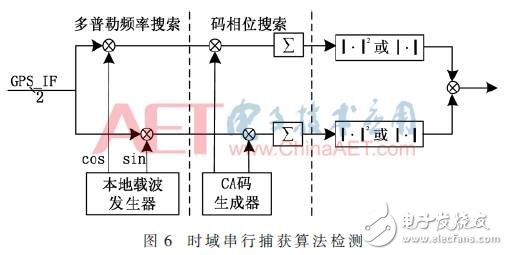

時域串行捕獲算法如圖6所示,即本地載波生成器在預先設定的多普勒頻率范圍內選擇一個載波頻率,產生兩路相位差 90°的本地載波cos和sin。將輸入信號與這兩路本地載波混頻,得到同相分量I和正交分量Q。然后將I和Q兩路分量分別與本地產生的C/A碼序列進行相關運算,并通過絕對值求和Absolute或平方求和square運算得到相關值[9-10]。

4 GPS中頻信號采集及分析結果

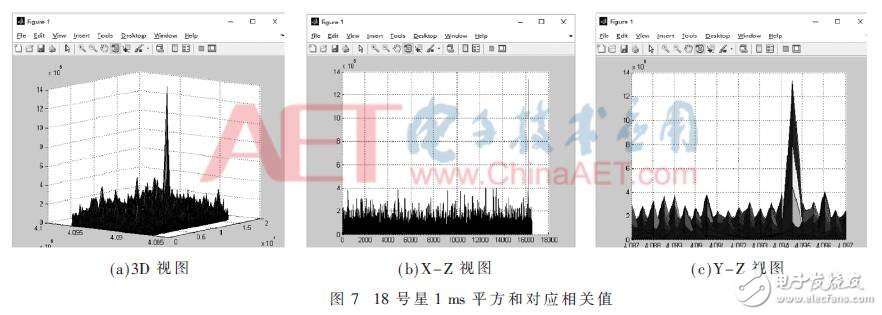

本文通過圖形操作界面對衛星信號進行采集、轉換和分析,實現了自主研發小型化、便攜式GPS中頻信號數據采集設備。GPS衛星信號數據于2017年1月13日下午1點20分在北京交通大學第九教學樓采集,此時的18號星1 ms平方和運算對應相關值如圖7所示。從圖中可明顯觀察到,該衛星的頻率在4.094 5 MHz附近,碼相位在16 000點附近出現明顯的相關峰。圖8則是18號星進行絕對值求和對應的相關圖,對比圖7和圖8可以看出,在信號明顯的情況下兩種運算都能找到相關峰,但絕對值求和得到的相關值基數更小,所需的硬件資源更少,相比之下,平方求和其相關峰則更加明顯。

在全搜索的基礎上,找到相關峰后還可對其進行更精確的搜索。在圖7 18號星全搜索的基礎上,將頻率搜索范圍縮小到4.092~4.097 MHz,并縮小頻率步長為250、CA碼步長為2,對其相關峰進行放大分析,其結果如圖9所示,該方法便于分析算法的可靠性以及信號正確性。

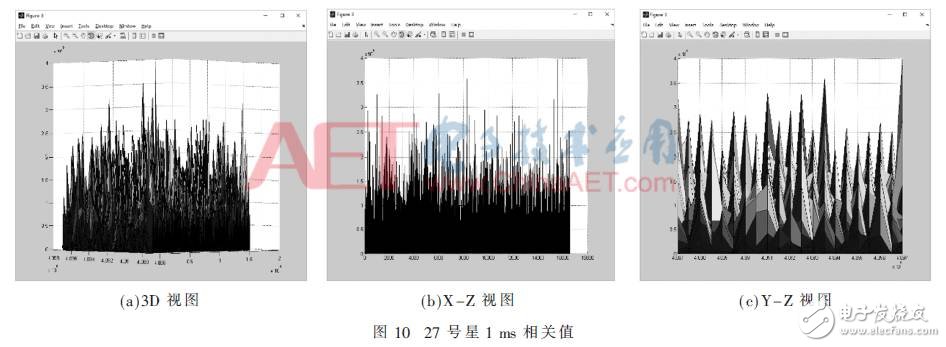

軟件還支持多毫秒疊加,設置多普勒搜索步長、頻率和CA碼采樣點數等。由于當前某顆衛星的信號比較弱,1 ms相關值累加有可能不能準確地找出相關峰,此時可通過多毫秒累積的方法得到相關峰。圖10為27號星1 ms的相關值,從圖中不能明顯地觀察到相關峰,但通過圖11中的2 ms運算可以看到,在頻率為4.092 MHz、碼相位為8 000處有明顯的相關峰。

5 結論

本文針對GPS中頻信號的采樣、轉換、分析提出了相應的解決方案。實驗證明,基于USB2.0的數據傳輸方案達到了對GPS中頻信號高速準確的采集目標。基于GPS的捕獲算法,通過C語言實現時域串行捕獲算法檢測,驗證了數據的可靠性,為之后的GPS算法研究奠定了堅實的基礎。

-

GPS中頻信號采集

+關注

關注

0文章

1瀏覽量

1864 -

GPS系統設計

+關注

關注

0文章

1瀏覽量

1911

原文標題:【論文精選】GPS中頻信號采集及分析系統設計

文章出處:【微信號:ChinaAET,微信公眾號:電子技術應用ChinaAET】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

一種GPS信號干擾源的設計與實現

數字方法中頻信號相干檢波實現

中頻信號與伴音信號處理電路

NewStar210A數字回放式GPS中頻信號采樣器

基于GPS中頻信號源的FPGA設計實現方案

GPS中頻信號采集及分析系統設計知識分享

GPS中頻信號采集及分析系統設計知識分享

評論