DDR3是目前DDR的主流產品,DDR3的讀寫分離作為DDR最基本也是最常用的部分,本文主要闡述DDR3讀寫分離的方法。最開始的DDR, 芯片采用的是TSOP封裝,管腳露在芯片兩側的,測試起來相當方便;但是,DDRII和III就不一樣了,它采用的是BGA封裝,所有焊點是藏在芯片的底部的,測試起來非常不便,一般需要提前預留測試點。在DDR讀寫burst分析之前,首先得把read burst和write burst分離出來,讀寫雙向的數據全部都擱在DQS和DQ上。那么,DDR的手冊中,留下了那些線索供我們進行都寫的分離呢?要實現DDR的快速的便捷的分離,在讀寫分離之前,我們必須得知道DDR讀寫信號之間的特征差異。首先,看看SPEC里面的定義:

方法一:preamble的差異在每次的burst之前,DQS會從高阻態切換到一段負脈沖,然后才開始正常的讀寫。這段負脈沖,我們叫做preamble(preamble實際上是在讀寫前,DQS提前通知DRAM芯片或者是controller的信號)。一般說來,讀數據DQS的preamble寬度要大于寫數據。對于DDR3,情況就更簡單了。因為在DDR3中,讀數據的preamble是負脈沖,寫數據的preamble是正脈沖。

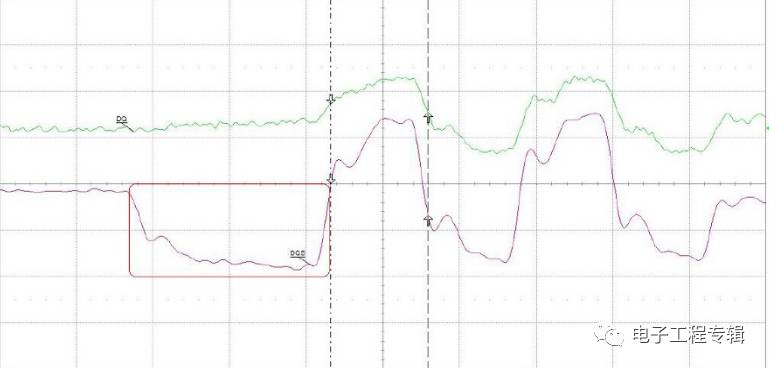

方法二:幅度上的差異一般在DRAM端進行測試,寫數據從memory controller出來,經過了主板PCB板,內存插槽和內存條PCB板,到達DRAM顆粒的時候,信號已經被衰減了,而讀數據剛剛從DRAM出來,還沒有經過任何的衰減,因此讀數據的幅度要大于寫數據。如下圖所示方法三:寫數據是DQS和DQ centre-align(中間對齊), 讀數據DQS和DQ是edge align(邊沿對齊),memory controller在接收到內存的讀數據時,在controller內部把DQS和DQ的相位錯開90度,實現中間對齊來采樣(這個過程示波器就看不到咯);方法四:斜率的差異:讀數據的斜率大于寫數據。一般在DRAM端進行測試,寫數據從memory controller出來,經過了主板PCB板,內存插槽和內存條PCB板,到達DRAM顆粒的時候,信號已經被衰減了,所以,斜率也小一些;而讀數據剛剛從DRAM出來,還沒有經過任何的衰減,因此讀數據的斜率要大于寫數據。也可以從下圖得到區分。

-

DDR3

+關注

關注

2文章

273瀏覽量

42080

原文標題:四種方法搞懂DDR3的讀寫分離

文章出處:【微信號:eet-china,微信公眾號:電子工程專輯】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

基于FPGA的DDR3多端口讀寫存儲管理系統設計

【紫光同創國產FPGA教程】【第十章】DDR3讀寫測試實驗

基于FPGA的DDR3多端口讀寫存儲管理設計

cyclone V控制DDR3的讀寫,quartusII配置DDR3 ip核后,如何調用實現DDR3的讀寫呢,謝謝

基于FPGA的DDR3多端口讀寫存儲管理的設計與實現

DDR3芯片讀寫控制及調試總結

ddr4和ddr3內存的區別,可以通用嗎

基于FPGA的DDR3多端口讀寫存儲管理的設計與實現

ddr3的讀寫分離方法有哪些?

ddr3的讀寫分離方法有哪些?

評論