在學習一門技術之前我們往往從它的編程語言入手,比如學習單片機時,我們往往從匯編或者C語言入門。所以不少開始接觸FPGA的開發人員,往往是從VHDL或者Verilog開始入手學習的。但我個人認為,若能先結合《數字電路基礎》系統學習各種74系列邏輯電路,深刻理解邏輯功能,對于學習HDL語言大有裨益,往往會起到事半功倍的效果。

當然,任何編程語言的學習都不是一朝一夕的事,經驗技巧的積累都是在點滴中完成,FPGA設計也無例外。下面就以我的切身體會,談談FPGA設計的經驗技巧。

我們先談一下FPGA基本知識:

FPGA(Field-Programmable Gate Array),即現場可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎上進一步發展的產物。它是作為專用集成電路領域中的一種半定制電路而出現的,既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。

1、硬件設計基本原則

(1)速度與面積平衡和互換原則:一個設計如果時序余量較大,所能跑的頻率遠高于設計要求,能可以通過模塊復用來減少整個設計消耗的芯片面積,這就是用速度優勢換面積的節約;反之,如果一個設計的時序要求很高,普通方法達不到設計頻率,那么可以通過數據流串并轉換,并行復制多個操作模塊,對整個設計采用“乒乓操作”和“串并轉換”的思想進行處理,在芯片輸出模塊處再對數據進行“并串轉換”。從而實現了用面積復制換取速度的提高。

(2)硬件原則:理解HDL本質

(3)系統原則:整體把握

(4)同步設計原則:設計時序穩定的基本原則

2、Verilog作為一種HDL語言,對系統行為的建模方式是分層次的。比較重要的層次有系統級、算法級、寄存器傳輸級、邏輯級、門級、電路開關級。

3、實際工作中,除了描述仿真測試激勵時使用for循環語句外,極少在RTL級編碼中使用for循環,這是因為for循環會被綜合器展開為所有變量情況的執行語句,每個變量獨立占用寄存器資源,不能有效的復用硬件邏輯資源,造成巨大的浪費。一般常用case語句代替。

4、if…else…和case在嵌套描述時是有很大區別的,if…else…是有優先級的,一般來說,第一個if的優先級最高,最后一個else的優先級最低。而case語句是平行語句,它是沒有優先級的,而建立優先級結構需要耗費大量的邏輯資源,所以能用case的地方就不要用if…else…語句。

補充:1.也可以用if…; if…; if…;描述不帶優先級的“平行”語句。

5、FPGA一般觸發器資源比較豐富,而CPLD組合邏輯資源更豐富。

6、FPGA和CPLD的組成:

FPGA基本有可編程I/O單元、基本可編程邏輯單元、嵌入式塊RAM、豐富的布線資源、底層嵌入功能單元和內嵌專用硬核等6部分組成。

CPLD的結構相對比較簡單,主要由可編程I/O單元、基本邏輯單元、布線池和其他輔助功能模塊組成。

7、Block RAM:

3種塊RAM結構,M512 RAM(512bit)、M4K RAM(4Kbit)、M-RAM(64Kbit)。

M512 RAM:適合做一些小的Buffer、FIFO、DPRAM、SPRAM、ROM等;

M4K RAM: 適用于一般的需求

M-RAM: 適合做大塊數據的緩沖區。

Xlinx 和 Lattice FPGA的LUT可以靈活配置成小的RAM、ROM、FIFO等存儲結構,這種技術被稱為分布式RAM。

補充:但是在一般的設計中,不提倡用FPGA/CPLD的片內資源配置成大量的存儲器,這是處于成本的考慮。所以盡量采用外接存儲器。

8、善用芯片內部的PLL或DLL資源完成時鐘的分頻、倍頻率、移相等操作,不僅簡化了設計,并且能有效地提高系統的精度和工作穩定性。

9、異步電路和同步時序電路的區別

異步電路:

電路核心邏輯有用組合電路實現;

異步時序電路的最大缺點是容易產生毛刺;

不利于器件移植;

不利于靜態時序分析(STA)、驗證設計時序性能。

同步時序電路:

電路核心邏輯是用各種觸發器實現;

電路主要信號、輸出信號等都是在某個時鐘沿驅動觸發器產生的;

同步時序電路可以很好的避免毛刺;

利于器件移植;

利于靜態時序分析(STA)、驗證設計時序性能。

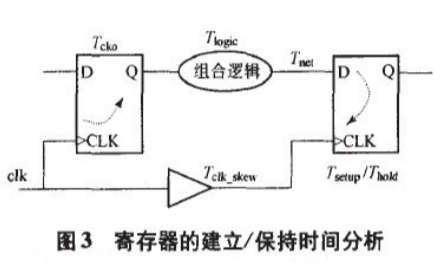

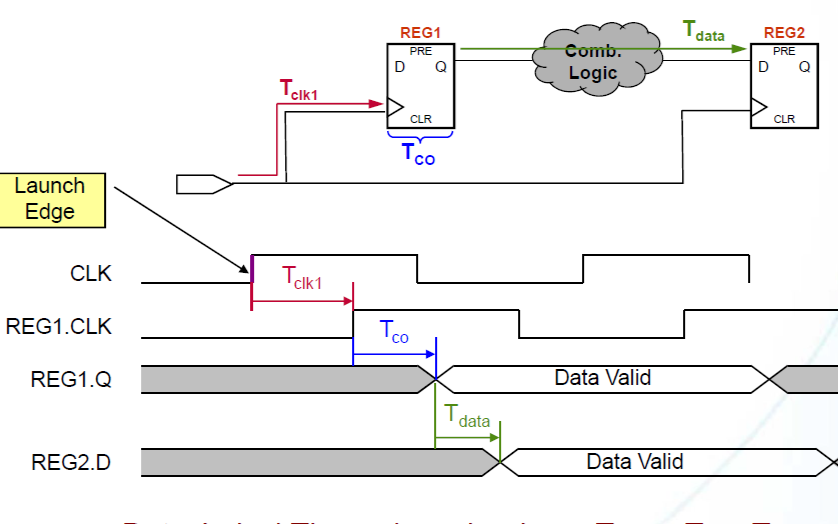

10、同步設計中,穩定可靠的數據采樣必須遵從以下兩個基本原則:

(1)在有效時鐘沿到達前,數據輸入至少已經穩定了采樣寄存器的Setup時間之久,這條原則簡稱滿足Setup時間原則;

(2)在有效時鐘沿到達后,數據輸入至少還將穩定保持采樣寄存器的Hold時鐘之久,這條原則簡稱滿足Hold時間原則。

11、同步時序設計注意事項:

異步時鐘域的數據轉換。

組合邏輯電路的設計方法。

同步時序電路的時鐘設計。

同步時序電路的延遲。同步時序電路的延遲最常用的設計方法是用分頻或者倍頻的時鐘或者同步計數器完成所需的延遲,對比較大的和特殊定時要求的延時,一般用高速時鐘產生一個計數器,根據計數產生延遲;對于比較小的延遲,可以用D觸發器打一下,這樣不僅可以使信號延時了一個時鐘周期,而且完成了信號與時鐘的初次同步。在輸入信號采樣和增加時序約束余量中使用。另外,還有用行為級方法描述延遲,如“#5 a《=4’0101;”這種常用于仿真測試激勵,但是在電路綜合時會被忽略,并不能起到延遲作用。

Verilog 定義的reg型,不一定綜合成寄存器。在Verilog代碼中最常用的兩種數據類型是wire和reg型,一般來說,wire型指定的數據和網線通過組合邏輯實現,而reg型指定的數據不一定就是用寄存器實現。

身處物聯網洪流的你還在等什么!“關注物聯網新機遇的你,怎能錯過這個饕餮盛宴!!由華強聚豐旗下電子發燒友網舉辦的第三屆“中國IoT大會”將 于12月2日在深圳隆重舉行:全球化的 視野、更高價值的獨家觀點、更專業的技術分享、更前沿的脈動把握,匯聚全球物聯網知名企業與精英的盛典,你不可錯過!更多信息歡迎大家繼續關注電子發燒友 網!”(點擊圖片查看詳情)

12、常用設計思想與技巧

(1)乒乓操作;

(2)串并轉換;

(3)流水線操作;

(4)異步時鐘域數據同步。是指如何在兩個時鐘不同步的數據域之間可靠地進行數據交換的問題。數據時鐘域不同步主要有兩種情況:

兩個域的時鐘頻率相同,但是相差不固定,或者相差固定但是不可測,簡稱為同頻異相問題。

兩個時鐘頻率根本不同,簡稱異頻問題。

兩種不推薦的異步時鐘域操作方法:一種是通過增加Buffer或者其他門延時來調整采樣;另一種是盲目使用時鐘正負沿調整數據采樣。

13、模塊劃分基本原則:

(1)對每個同步時序設計的子模塊的輸出使用寄存器(用寄存器分割同步時序模塊原則)。

(2)將相關邏輯和可以復用的邏輯劃分在同一模塊內(呼應系統原則)。

(3)將不同優化目標的邏輯分開。

(4)將送約束的邏輯歸到同一模塊。

(5)將存儲邏輯獨立劃分成模塊。

(6)合適的模塊規模。

(7)頂層模塊最好不進行邏輯設計。

14、組合邏輯的注意事項

(1)避免組合邏輯反饋環路(容易毛刺、振蕩、時序違規等)。

解決:

A、牢記任何反饋回路必須包含寄存器;

B、檢查綜合、實現報告的warning信息,發現反饋回路(combinational loops)后進行相應修改。

(2)替換延遲鏈。

解決:用倍頻、分頻或者同步計數器完成。

(3)替換異步脈沖產生單元(毛刺生成器)。

解決:用同步時序設計脈沖電路。

(4)慎用鎖存器。

解決:

A、使用完備的if…else語句;

B、檢查設計中是否含有組合邏輯反饋環路;

C、對每個輸入條件,設計輸出操作,對case語句設置default操作。特別是在狀態機設計中,最好有一個default的狀態轉移,而且每個狀態最好也有一個default的操作。

D、如果使用case語句時,特別是在設計狀態機時,盡量附加綜合約束屬性,綜合為完全條件case語句。

小技巧:仔細檢查綜合器的綜合報告,目前大多數的綜合器對所綜合出的latch都會報“warning”,通過綜合報告可以較為方便地找出無意中生成的latch。

15、時鐘設計的注意事項

(1)同步時序電路推薦的時鐘設計方法:

時鐘經全局時鐘輸入引腳輸入,通過FPGA內部專用的PLL或DLL進行分頻/倍頻、移相等調整與運算,然后經FPGA內部全局時鐘布線資源驅動到達芯片內所有寄存器和其他模塊的時鐘輸入端。

FPGA設計者的5項基本功:仿真、綜合、時序分析、調試、驗證。

對于FPGA設計者來說,練好這5項基本功,與用好相應的EDA工具是同一過程,對應關系如下:

1、仿真:Modelsim, Quartus II(Simulator Tool)

2、綜合:Quartus II (Compiler Tool, RTL Viewer, Technology Map Viewer, Chip Planner)

3、時序:Quartus II (TimeQuest Timing Analyzer, Technology Map Viewer, Chip Planner)

4、調試:Quartus II (SignalTap II Logic Analyzer, Virtual JTAG, Assignment Editor)

5、驗證:Modelsim, Quartus II(Test Bench Template Writer)

掌握HDL語言雖然不是FPGA設計的全部,但是HDL語言對FPGA設計的影響貫穿于整個FPGA設計流程中,與FPGA設計的5項基本功是相輔相成的。

對于FPGA設計者來說,用好“HDL語言的可綜合子集”可以完成FPGA設計50%的工作——設計編碼。

練好仿真、綜合、時序分析這3項基本功,對于學習“HDL語言的可綜合子集”有如下幫助:

1、通過仿真,可以觀察HDL語言在FPGA中的邏輯行為。

2、通過綜合,可以觀察HDL語言在FPGA中的物理實現形式。

3、通過時序分析,可以分析HDL語言在FPGA中的物理實現特性。

對于FPGA設計者來說,用好“HDL語言的驗證子集”,可以完成FPGA設計另外50%的工作——調試驗證。

1、搭建驗證環境,通過仿真的手段可以檢驗FPGA設計的正確性。

2、全面的仿真驗證可以減少FPGA硬件調試的工作量。

3、把硬件調試與仿真驗證方法結合起來,用調試解決仿真未驗證的問題,用仿真保證已經解決的問題不在調試中再現,可以建立一個回歸驗證流程,有助于FPGA設計項目的維護。

FPGA設計者的這5項基本功不是孤立的,必須結合使用,才能完成一個完整的FPGA設計流程。反過來說,通過完成一個完整的設計流程,才能最有效地練習這5項基本功。對這5項基本功有了初步認識,就可以逐個深入學習一些,然后把學到的知識再次用于完整的設計流程。如此反復,就可以逐步提高設計水平。采用這樣的循序漸進、螺旋式上升的方法,只要通過培訓入了門,就可以自學自練,自我提高。

市面上出售的有關FPGA設計的書籍為了保證結構的完整性,對FPGA設計的每一個方面分開介紹,每一方面雖然深入,但是由于缺少其他相關方面的支持,讀者很難付諸實踐,只有通讀完全書才能對FPGA設計獲得一個整體的認識。這樣的書籍,作為工程培訓指導書不行,可以作為某一個方面進階的參考書。

對于新入職的員工來說,他們往往對FPGA的整體設計流程有了初步認識,5項基本功的某幾個方面可能很扎實。但是由于某個或某幾個方面能力的欠缺,限制了他們獨自完成整個設計流程的能力。入職培訓的目的就是幫助他們掌握整體設計流程,培養自我獲取信息的能力,通過幾個設計流程來回的訓練,形成自我促進、自我發展的良性循環。在這一過程中,隨著對工作涉及的知識的廣度和深度的認識逐步清晰,新員工的自信心也會逐步增強,對個人的發展方向也會逐步明確,才能積極主動地參與到工程項目中來。

最后總結幾點:

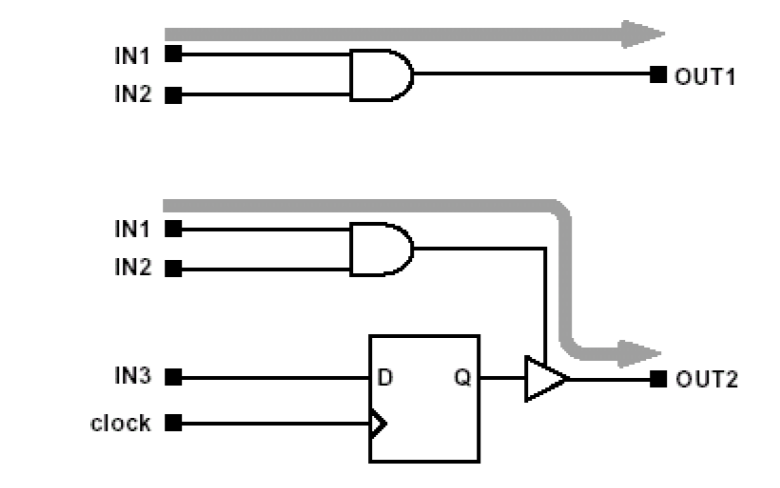

1)看代碼,建模型

只有在腦海中建立了一個個邏輯模型,理解FPGA內部邏輯結構實現的基礎,才能明白為什么寫Verilog和寫C整體思路是不一樣的,才能理解順序執行語言和并行執行語言的設計方法上的差異。在看到一段簡單程序的時候應該想到是什么樣的功能電路。

例如:

2)用數學思維來簡化設計邏輯

學習FPGA不僅邏輯思維很重要,好的數學思維也能讓你的設計化繁為簡,所以啊,那些看見高數就頭疼的童鞋需要重視一下這門課哦。舉個簡單的例子,比如有兩個32bit的數據X[31:0]與Y[31:0]相乘。當然,無論Altera還是Xilinx都有現成的乘法器IP核可以調用,這也是最簡單的方法,但是兩個32bit的乘法器將耗費大量的資源。那么有沒有節省資源,又不太復雜的方式來實現呢?我們可以稍做修改:

將X[31:0]拆成兩部分X1[15:0]和X2[15:0],令X1[15:0]=X[31:16],X2[15:0]=X[15:0],則X1左移 16位后與X2相加可以得到X;同樣將Y[31:0]拆成兩部分Y1[15:0]和Y2[15:0],令 Y1[15:0]=Y[31:16],Y2[15:0]=Y[15:0],則Y1左移16位后與Y2相加可以得到Y;則X與Y的相乘可以轉化為X1和X2 分別與Y1和Y2相乘,這樣一個32bit*32bit的乘法運算轉換成了四個16bit*16bit的乘法運算和三個32bit的加法運算。轉換后的占用資源將會減少很多,有興趣的童鞋,不妨綜合一下看看,看看兩者差多少。

3)時鐘與觸發器的關系

“時鐘是時序電路的控制者”這句話太經典了,可以說是FPGA設計的圣言。FPGA的設計主要是以時序電路為主,因為組合邏輯電路再怎么復雜也變不出太多花樣,理解起來也不沒太多困難。但是時序電路就不同了,它的所有動作都是在時鐘一拍一拍的節奏下轉變觸發,可以說時鐘就是整個電路的控制者,控制不好,電路功能就會混亂。

打個比方,時鐘就相當于人體的心臟,它每一次的跳動就是觸發一個 CLK,向身體的各個器官供血,維持著機體的正常運作,每一個器官體統正常工作少不了組織細胞的構成,那么觸發器就可以比作基本單元組織細胞。時序邏輯電路的時鐘是控制時序邏輯電路狀態轉換的“發動機”,沒有它時序邏輯電路就不能正常工作,因為時序邏輯電路主要是利用觸發器存儲電路的狀態,而觸發器狀態變換需要時鐘的上升或下降沿!由此可見時鐘在時序電路中的核心作用!

最后簡單說一下體會吧,歸結起來就多實踐、多思考、多問。實踐出真知,看100遍別人的方案不如自己去實踐一下。實踐的動力一方面來自興趣,一方面來自壓力,我個人覺得后者更重要。有需求會容易形成壓力,也就是說最好能在實際的項目開發中鍛煉,而不是為了學習而學習。在實踐的過程中要多思考,多想想問題出現的原因,問題解決后要多問幾個為什么,這也是經驗積累的過程,如果有寫項目日志的習慣更好,把問題及原因、解決的辦法都寫進去。最后還要多問,遇到問題思索后還得不到解決就要問了,畢竟個人的力量是有限的,問同學同事、問搜索引擎、問網友都可以,一篇文章、朋友們的點撥都可能幫助自己快速解決問題。

-

FPGA設計

+關注

關注

9文章

428瀏覽量

26484 -

靜態時序分析

+關注

關注

0文章

28瀏覽量

9572 -

同步時序設計

+關注

關注

0文章

1瀏覽量

1135

原文標題:十年開發工程師談該如何學習FPGA?

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

同步電路設計中靜態時序分析的時序約束和時序路徑

靜態時序分析在高速 FPGA設計中的應用

靜態時序分析:如何編寫有效地時序約束(一)

FPGA進行靜態時序分析

同步時序設計靜態時序分析等fpga設計技巧剖析

同步時序設計靜態時序分析等fpga設計技巧剖析

評論