共讀好書

芯片制造是當今世界最為復雜的工藝過程。這是一個由眾多頂尖企業共同完成的一個復雜過程。本文努力將這一工藝過程做一個匯總,對這個復雜的過程有一個全面而概括的描述。

半導體制造工藝過程非常多,據說有幾百甚至幾千個步驟。這不是夸張的說法,一個百億投資的工廠做的可能也只是其中的一小部分工藝過程。對于這么復雜的工藝,本文將分成五個大類進行解說:晶圓制造、光刻蝕刻、離子注入、薄膜沉積、封裝測試。

晶圓制造(Wafer Manufacturing)又可分為以下5 個主要過程:

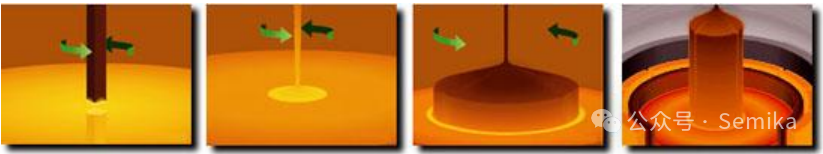

(1)拉晶Crystal Pulling

?

摻雜多晶硅在1400度熔煉?注入高純氬氣的惰性氣體

?將單晶硅“種子”放入熔體中,并在“拔出”時緩慢旋轉。

?

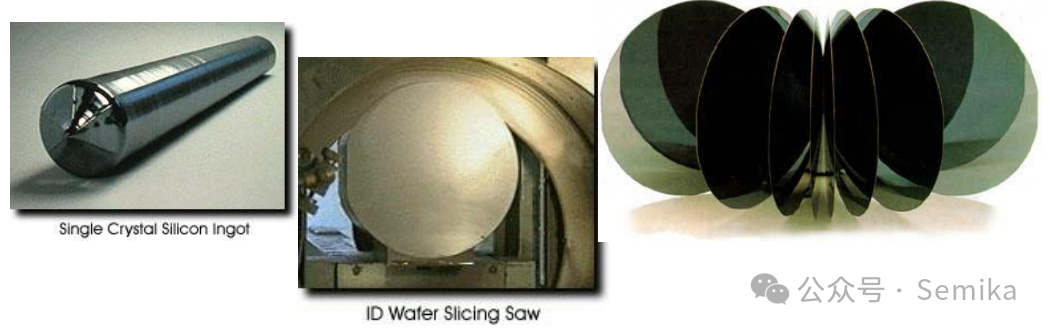

單晶錠直徑由溫度和提取速度決定(2)晶圓切片 (Wafer slicing)

用精密的“鋸(Saw)”將硅錠切成獨立的晶圓。

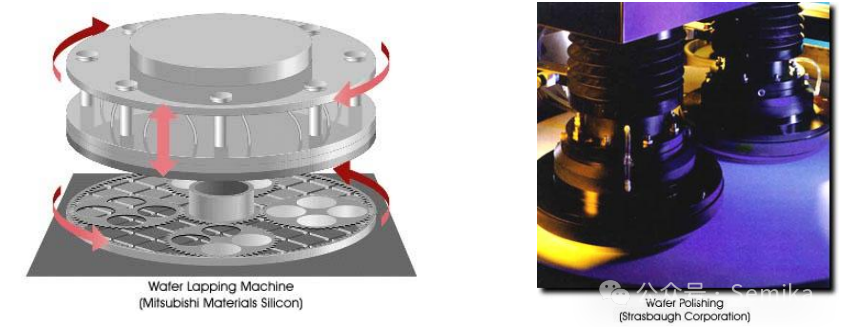

(3)晶圓研磨、侵蝕(Wafer lapping,etching)

? 切片的晶圓片使用旋轉研磨機和氧化鋁漿料進行機械研磨,使晶圓片表面平整、平行,減少機械缺陷。

?然后在氮化酸/乙酸溶液中蝕刻晶圓,以去除微觀裂紋或表面損傷,然后進行一系列高純度RO/DI水浴。

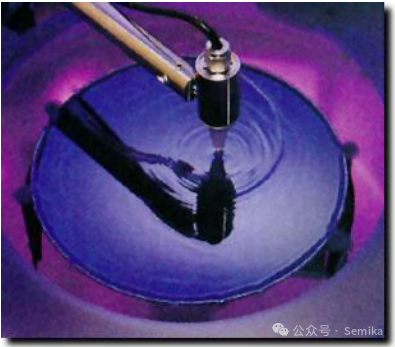

(4) 硅片拋光、清洗 (Wafer polishing and Cleaning)

?接下來,晶圓在一系列化學和機械拋光過程中拋光,稱為CMP(Chemical Mechanical Polish)。

?拋光過程通常包括兩到三個拋光步驟,使用越來越細的漿液和使用RO/DI水的中間清洗。

?使用SC1溶液(氨,過氧化氫和RO/DI水)進行最終清洗,以去除有機雜質和顆粒。然后,用HF除去天然氧化物和金屬雜質,最后SC2溶液使超干凈的新的天然氧化物在表面生長。

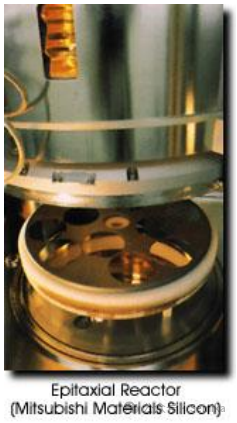

(5)晶片外延加工 (Wafer epitaxial processing)

?外延工藝(EPI)被用來在高溫下從蒸汽生長一層單晶硅到單晶硅襯底上。

?氣相生長單晶硅層的工藝被稱為氣相外延(VPE)。

SiCl4 + 2H2Si + 4HCl

該反應是可逆的,即如果加入HCl,硅就會從晶圓片表面蝕刻出來。

另一個生成Si的反應是不可逆的:

SiH4→Si + 2H2(硅烷)

? EPI生長的目的是在襯底上形成具有不同(通常較低)濃度的電活性摻雜劑的層。例如,p型晶圓片上的N型層。

?約為晶圓片厚度的3%。

?對后續晶體管結構無污染。

半導體制造工藝 - 光刻 (Photolithography)

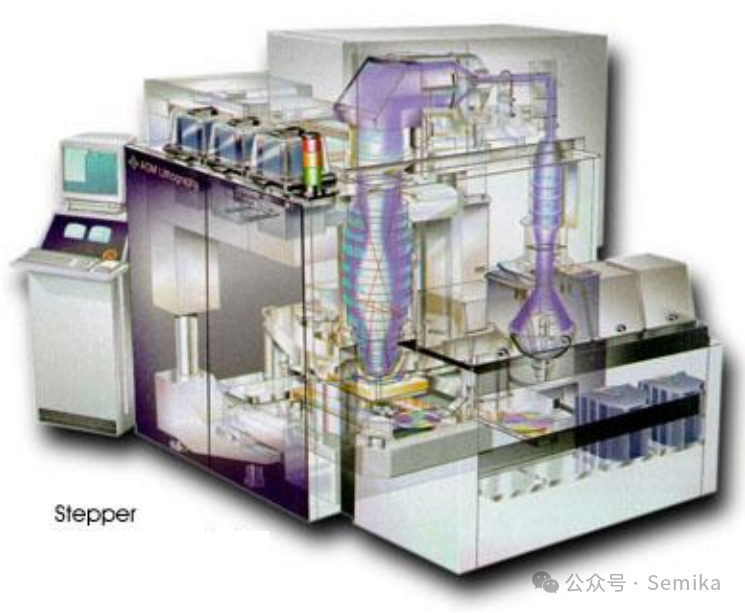

近年大量提及的光刻機,只是眾多工藝設備中的一個。即使是光刻,也有很多的工藝過程和設備。

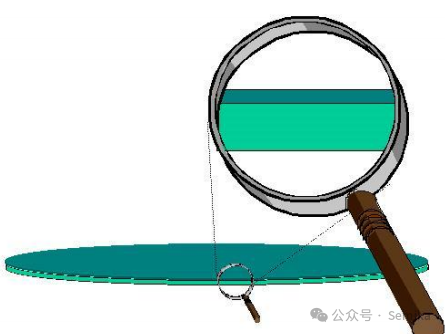

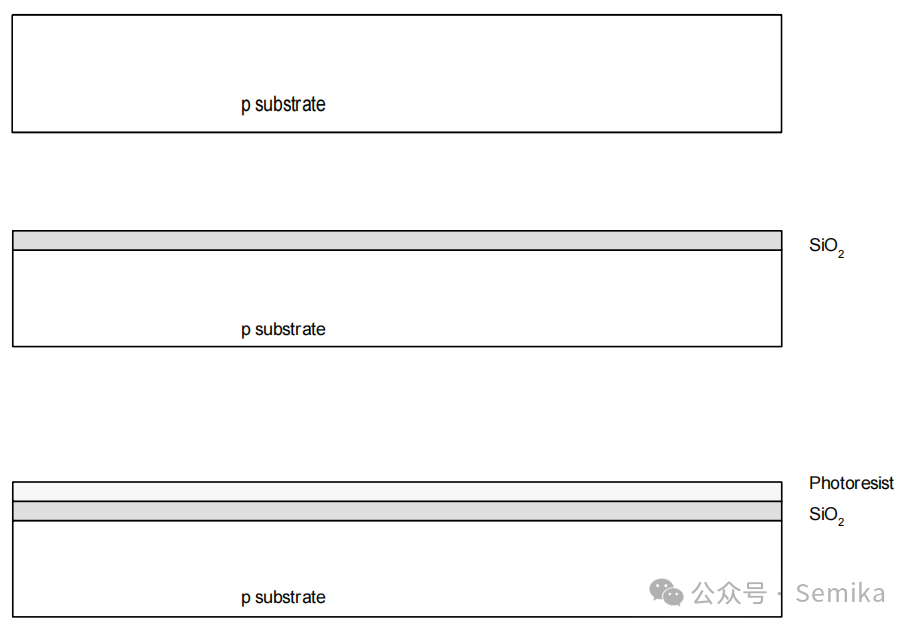

(1)光刻膠涂層Photoresist coating

光刻膠是一種光敏材料。將少量光刻膠液體加在晶圓片上。晶圓片在1000到5000 RPM的速度下旋轉,將光刻膠擴散成2到200um厚的均勻涂層。

光刻膠有兩種類型:負膠和正膠。

正膠:暴露于光下可以分解復雜的分子結構,使其易于溶解。

負膠:曝光使分子結構變得更復雜,更難以溶解。

每個光刻步驟所涉及的步驟如下

?清潔晶圓片

?沉積屏障層SiO2,Si3N4,金屬

?涂上光刻膠

?軟烤

?對齊蒙版

?圖形曝光

?顯影

?烘焙

?蝕刻

?去除光刻膠

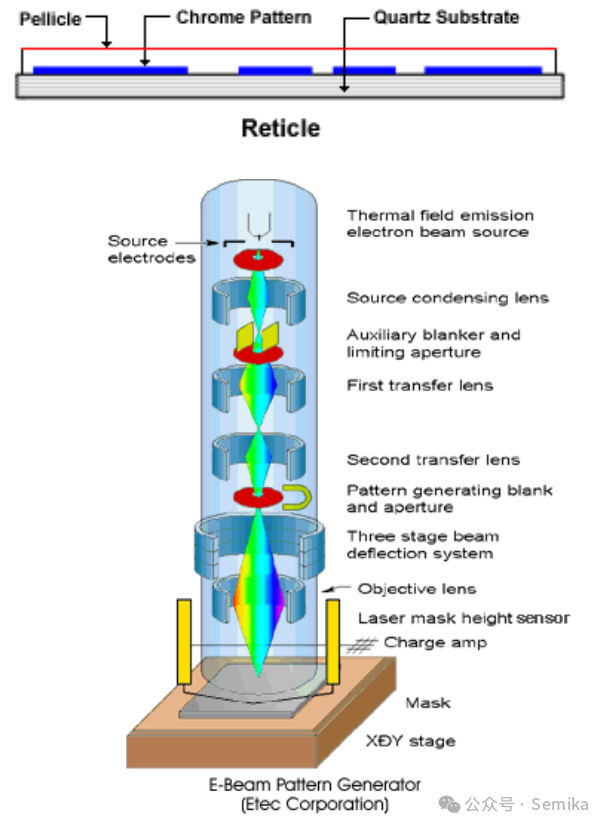

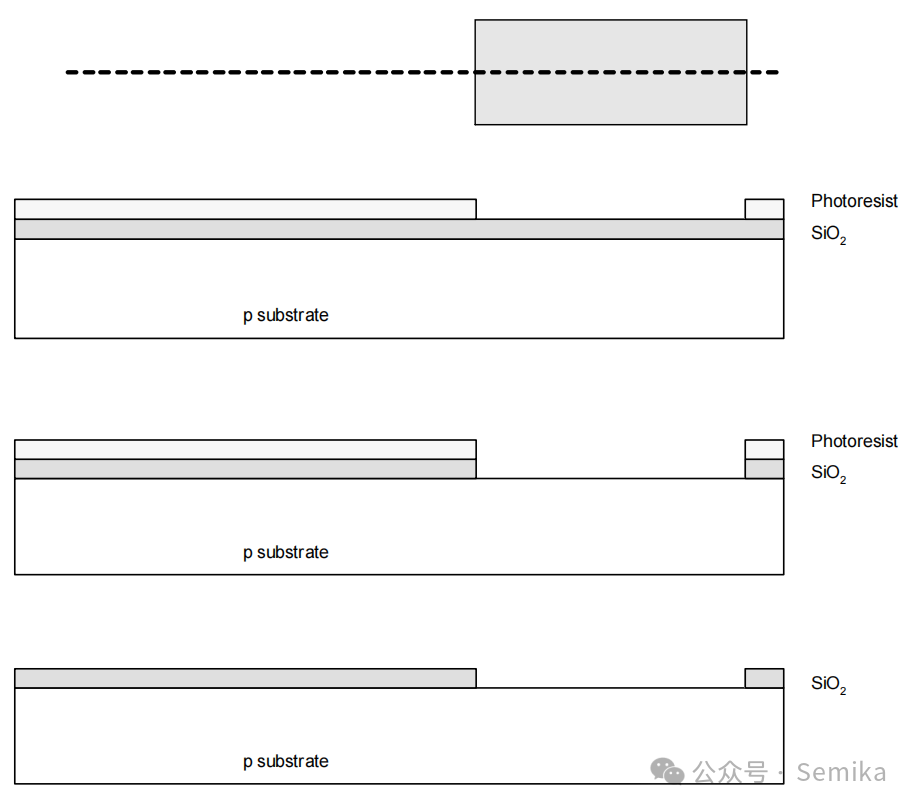

(2)圖案準備Pattern Preparation

IC設計人員使用CAD軟件設計每層的圖案。然后使用激光圖案發生器或電子束將圖案轉移到具有圖案的光學透明石英襯底(模板)上。

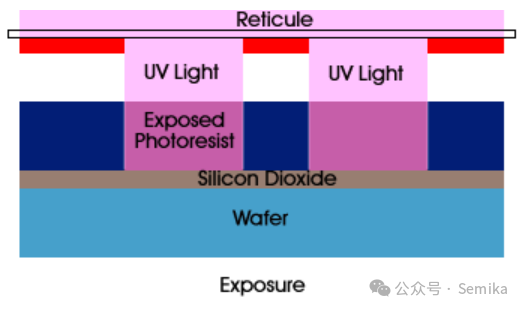

(3)圖案轉移(曝光)

這里使用光刻機,將圖案從模板上,投影復制到芯片層板上。

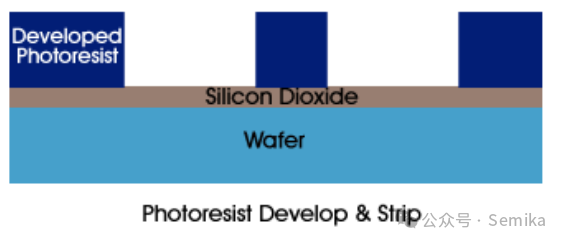

(4)顯影、烘烤

?曝光后,晶圓片在酸溶液或堿溶液中顯影,以去除光刻膠的暴露區域。

?一旦除去暴露的光刻膠,晶圓片將在低溫下“烘烤”以硬化剩余的光刻膠。

半導體制造工藝 - 蝕刻和離子注入 (Etching and Ion Implantation)

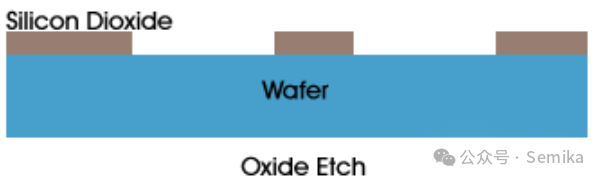

(1)濕式和干式蝕刻

?在大型濕平臺上進行化學蝕刻。

?不同類型的酸,堿和苛性堿溶液用于去除不同材料的選定區域。

? BOE,或緩沖氧化物蝕刻劑,由氟化銨緩沖的氫氟酸制備,用于去除二氧化硅,而不會蝕刻掉底層的硅或多晶硅層。

?磷酸用于蝕刻氮化硅層。

?硝酸用來蝕刻金屬。

?用硫酸去除光刻膠。

?對于干式蝕刻,晶圓片被放置在蝕刻室中,通過等離子體進行蝕刻。

?人員安全是首要問題。

?許多晶圓廠使用自動化設備執行蝕刻過程。

(2)抗蝕劑剝離

然后光刻膠完全從晶圓上剝離,在晶圓上留下氧化物圖案。

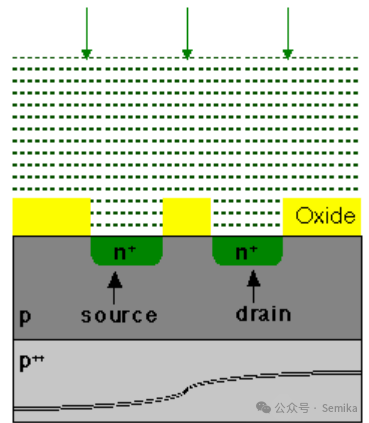

(3)離子注入

?離子注入改變晶圓片上現有層內精確區域的電特性。

?離子注入器使用高電流加速器管和轉向聚焦磁鐵,用特定摻雜劑的離子轟擊晶圓表面。

?當摻雜化學物質沉積在表面并擴散到表面時,氧化物充當屏障。

?將硅表面加熱到900℃來進行退火,注入的摻雜離子進一步擴散到硅片中。

半導體制造工藝 - 薄膜沉積 (Thin Film Deposition)

薄膜沉積的方式和內容也比較多,下面逐個說明:

(1)氧化硅

當硅在氧氣中存在時,SiO2會熱生長。氧氣來自氧氣或水蒸氣。環境溫度要求為900 ~ 1200℃。發生的化學反應是

Si + O2→SiO2

Si +2H2O —> SiO2 + 2H2

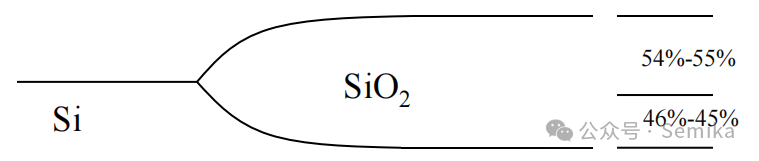

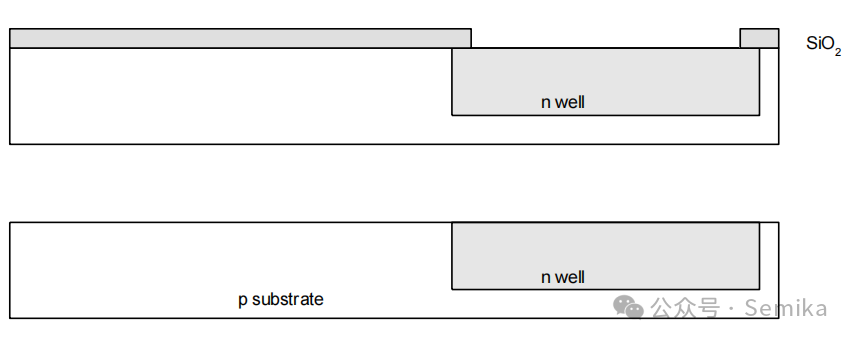

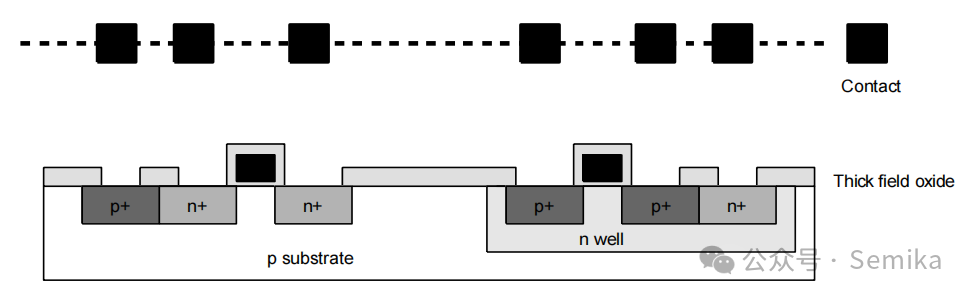

選擇性氧化后的硅片表面如下圖所示:

氧氣和水都會通過現有的SiO2擴散,并與Si結合形成額外的SiO2。水(蒸汽)比氧氣更容易擴散,因此蒸汽的生長速度要快得多。

氧化物用于提供絕緣和鈍化層,形成晶體管柵極。干氧用于形成柵極和薄氧化層。蒸汽被用來形成厚厚的氧化層。絕緣氧化層通常在1500nm左右,柵極層通常在200nm到500nm間。

(2)化學氣相沉積Chemical Vapor Deposition

化學氣相沉積(CVD)通過熱分解和/或氣體化合物的反應在襯底表面形成薄膜。

CVD反應器有三種基本類型:

?大氣化學氣相沉積

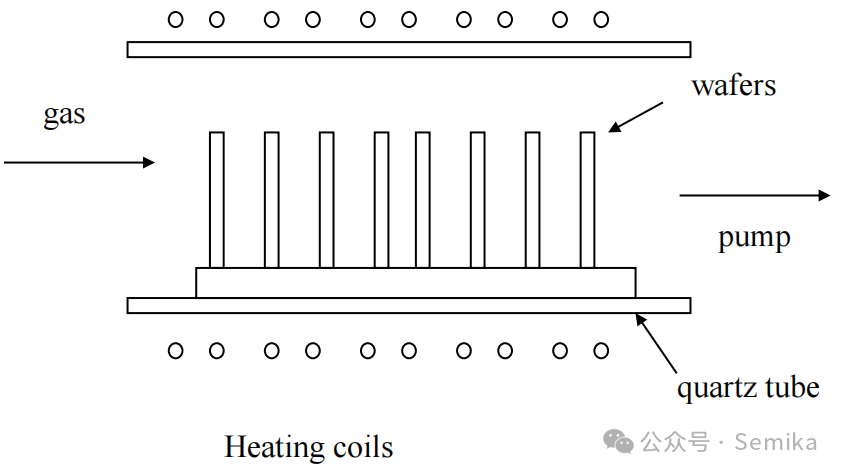

?低壓CVD (LPCVD)

?等離子增強CVD (PECVD)

低壓CVD工藝示意圖如下圖所示。

CVD的主要有下面幾種反應過程

i). 多晶硅 Polysilicon

SiH4 —> Si + 2H2(600℃)

沉積速度 100 - 200 nm/min

可添加磷(磷化氫)、硼(二硼烷)或砷氣體。多晶硅也可以在沉積后用擴散氣體摻雜。

ii). 二氧化硅Dioxide

SiH4 + O2→SiO2 + 2H2 (300 - 500℃)

SiO2用作絕緣體或鈍化層。通常添加磷是為了獲得更好的電子流動性能。

iii). 氮化硅 Siicon Nitride

3SiH4 + 4NH3 —> Si3N4 + 12H2

(硅烷) (氨) (氮化物)

(3)濺射

目標被高能離子如Ar+轟擊,目標中的原子將被移動并輸送到基材上。

金屬如鋁、鈦可以用作靶材。

(4)蒸鍍

Al或Au(金)被加熱到蒸發點,蒸汽將凝結并形成覆蓋晶圓片表面的薄膜。

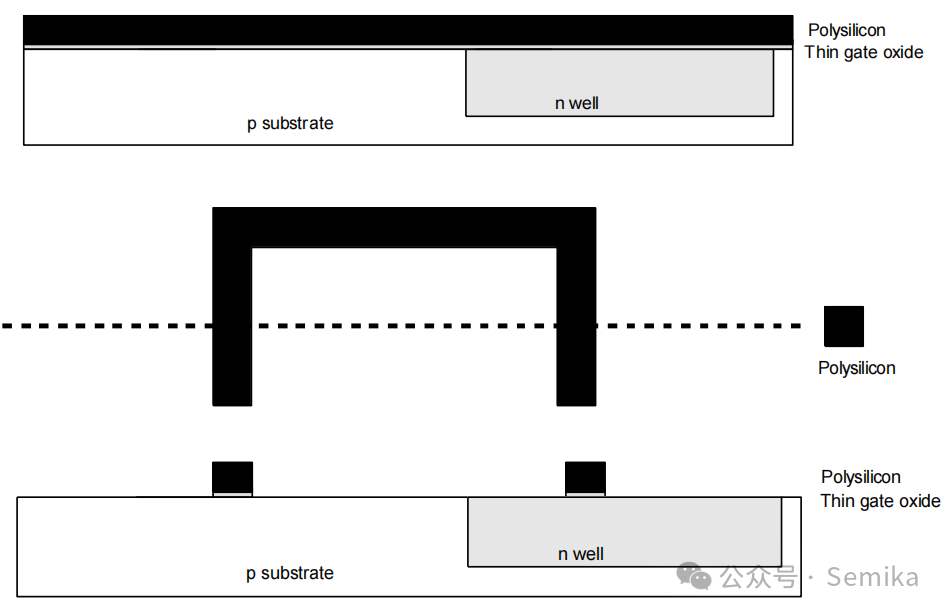

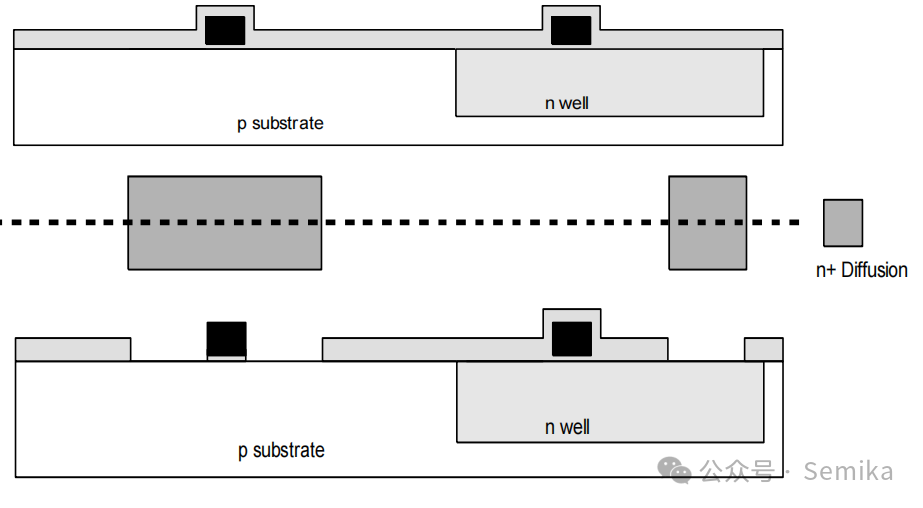

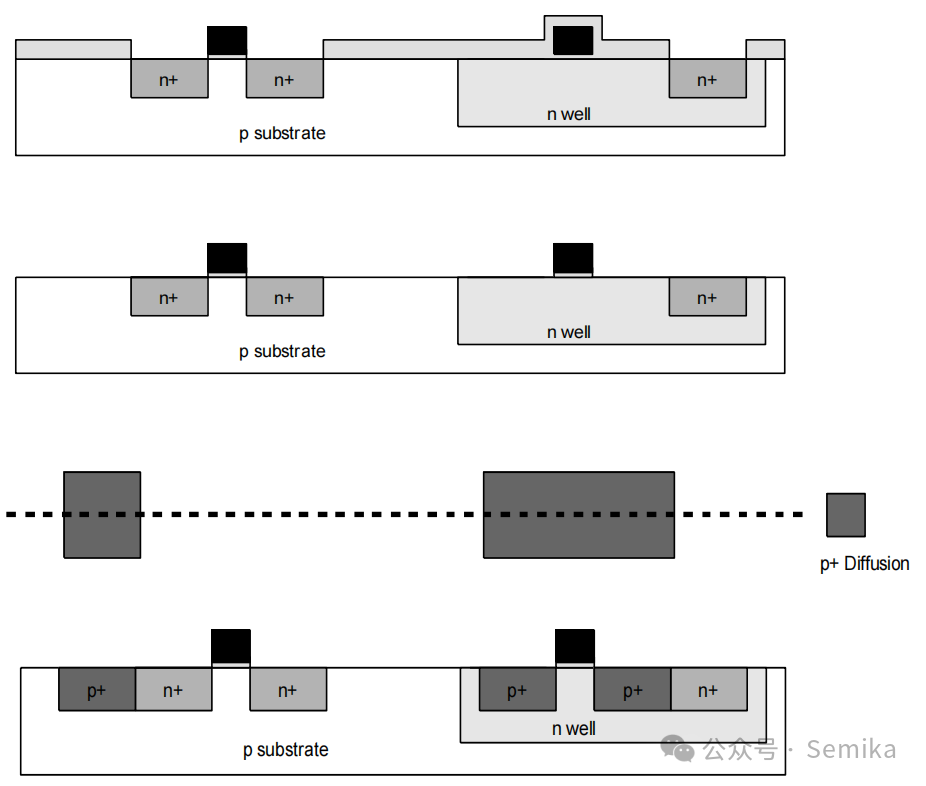

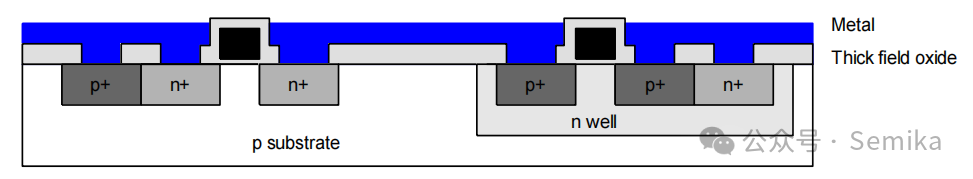

下面用一個案例,來詳細說明一下光刻、蝕刻,到離子沉積的過程中,硅片上的電路是如何一步步成型的:

半導體制造工藝 - 封裝測試 (Post-processing)

(1)晶圓測試Probe Test

在最終線路制備完成后,使用自動化探針測試方法測試晶圓上測試器件,剔除不良品。

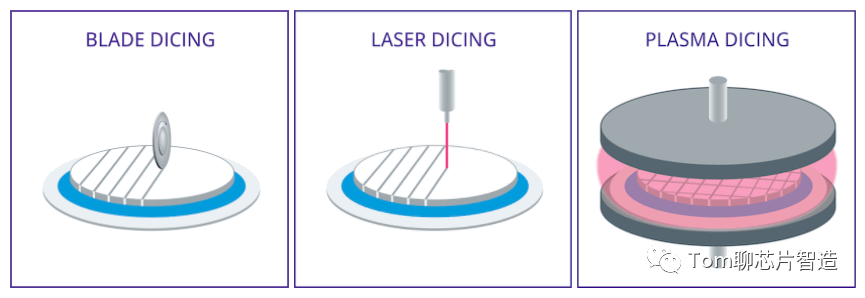

(2) 晶圓切割Wafer Dicing

探針測試后,晶圓片被切成單個的芯片。

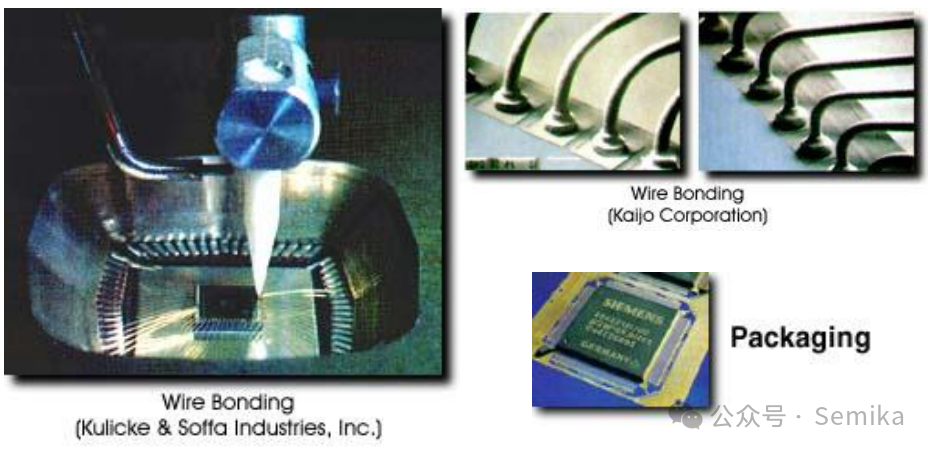

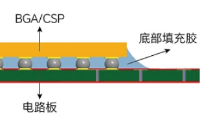

(3) 接線、封裝

?單個芯片連接到引線框架,鋁或金引線通過熱壓縮或超聲波焊接連接。

?通過將設備密封到陶瓷或塑料包裝中來完成包裝。

?多數芯片還需要經過最后的功能測試,才會送到下游用戶手上。

微電子封裝切割熔錫失效分析及對策

方欣

摘要:

熔錫是微電子封裝QFN(Quad Flat No-leads Package,方形扁平無引腳封裝)產品在切割生產過程中的核心質量不良,是導致產品可焊性失效的關鍵風險點。本文針對QFN封裝產品的切割生產過程進行熔錫失效的原因分析和對策探討。

0引言

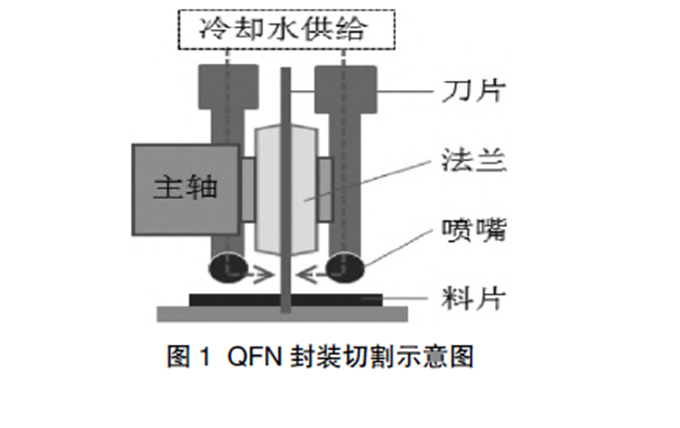

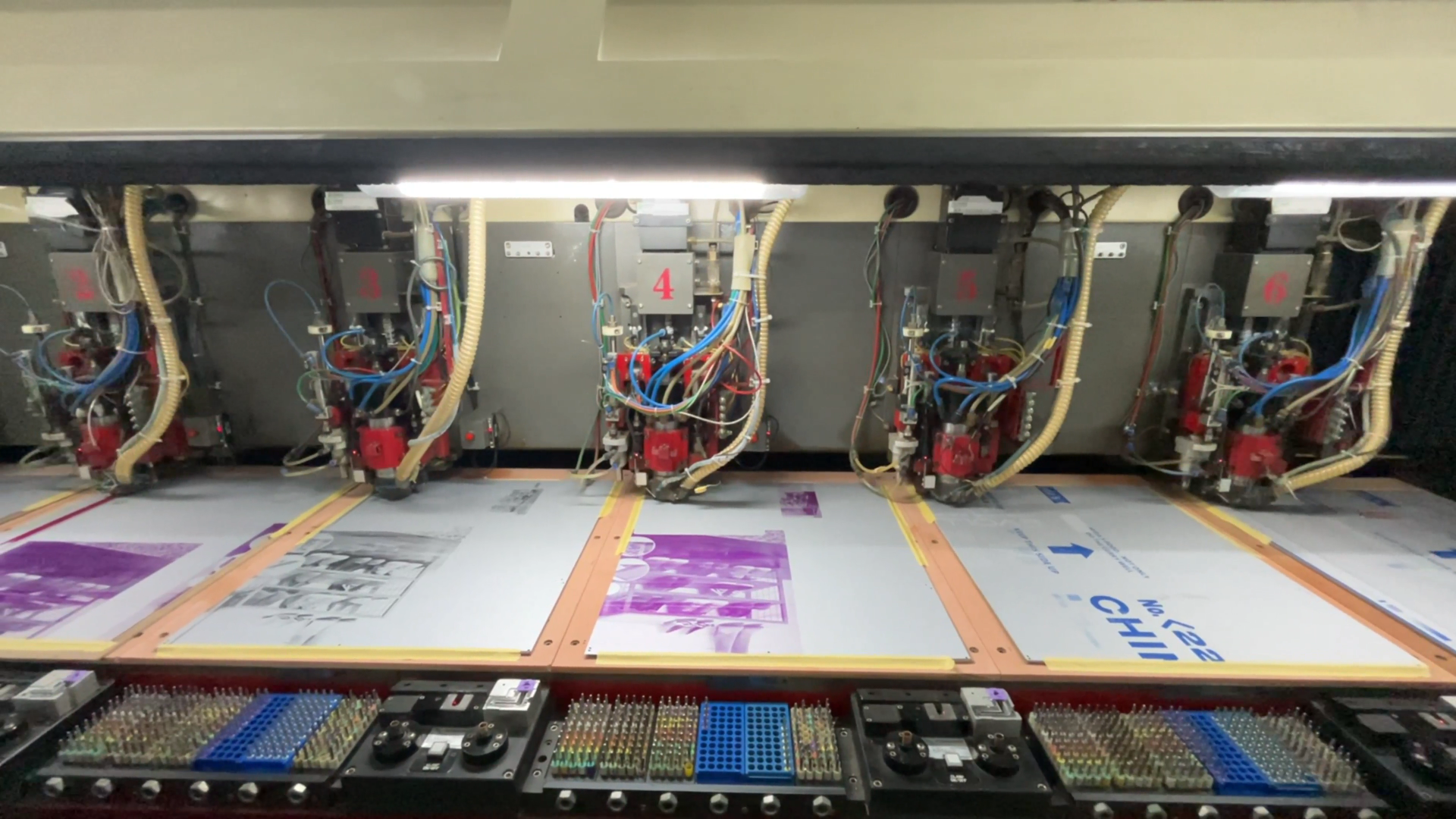

QFN封裝切割的工藝特點是通過高速旋轉的切割刀片將整條料片切割分離成單顆的產品。在切割生產過程中,刀片和產品本身容易受到切削高溫的影響,使產品引腳表面的錫層發生異常熔化,這一現象通常稱為切割熔錫。由于熔錫不良會導致產品可焊性失效,這在微電子封裝生產過程中屬于嚴重的質量不良。因此,解決QFN產品的切割熔錫問題顯得非常重要,本文著重分析微電子QFN封裝產品在切割過程中的熔錫成因和探討其控制方法。

1切割熔錫的成因

1.1 QFN切割工藝簡述

通常,QFN產品在封裝后道的工藝流程如下:

塑封→電鍍→后烘→打印→切割

其中,QFN封裝產品切割工藝如圖1所示,整條料片通過刀片旋轉切割分離成單顆的產品。切割移動過程中,刀片表面和產品表面錫層同時采用冷卻水進行噴射降溫處理,以降低刀片和產品所產生的切削高溫,避免產品造成切割熔錫等質量不良。

1.2切割熔錫失效的成因及特征

(1)當傳遞到產品切割面的切削溫度高于純錫的熔點溫度232℃時,QFN封裝產品切割面的引腳則有熔錫的風險;

(2)當傳遞到產品切割面的切削溫度低于純錫的熔點溫度232℃時,QFN封裝產品切割面的引腳則沒有熔錫的風險。

根據成因分析可知,切割熔錫失效主要是由于切割刀片傳遞到產品引腳表面錫層的溫度超過了純錫的熔點。根據熔錫位置不同,QFN封裝產品切割熔錫失效有兩種特征:

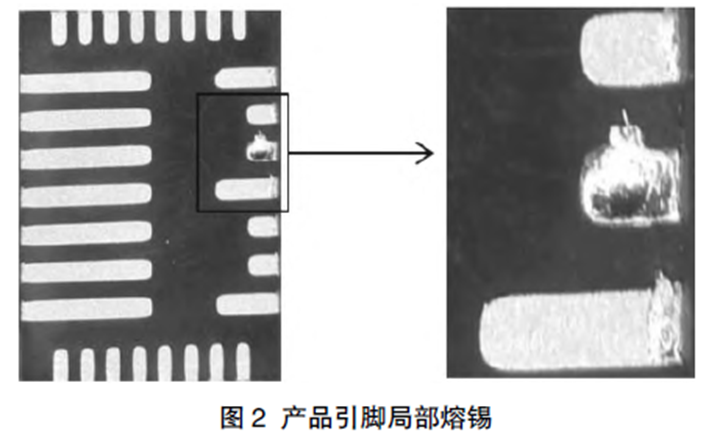

如圖2,產品引腳錫層產生局部的熔錫失效:

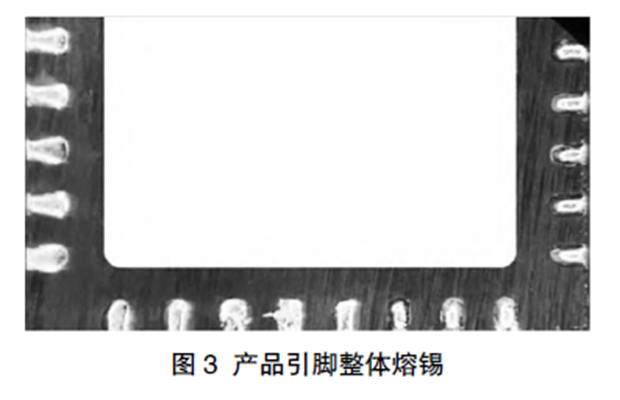

如圖3,產品引腳錫層產生整體的熔錫失效:

1.3熔錫失效的不良后果

在QFN封裝產品從整條料片切割成單顆產品的生產過程中,當切削所釋放出來的溫度高于產品錫層熔點時,產品引腳表面的錫層會產生熔化。這樣會造成引腳錫層脫落、銅層裸露氧化的現象,使產品在PCB板、電路板等焊接應用的過程中,產生引腳虛焊、脫焊、短路等可焊性失效的質量異常。

綜上所述,切割熔錫失效將直接造成產品可焊性失效的問題,這在電子元器件生產應用中是重要的質量隱患。因此,控制切割熔錫是微電子QFN封裝生產的一個關鍵點,我們從切割工藝設計和設備應用的角度來實驗分析,針對影響切割熔錫的風險因素進行相應的對策探討。

2切割熔錫的風險點分析

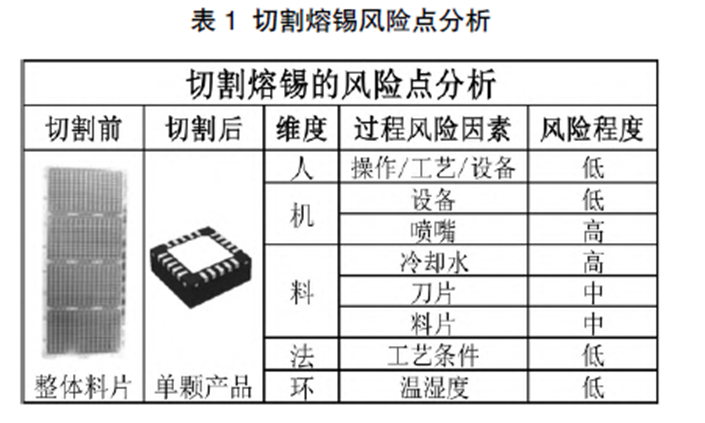

如表1所示,通過人、機、料、法、環五個維度來分析整體料片切割成單顆產品的過程,識別出QFN封裝切割過程中的熔錫風險點。

從分析可知,切割熔錫的過程風險因素中,人員方面、設備本身、生產工藝方法、生產環境所造成產品切割熔錫的風險低,基本不會產生切割熔錫的問題。料片、切割刀片產生切割熔錫的風險中等,在其選型方面,應遵循料片和刀片材料在常規的切割工藝條件下,本身不會造成切割熔錫這一原則。而設備噴嘴、供給冷卻水直接作用于料片和刀片的表面,是切割熔錫的高風險因素,也是解決和控制切削高溫造成切割熔錫的關鍵點。我們著重對噴嘴和冷卻水這兩個因素進行分析和探討。

3冷卻水的影響

3.1冷卻水的溫度過高

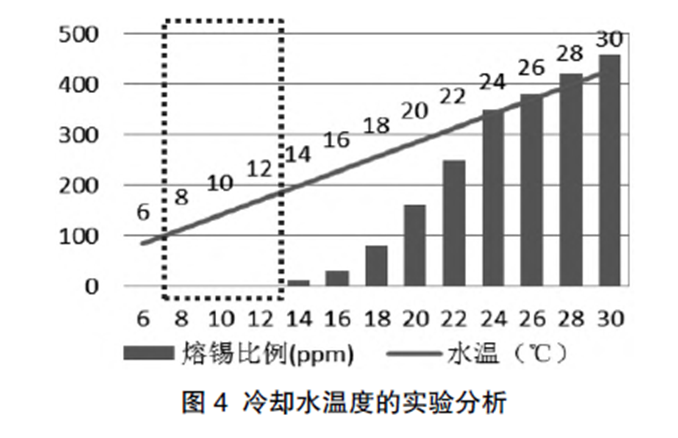

冷卻水溫度是影響切割熔錫失效的關鍵因素,在產品切割過程中,控制切割冷卻水的溫度至關重要。如圖4所示,為冷卻水溫度對產品熔錫的影響趨勢分析。由批量生產驗證數據得知,隨著冷卻水溫度的升高,產品熔錫的風險比例越高,熔錫數量也逐步增加;而水溫越低,產品熔錫的風險越小,熔錫的比例越少。結合廠務動力成本和產品品質來綜合考慮,切割冷卻水的輸出溫度控制在10±2℃,能夠有效降低切割熔錫的風險,且較為經濟合理。

3.2冷卻水的流量過小

3.2.1冷卻水流量的區間控制

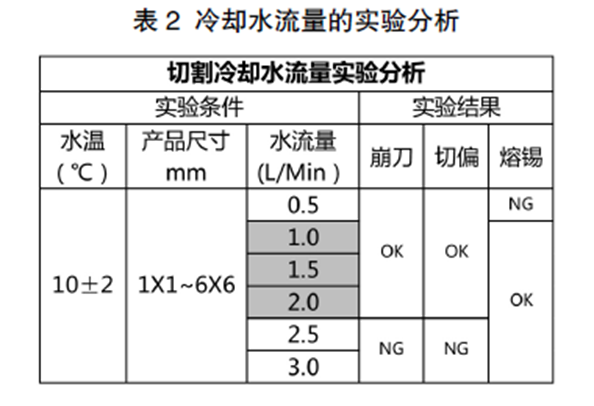

如表2所示,在水溫條件穩定的情況下,采用大小不同的水流量進行產品切割實驗分析。從數據分析可以看出,異常的水流量大小,會產生刀片崩刀、切割偏移、切割熔錫等質量不良。當切割冷卻水流量過小時,切割刀片所產生的高溫不能及時降低而傳遞到產品引腳的錫層面,導致切割熔錫的問題。理論上,切割冷卻水流量越大其冷卻效果越好,在實際應用過程中,應綜合考慮如水流量過大容易造成刀片崩刀、產品位移切偏等不良因素。從實驗結果可知,切割冷卻水流量控制在1.0-2.0L/Min這一區間相對穩定可靠。

3.2.2冷卻水流量的穩定性控制

如上述分析可知,噴嘴出水流量的大小會影響到切割熔錫失效的比例,因此冷卻水流量輸出的穩定性也是非常關鍵的一個控制點。在實際應用過程中,水流量穩定性控制可從動力供給和設備裝置兩方面來考慮。動力供給方面,可優先選用潔凈度等級高于普通自來水的純水,并在設備冷卻水的進水口安裝過濾器裝置來提高冷卻水水質的穩定性。而設備裝置方面,可采用電子流量計控制的設計方式來輸出冷卻噴射水的水流量,通過設定輸出目標值,自動監測和自動識別補償實際出水供給的水流量大小。相比較傳統的機械流量計而言,電子流量計能夠自動調節控制,自動修復水流波動、管路堵塞等供給不穩定的因素,可提前預防水流量異常的問題,提升冷卻系統的穩定性。

4噴嘴的影響

噴嘴是切割冷卻水的傳輸裝置,它將切割冷卻水均勻地噴射到刀片和產品的表面,使刀片和產品在切割過程中的有限空間實現快速降溫。針對噴嘴的設計應用,應從噴嘴冷卻的均勻性、噴射的覆蓋面積、排屑的有效性這三個方面來考慮,以避免產品切割熔錫的風險。

4.1噴嘴的功能結構設計

實際應用中,刀片兩側的刃口通常需要實現瞬間降溫,以滿足各種QFN產品尺寸、材料類別的加工需求。特別是在切割有特殊工藝要求、熔錫敏感的產品時,提升刀片和產品的冷卻效果尤為重要。

如圖5所示,在A點部位設計90°垂直于刀片表面的噴嘴裝置,可提升噴嘴傳輸冷卻水的有效性,使冷卻水有效地作用于刀片,起到良好的刀片冷卻效果。同時,還可在B點部位設計帶有60°扇形角度的產品噴嘴裝置,這樣能夠對產品的引腳表面及切割槽深度同步進行噴射冷卻。這樣的設計方式提高了產品切割的排屑能力,且大幅度提升了設備冷卻系統的兼容能力,降低了切割熔錫的風險。

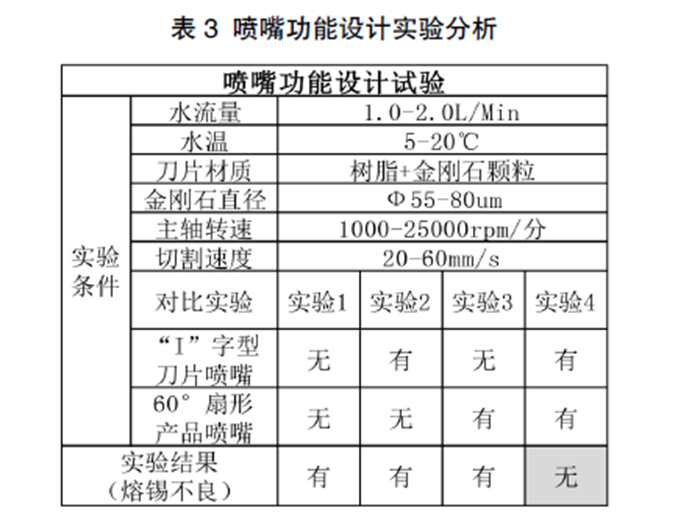

如表3所示,從噴嘴功能設計實驗分析的結果可以看出:實驗4,在A部位的刀片區域、B部位的產品切割區域采用雙路冷卻水噴嘴裝置的設計,其降溫冷卻效果明顯,質量控制最為穩定,產品沒有切割熔錫不良的問題。而實驗1、2、3,不采用冷卻噴嘴裝置或采用單一的噴嘴功能設計,產品的冷卻效果均存在一定的局限性,在切割特定產品或特殊工藝條件下,均有切割熔錫的質量不良。

從實驗結果得知,設備噴嘴采用雙路冷卻的功能設計,能夠提升切割不同產品的兼容能力,提升切割效率,減少切割熔錫失效的風險。

4.2噴嘴口的形狀設計

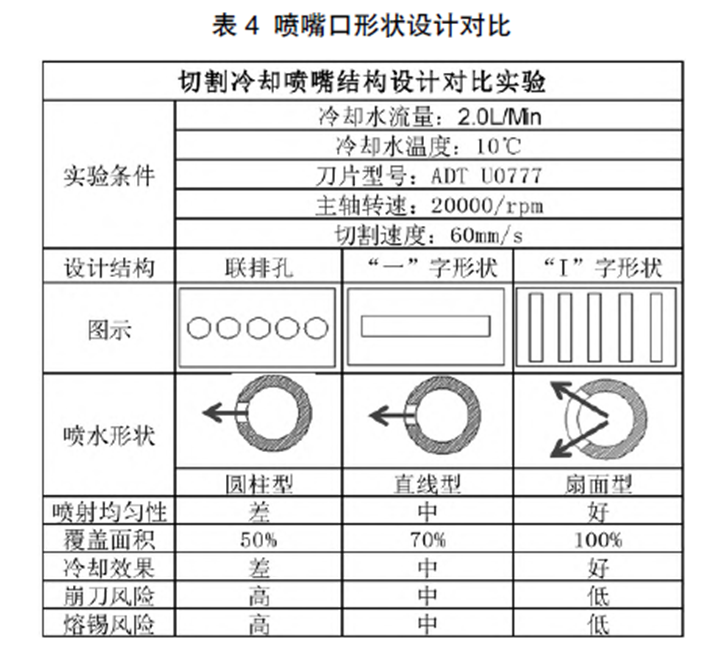

噴嘴的噴射口采用不同的形狀設計,其作用效果有很大差別。如表4所示,切割冷卻噴嘴的噴射口采用3種不同的形狀設計,其冷卻效果和熔錫風險明顯不同。具體如下:

1、采用聯排孔形狀的設計方式,噴射出水為圓柱形狀。該形狀設計的噴水集中作用于刀片局部的固定區域,刀片局部面積受到水壓的沖擊力較大。在實際應用中,其崩刀風險高,且噴射覆蓋的面積小,整體的冷卻效果差,熔錫的風險高。

2、采用“一”字形狀的設計,噴射出水為直線形狀。整體的冷卻效果比聯排孔設計好,噴射覆蓋面積、崩刀和熔錫風險有明顯的改善。

3、采用“I”字形狀的設計,噴射出水為扇面形狀。該結構形狀設計的噴嘴呈扇形霧狀的形態噴射,因此降低了水壓對于產品和刀片的沖擊力,減少了切偏和崩刀的風險。同時,出水呈扇面形狀噴射,其噴射覆蓋面積廣,能夠將冷卻水有效地噴射到刀片和產品所需降溫的全部區域,這樣就大幅度地提升了冷卻效果,產品熔錫風險則明顯降低。

通過實驗對比,刀片冷卻噴嘴采用“I”字形狀的結構設計,其實用性最好。應用到實際生產中,能夠有效降低切割熔錫等質量隱患,從而提升QFN封裝切割的穩定性。

5切割熔錫失效的管控

針對切割熔錫的控制,可以從廠務動力供給布局、產品工藝流程管控、設備功能結構設計等方面來考慮。

1、建立廠務動力車間,采用冷水機等制冷設備將常溫的切割水降低到切割工藝所需的水溫。盡可能縮短冷卻水輸入和輸出管道的距離,并采用隔熱保溫棉包裹,減少水溫在傳輸過程中的熱量消耗,確保冷卻水的供給溫度穩定且可控制。

2、建立新產品、新材料的風險評估流程。根據產品生產評估結果,將切割參數、工藝條件、生產要求等制定標準作業流程。針對核心風險點進行分級授權管控,避免量產時造成切割熔錫失效。

3、在設備設計層面,將應用穩定的噴嘴機構等備件圖紙進行標準化。同步上傳系統存檔并更新到設備技術協議,為后續新購設備提供技術參考。

4、影響切割熔錫的核心備件,如刀架噴嘴、刀片等,建立安裝調試和維護技能培訓指導書,培訓工程技術人員,提高設備切割熔錫的管控能力。

5、冷卻水輸出設備、傳輸管路、過濾裝置、噴嘴裝置等硬件設施,制定預防性維護要求和管理周期。定期對影響切割熔錫的部件進行數據跟蹤、功能檢查,定期維護保養及更換。

6結束語

微電子封裝QFN產品的外形結構緊湊,體積小、重量輕、電性能和散熱性好,因此多應用于集成度相對較高的高端電子產品中。根據其方形扁平的形狀特點,整條料片分離成單顆的電路產品,通常采用效率高、成本低的切割工藝。本文是基于切割工藝生產中的切割熔錫失效現狀,從實際應用和設計的角度給予分析和對策探討,以供參考。

歡迎掃碼添加小編微信

掃碼加入知識星球,領取公眾號資料

原文標題:芯片制造工藝流程.圖文詳解.一文通

文章出處:【微信公眾號:半導體封裝工程師之家】歡迎添加關注!文章轉載請注明出處。

-

封裝

+關注

關注

126文章

7794瀏覽量

142740

發布評論請先 登錄

相關推薦

電鍍工藝流程詳解 電鍍技術在工業中的應用

SMT工藝流程詳解

簡述連接器的工藝流程

傳統封裝工藝流程簡介

不同PCBA工藝流程的成本與報價介紹

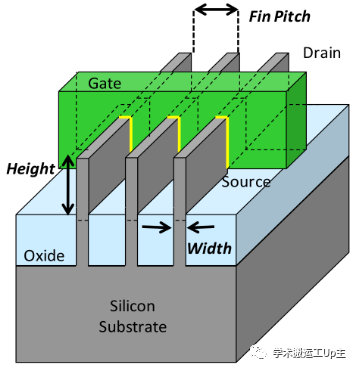

22nm技術節點的FinFET制造工藝流程

芯片制造工藝流程.圖文詳解.一文通

芯片制造工藝流程.圖文詳解.一文通

評論