從綜合角度看,Vivado 2024.1對SystemVerilog和VHDL-2019的一些特性開始支持。先看SystemVerilog。

支持SystemVerilog AOI (Array of Instances)

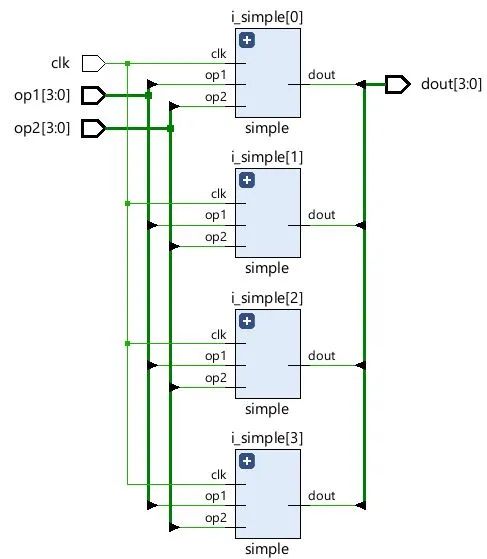

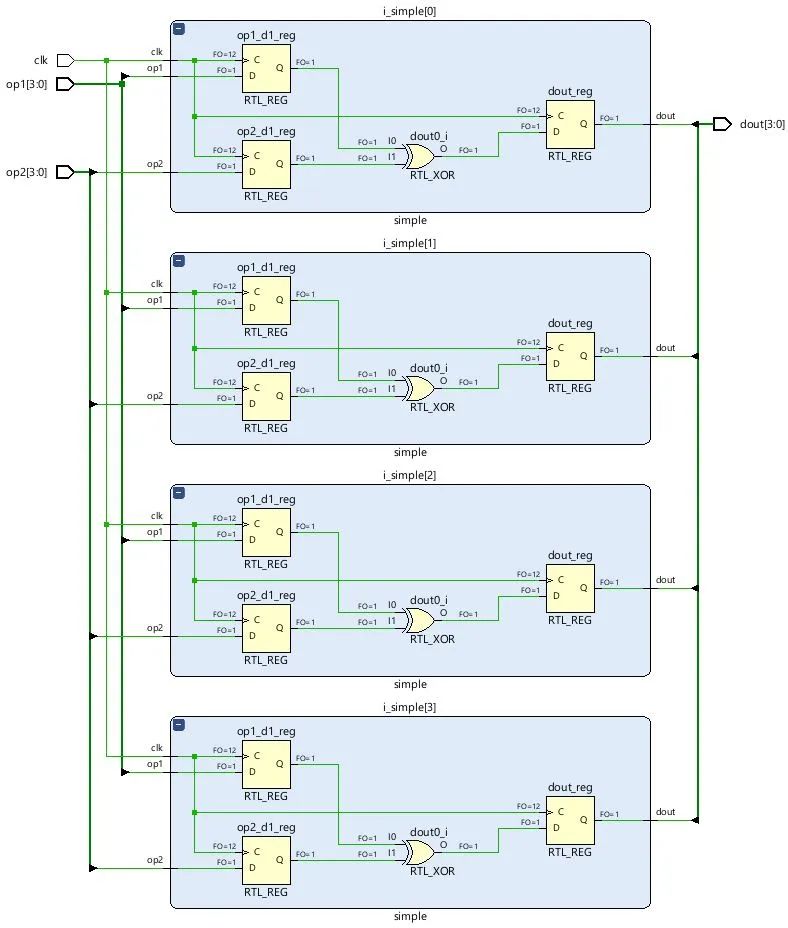

AOI指的是在實(shí)例化某個module時,可以將其聲明為數(shù)組,這樣就等效于同時聲明了多個module,如下圖所示。代碼第8行對模塊simple進(jìn)行實(shí)例化,實(shí)例化名為i_simple[M-1:0],這里M等于4。實(shí)際上就等于實(shí)例化了4個simple,每個的實(shí)例化名分別為i_simple[0]~i_simple[3]。這樣可以不用for generate語句。打開Elaborated Design視圖可以看到其中的連接關(guān)系。

支持VHDL-2019引用端口屬性的功能

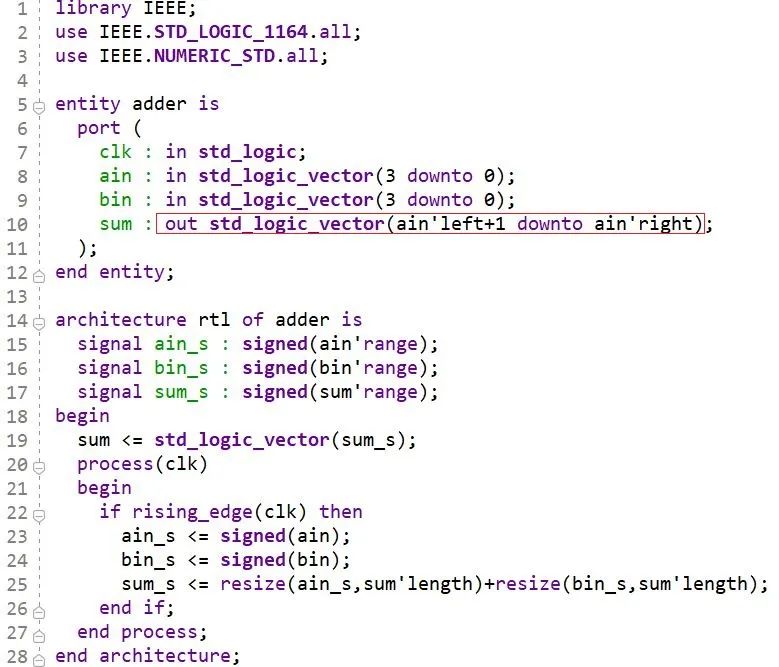

VHDL-2019支持在端口列表中引用端口屬性。如下圖所示代碼片段,代碼第10行聲明端口sum時,對sum位寬的定義就引用了輸入端口ain的屬性left和right。其中ain’left返回值為3,ain’right返回值為0。同時還可以注意到第10行的末尾增添了分號。這也是VHDL-2019的新特性。之前的VHDL版本,由于端口列表中的最后一個端口聲明不能加分號,導(dǎo)致端口列表聲明不一致,VHDL-2019則解決了這一問題。但這個分號不是強(qiáng)制的,是可選的,即沒有分號也同樣是正確的。

支持VHDL-2019的多位寬端口部分互連功能

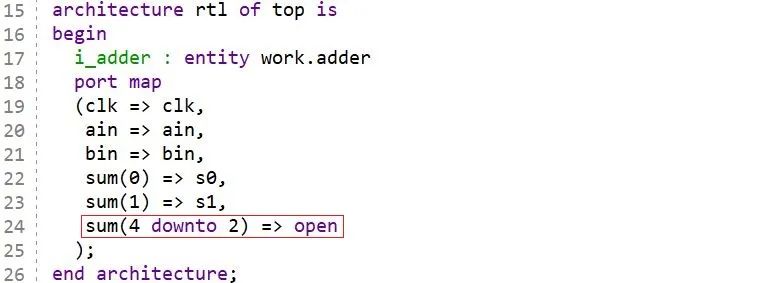

使用VHDL當(dāng)對某個模塊進(jìn)行實(shí)例化時,若該模塊某個輸出端口未使用,需要聲明為open狀態(tài)。如果該端口是個多位寬的信號,某些位的數(shù)據(jù)需要連接到其他模塊,某些位的數(shù)據(jù)不需要,那么VHDL-2019可以支持部分位的數(shù)據(jù)標(biāo)記為open狀態(tài)。如下圖所示代碼,代碼第22行和第23行分別標(biāo)記了sum(0)和sum(1)的連接關(guān)系,第24行則將sum(4 downto 2)標(biāo)記為open狀態(tài)。從代碼風(fēng)格角度看,該代碼片段還體現(xiàn)了如何更好的實(shí)例化指定模塊,如代碼第17行所示,采用entity work的方式,這樣的好處是不用在architecture中聲明component,從而使代碼更簡潔。

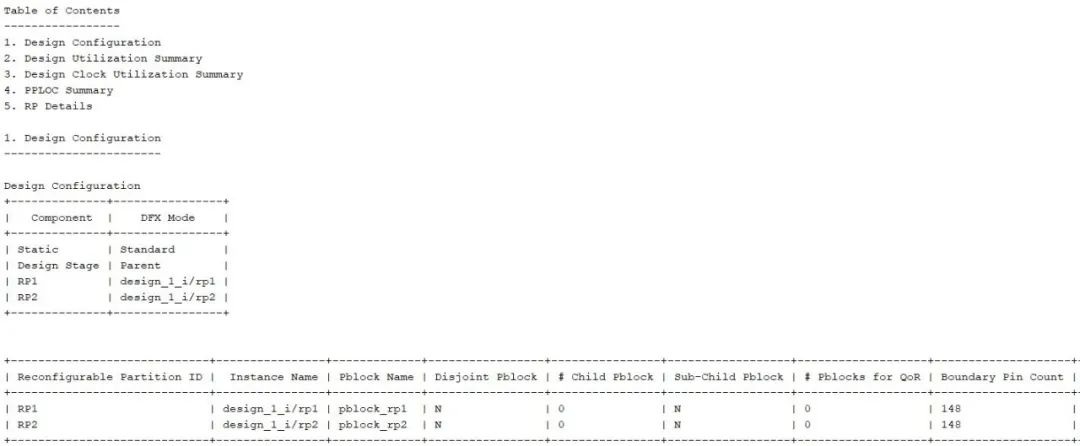

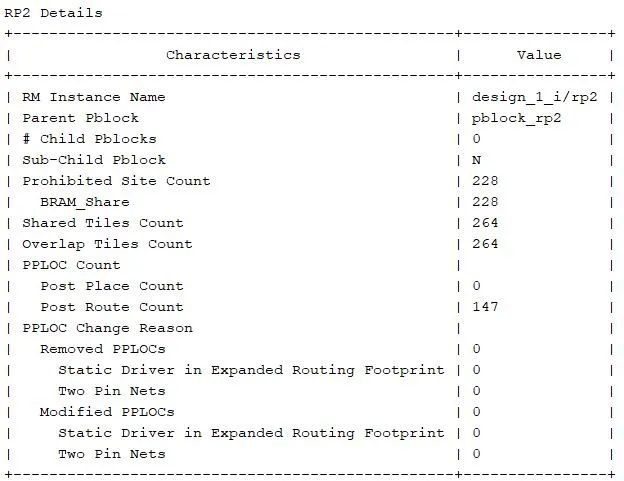

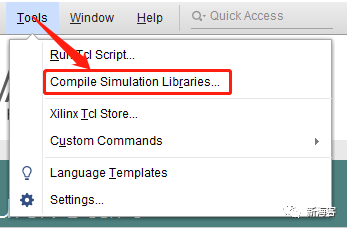

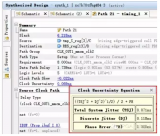

新增支持DFX的命令report_dfx_summary

新增命令report_dfx_summary,針對基于Versal器件的DFX設(shè)計(jì)。該命令會生成5個部分的內(nèi)容,如下圖所示。這對于DFX的分析會很有幫助。從該報(bào)告中可以看每個動態(tài)區(qū)的大小以及資源利用率、靜態(tài)區(qū)的可用資源及資源利用率、時鐘資源利用率以及PPLOC。除此之外,對于每個RP,還會顯示RP的Pblock名稱、共享的Tile等更具體的信息。

-

代碼

+關(guān)注

關(guān)注

30文章

4753瀏覽量

68368 -

design

+關(guān)注

關(guān)注

0文章

157瀏覽量

45714 -

Vivado

+關(guān)注

關(guān)注

19文章

808瀏覽量

66347

原文標(biāo)題:Vivado 2024.1有哪些新特性?(2)

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術(shù)驛站】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

請問我可以免費(fèi)更新Vivado版本到2016.1嗎?

怎么將vivado12.3更新到最新的15.4版本?

Vivado Design Suite HLx 版本 2016.4 現(xiàn)已發(fā)布

Vivado Design Suite 2014.4.1 現(xiàn)已推出!

賽靈思Vivado設(shè)計(jì)套件推出2013.1版本,提供IP 集成器和高層次綜合功能

使用Vivado 2017調(diào)用Modelsim的詳細(xì)步驟

如何使用Vivado 2022.1版本工具鏈實(shí)現(xiàn)ZCU102 USB啟動(上)

Vivado Design Suite用戶指南:版本說明、安裝和許可

Vivado2018版本中Modelsim的配置

Vivado 2024.1版本的新特性(2)

Vivado 2024.1版本的新特性(2)

評論