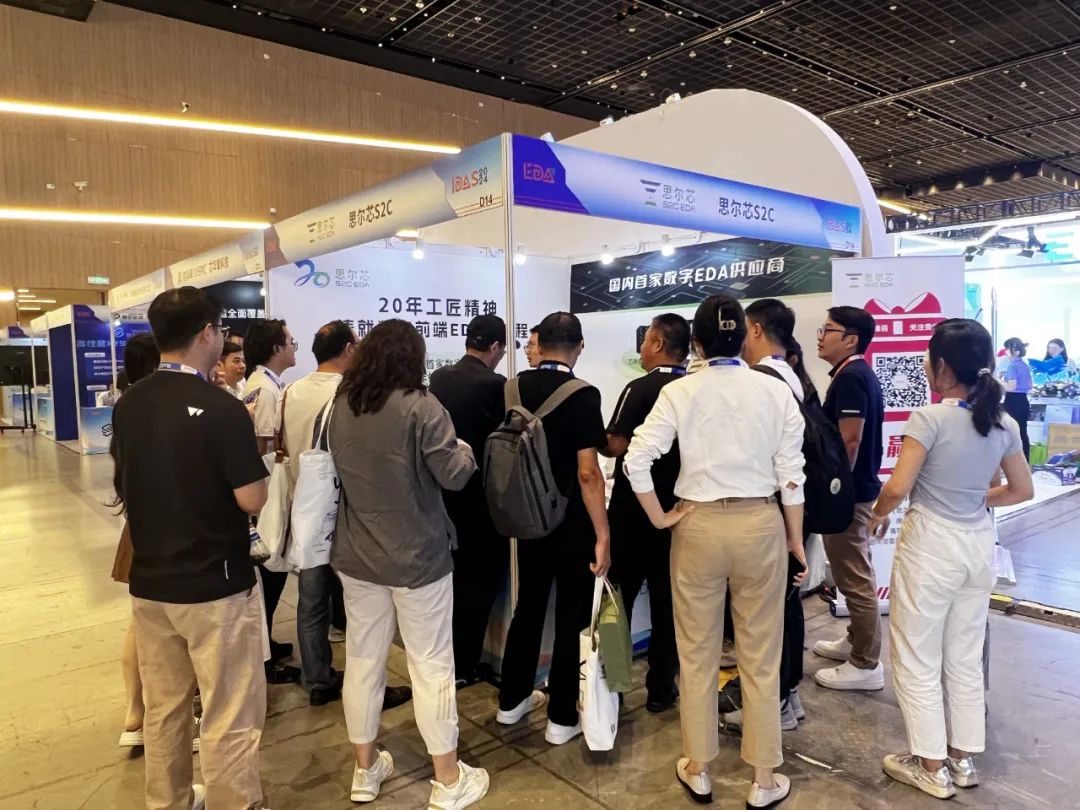

2024年9月23日至24日,備受矚目的第二屆設(shè)計自動化產(chǎn)業(yè)峰會(IDAS 2024)在上海張江順利舉行。本次峰會以“逐浪”為主題,與產(chǎn)業(yè)上下游頭部企業(yè)、高校、科研院所等共探EDA及集成電路領(lǐng)域的無限可能。作為國內(nèi)首家數(shù)字EDA企業(yè),思爾芯受邀亮相此次峰會。

展會現(xiàn)場,思爾芯更是以完善的數(shù)字前端EDA解決方案亮相,通過生動的現(xiàn)場Demo體驗,向與會者全方位展示了技術(shù)實力與創(chuàng)新成果。其中,RISC-V香山圖形化顯示項目作為RISC-V架構(gòu)芯片設(shè)計作為典型代表,不僅凸顯了思爾芯在原型驗證技術(shù)領(lǐng)域的深厚積累,也為RISC-V架構(gòu)的多元化應(yīng)用探索樹立了行業(yè)典范。

展會現(xiàn)場,思爾芯更是以完善的數(shù)字前端EDA解決方案亮相,通過生動的現(xiàn)場Demo體驗,向與會者全方位展示了技術(shù)實力與創(chuàng)新成果。其中,RISC-V香山圖形化顯示項目作為RISC-V架構(gòu)芯片設(shè)計作為典型代表,不僅凸顯了思爾芯在原型驗證技術(shù)領(lǐng)域的深厚積累,也為RISC-V架構(gòu)的多元化應(yīng)用探索樹立了行業(yè)典范。

此外,思爾芯還展示了聯(lián)合仿真Demo,同樣吸引了眾多與會者的目光。該Demo由思爾芯“芯神匠”架構(gòu)設(shè)計與“芯神馳”軟件仿真組成。近年來,隨著半導(dǎo)體行業(yè)的快速發(fā)展,聯(lián)合仿真技術(shù)對于提升設(shè)計驗證效率與關(guān)鍵部件的驗證是一種重要的手段。它通過整合軟硬件資源,構(gòu)建了一個能夠集成并協(xié)調(diào)多個仿真系統(tǒng)與現(xiàn)實系統(tǒng)運行的聯(lián)合仿真平臺。思爾芯的“芯神匠”架構(gòu)設(shè)計工具,該平臺能夠一站式完成架構(gòu)設(shè)計、設(shè)計驗證,并通過不同抽象層次的建模仿真優(yōu)化IP、SoC及系統(tǒng)。思爾芯的聯(lián)合仿真框架不僅基于圖形化的架構(gòu)建模方式,提供了直觀易用的操作界面,還通過緊密結(jié)合架構(gòu)建模與混合仿真驗證,實現(xiàn)了對設(shè)計錯誤的快速發(fā)現(xiàn)與精確定位,極大地提升了設(shè)計效率與質(zhì)量。尤為值得一提的是,“芯神匠”還可與思爾芯的其他EDA工具,例如芯神鼎硬件仿真、芯神瞳原型驗證等無縫對接,實現(xiàn)混合仿真,這種高度集成的解決方案進一步增強了設(shè)計驗證的全面性和準確性。

思爾芯通過其創(chuàng)新的Demo,不僅展示了公司在EDA領(lǐng)域的技術(shù)實力和創(chuàng)新能力,更為行業(yè)內(nèi)外提供了寶貴的實踐經(jīng)驗和啟示。未來,隨著半導(dǎo)體技術(shù)的不斷進步和市場需求的日益多樣化,思爾芯將繼續(xù)深耕數(shù)字EDA領(lǐng)域,不斷優(yōu)化自有EDA工具,以市場為導(dǎo)向為全球客戶提供更加高效的設(shè)計驗證解決方案。

-

仿真

+關(guān)注

關(guān)注

50文章

4041瀏覽量

133413 -

RISC-V

+關(guān)注

關(guān)注

44文章

2228瀏覽量

46026 -

思爾芯

+關(guān)注

關(guān)注

0文章

116瀏覽量

1286

發(fā)布評論請先 登錄

相關(guān)推薦

思爾芯IDAS 2024:RISC-V圖形顯示與仿真技術(shù)革新

思爾芯加入甲辰計劃,共推RISC-V生態(tài)

思爾芯加入甲辰計劃,持續(xù)助力共推 RISC-V 生態(tài)

RISC-V Summit China 2024 | 青稞RISC-V+接口PHY,賦能RISC-V高效落地

2024 RISC-V 中國峰會:華秋電子助力RISC-V生態(tài)!

2024 RISC-V 中國峰會:華秋電子助力RISC-V生態(tài)!

思爾芯受邀參加2024 RISC-V中國峰會

思爾芯即將亮相2024 RISC-V中國峰會

2024 第四屆 RISC-V 中國峰會將于 8 月 19 日至 25 日在杭州舉辦

數(shù)字EDA賦能RISC-V落地演進技術(shù)研討會成功舉辦

芯原科技牽頭的RISC-V創(chuàng)新聯(lián)合體獲正式認定授牌

思爾芯亮相第二屆玄鐵RISC-V生態(tài)大會

助力RISC-V高效開發(fā)!思爾芯亮相玄鐵RISC-V生態(tài)大會

思爾芯亮相玄鐵RISC-V生態(tài)大會 思爾芯EDA助力RISC-V高效開發(fā)

逐浪IDAS 2024:思爾芯展示RISC-V圖形化顯示與聯(lián)合仿真創(chuàng)新

逐浪IDAS 2024:思爾芯展示RISC-V圖形化顯示與聯(lián)合仿真創(chuàng)新

評論