設(shè)計(jì)電路時(shí),很多工程師不會(huì)忘記添加各種各樣的保護(hù)電路,尤其在特別脆弱的I/O口。或許你以前沒有關(guān)注到“高壓脈沖”,那么如何避免電路設(shè)計(jì)這些坑。

在產(chǎn)品設(shè)計(jì)過程中,我們往往更關(guān)注產(chǎn)品的外觀、功能、性能,而對(duì)一些細(xì)節(jié)沒有給予足夠的重視。很多時(shí)候,給產(chǎn)品造成重大問題的正是這些看似不起眼的細(xì)節(jié)問題。

我們?cè)谠O(shè)計(jì)P800isp的電源電路時(shí),重點(diǎn)關(guān)注了電壓幅值、紋波、負(fù)載調(diào)整率等硬性指標(biāo),而上電瞬間的情況被我們忽視了。當(dāng)我們用P800isp對(duì)客戶提供的目標(biāo)板上的芯片進(jìn)行編程調(diào)試時(shí),發(fā)現(xiàn)一個(gè)奇怪的現(xiàn)象:

當(dāng)編程器上電穩(wěn)定后再接上目標(biāo)板時(shí),就可以對(duì)目標(biāo)芯片進(jìn)行擦除、編程、校驗(yàn);

當(dāng)接上目標(biāo)板后再給編程器上電時(shí),對(duì)目標(biāo)芯片的任何操作都會(huì)失敗;

當(dāng)接上目標(biāo)板后再給編程器上電后,這個(gè)目標(biāo)板后面不管是先上電再接線還是先接線再上電,都會(huì)編程失敗。

研發(fā)同事以身試險(xiǎn),用手去觸摸編程失敗的芯片,被燙得手指都起了泡。用萬用表測(cè)量發(fā)現(xiàn)編程失敗的芯片電源腳和地已經(jīng)短路了。測(cè)量編程電源的電壓正常。因此,工程師根據(jù)經(jīng)驗(yàn)推測(cè)很有可能是編程器上電時(shí)編程電源有異常高壓輸出將目標(biāo)芯片擊穿。用示波器捕獲編程器上電瞬間編程電源Vout的波形證實(shí)了我們的猜想。

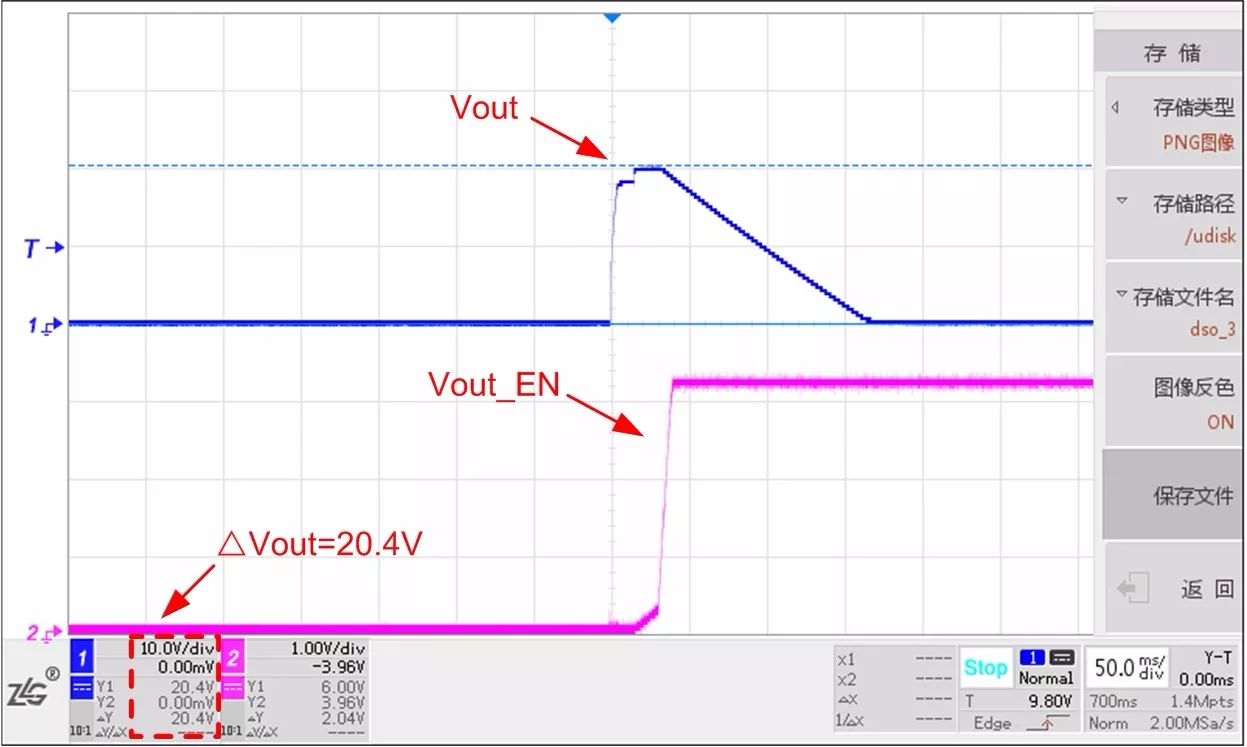

如圖1所示,編程器上電瞬間,編程電源Vout有高達(dá)20.4V、持續(xù)時(shí)間長達(dá)150ms的脈沖輸出到目標(biāo)芯片。供電電源才3.3V的目標(biāo)芯片顯然無法承受這樣的高壓脈沖。

圖1 上電瞬間Vout的異常輸出

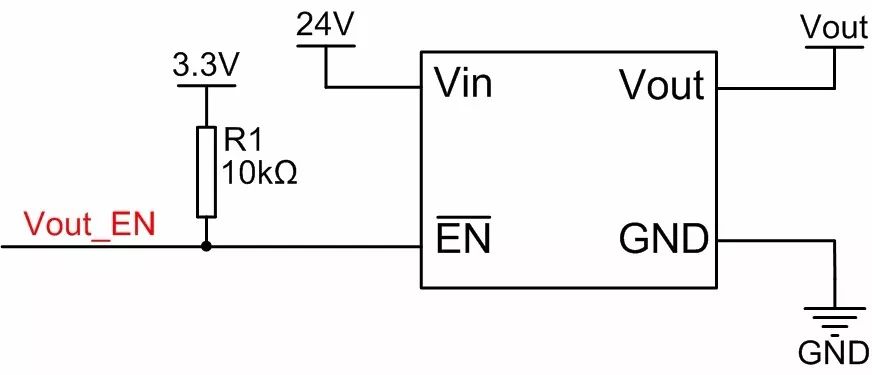

從圖2的Vout電源電路的示意圖看出Vout是由Vout_EN控制的,低電平使能Vout輸出。Vout_EN上拉到3.3V高電平,上電瞬間默認(rèn)應(yīng)該禁能Vout輸出的,怎么還會(huì)有這個(gè)高壓脈沖輸出呢?

圖2 Vout電源電路示意圖

從圖1可以發(fā)現(xiàn),Vout輸出20.4V并持續(xù)近30ms后,Vout_EN才上拉到高電平禁能Vout輸出,此后Vout才逐漸降低到0V。為什么Vout_EN要比Vout滯后30ms才有效,而不是一上電就有效呢?

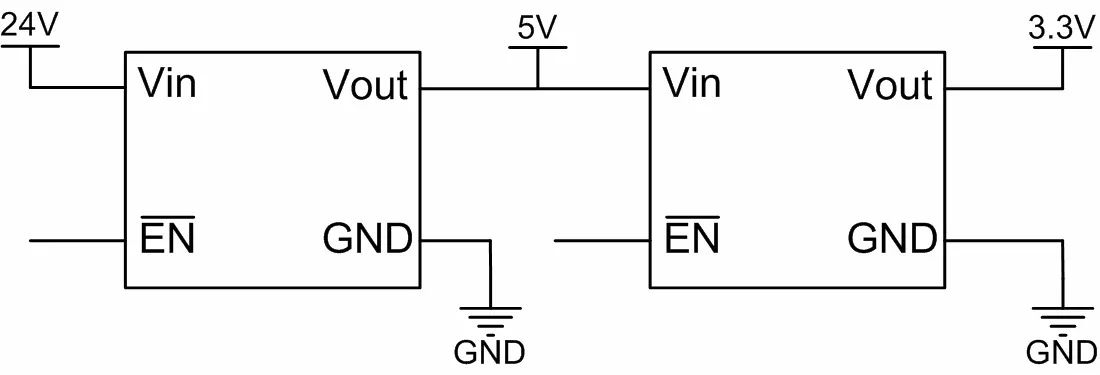

我們看下圖3,3.3V是由24V轉(zhuǎn)換成5V再轉(zhuǎn)換而成的,因而3.3V的產(chǎn)生需要一定時(shí)間,相應(yīng)的Vout_EN也需要一定時(shí)間才能有效。正是由于這個(gè)時(shí)間差,Vout才可以輸出20.4V的高壓脈沖。

圖3 3.3V電源示意圖

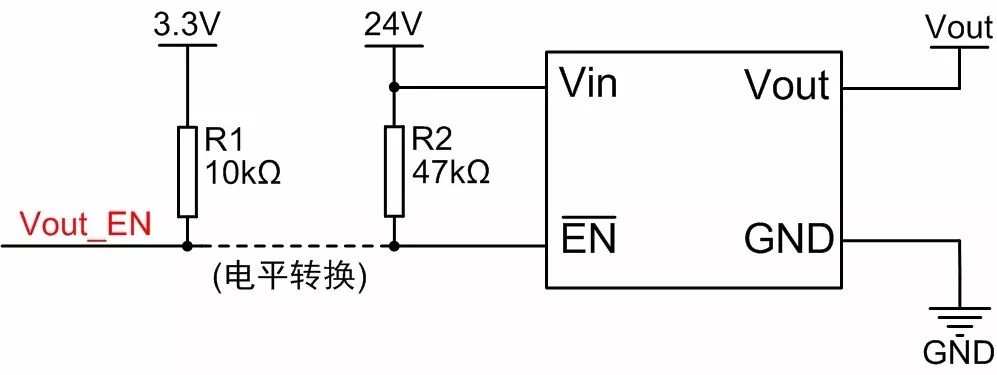

要解決使能信號(hào)滯后的問題,最好的解決方案就是用輸入電源Vin作為使能電平。當(dāng)輸入電源上電時(shí),就能直接禁能Vout的輸出。在Vout_EN和Vin使能電平之間加入電平轉(zhuǎn)換電路,使3.3V電平的Vout_EN可以在程序運(yùn)行后正常控制Vout的輸出。經(jīng)過改進(jìn)后,上電瞬間的高壓脈沖被完美的消除了。

圖4 改進(jìn)后的Vout電源電路

所以在產(chǎn)品的設(shè)計(jì)過程中,容不得半點(diǎn)疏忽,具有匠心精神,才能打造出精品!

-

保護(hù)電路

+關(guān)注

關(guān)注

45文章

868瀏覽量

101403 -

高壓脈沖

+關(guān)注

關(guān)注

0文章

13瀏覽量

11361

原文標(biāo)題:別讓“高壓脈沖”毀了你的芯片

文章出處:【微信號(hào):ZLG_zhiyuan,微信公眾號(hào):ZLG致遠(yuǎn)電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

高壓脈沖電容器與普通電容器的區(qū)別

高壓脈沖電容器的廣泛應(yīng)用及激光焊錫的優(yōu)勢(shì)

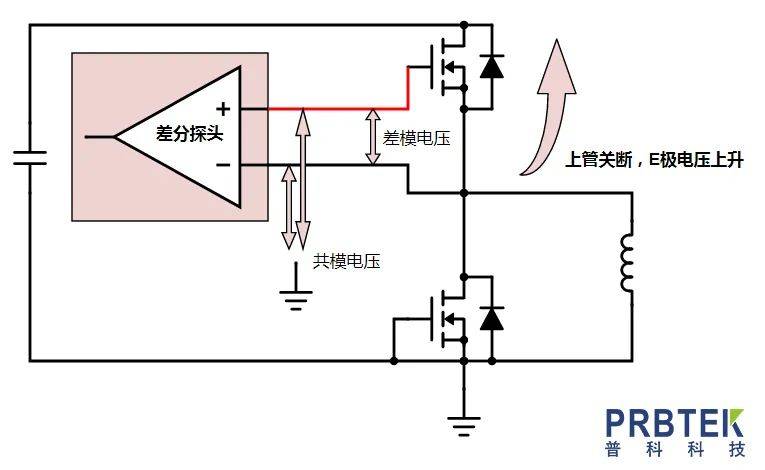

雙脈沖測(cè)試中高壓差分探頭的使用問題解析

脈沖與數(shù)字信號(hào)之間的關(guān)系是什么?數(shù)字電路的工作信號(hào)是脈沖嗎?

自諧振現(xiàn)象對(duì)電路性能的影響及其避免方法

安泰高壓放大器電路設(shè)計(jì)方案是什么

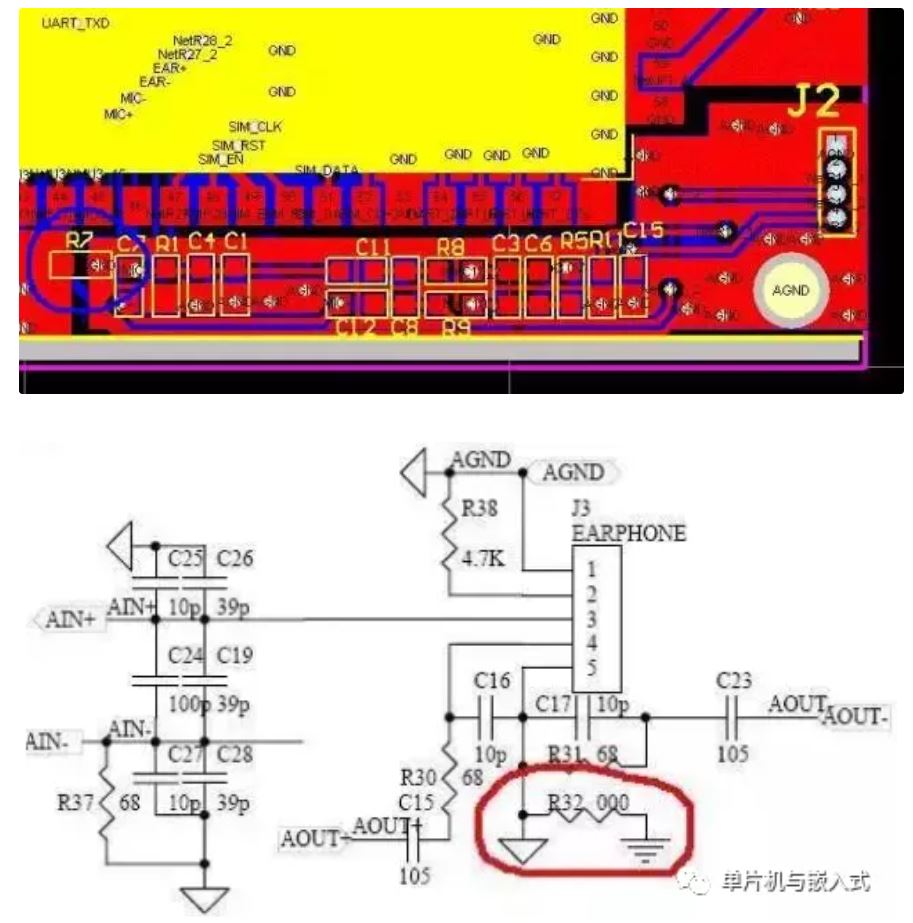

深入研究電路設(shè)計(jì)中的“地”之謎:詳解分類與作用應(yīng)用

電路設(shè)計(jì)中的“地”

二極管在脈沖發(fā)生電路中的應(yīng)用

放大器電路設(shè)計(jì):如何避免常見問題

硬件電路設(shè)計(jì)之接地問題

如何避免電路設(shè)計(jì)中的“高壓脈沖”

如何避免電路設(shè)計(jì)中的“高壓脈沖”

評(píng)論