可編程片上系統(tǒng)( SoPC)是在可編程邏輯器件的基礎(chǔ)上發(fā)展起來(lái)的一種靈活、高效的嵌入式系統(tǒng)設(shè)計(jì)解決方案,系統(tǒng)設(shè)計(jì)者可以從傳統(tǒng)的板級(jí)系統(tǒng)設(shè)計(jì)轉(zhuǎn)換到芯片級(jí)系統(tǒng)設(shè)計(jì),將系統(tǒng)設(shè)計(jì)中所需要的各個(gè)功能單元以IP ( Intellectual Property)的形式集成到FPGA中,實(shí)現(xiàn)集成度更高的嵌入式系統(tǒng)。

Virtex-4系列FPGA是由Xilinx公司推出的包含多個(gè)面向特定領(lǐng)域平臺(tái)的FPGA產(chǎn)品,各個(gè)系列的FPGA通過(guò)對(duì)嵌入式處理器、高性能DSP功能單元、增強(qiáng)時(shí)鐘管理、存儲(chǔ)器、并行和串行I/O、混合信號(hào)以及其它功能模塊等的優(yōu)化組合使其可以滿足特定領(lǐng)域的應(yīng)用需求。Virtex-4系列的三個(gè)平臺(tái)分別是:針對(duì)邏輯應(yīng)用的Virtex-4 LX,針對(duì)超高性能信號(hào)處理的Virtex-4SX,針對(duì)嵌入式處理和高速串行連接的Virtex-4 FX。其中Virtex-4 FX系列FPGA主要是為復(fù)雜系統(tǒng)應(yīng)用提供優(yōu)化,特別是網(wǎng)絡(luò)、存儲(chǔ)、電信和嵌入式應(yīng)用中的高速串行連接和嵌入式處理,在其配套的EDK環(huán)境中還為系統(tǒng)設(shè)計(jì)者提供豐富的總線、時(shí)鐘、外設(shè)、JTAG口等IP資源,使設(shè)計(jì)者能夠方便的搭建自己的嵌入式系統(tǒng)。

1Virtex-4 FX系列FPGA介紹

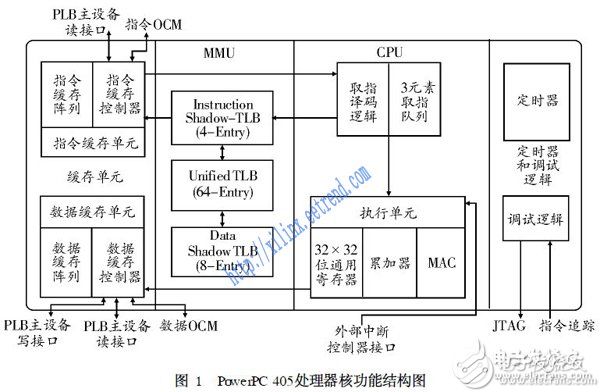

Virtex-4 FX系列FPGA芯片內(nèi)至少包含一個(gè)PowerPC405處理器核,其功能結(jié)構(gòu)如圖1所示,該處理器核為32位哈佛結(jié)構(gòu)的R ISC硬核,最高工作頻率為400MHz。PowerPC405處理器包括以下功能單元: ( 1)5級(jí)數(shù)據(jù)通道流水線,包括取指、譯碼、執(zhí)行、寫回、裝入寫回5 級(jí)流水段; ( 2 ) 一個(gè)虛擬內(nèi)存管理單元(MMU) ,支持可變頁(yè)面大小和寫保護(hù)、控制訪問選項(xiàng);(3)獨(dú)立的指令Cache和數(shù)據(jù)Cache; ( 4)支持調(diào)試和跟蹤,包含一個(gè)JTAG接口; ( 5)三個(gè)可編程計(jì)時(shí)器。另外, PowerPC 405硬核還具有如下特點(diǎn): ( 1)支持硬件乘法和除法; ( 2) 32個(gè)32位通用寄存器; ( 3) 16KB兩路組相聯(lián)方式指令緩存( set-associave) ; (4) 16KB兩路組相聯(lián)方式數(shù)據(jù)緩存、寫回/寫直達(dá); ( 5 ) 實(shí)現(xiàn)PowerPC用戶指令集架構(gòu)(U ISA) ; ( 6)專用的片上存儲(chǔ)器接口(OCM) ; ( 7 )支持IBM CoreConnect總線架構(gòu)。

CoreConnect總線架構(gòu)是由IBM開發(fā)的一種片上總線通信連接技術(shù)。CoreConnect總線包括處理器局部總線( PLB) 、片上外設(shè)總線(OPB)和設(shè)備控制寄存器總線(DCR) 。PLB總線為主設(shè)備和從設(shè)備之間提供高帶寬、低延遲的連接,OPB總線為連接具有不同總線寬度和時(shí)序要求的外設(shè)提供了一條途徑,減少了對(duì)PLB性能的影響,DCR總線用來(lái)控制PowerPC405處理器中的通用寄存器和設(shè)備寄存器之間的數(shù)據(jù)傳輸。

2基于SoPC的嵌入式系統(tǒng)設(shè)計(jì)技術(shù)

2. 1平臺(tái)技術(shù)

在平臺(tái)的基礎(chǔ)上來(lái)構(gòu)建嵌入式系統(tǒng)為設(shè)計(jì)者提供了極大的便利, Xilinx 推出的嵌入式開發(fā)工具包( EDK)集成了諸如硬件平臺(tái)產(chǎn)生器(platgen) 、硬件仿真模型產(chǎn)生器( SimGen) 、軟件平臺(tái)產(chǎn)生器( libgen) 、應(yīng)用軟件編譯工具(GNU Compiler) 、軟件調(diào)試工具(GNU Debugger) 等一系列工具。設(shè)計(jì)者可以通過(guò)集成在EDK環(huán)境下的Xilinx平臺(tái)工作室(XPS)方便的調(diào)用各種工具進(jìn)行基于SoPC的嵌入式系統(tǒng)設(shè)計(jì)。EDK環(huán)境下為系統(tǒng)設(shè)計(jì)者提供了豐富的IP資源,可利用現(xiàn)有的資源迅速搭建自己的嵌入式系統(tǒng),完成整個(gè)PowerPC系統(tǒng)硬件的開發(fā)。如果開發(fā)工具包提供的IP庫(kù)不能滿足系統(tǒng)設(shè)計(jì)者的需求,設(shè)計(jì)者也可定制自己的IP。圖2所示為EDK開發(fā)環(huán)境圖形界面。

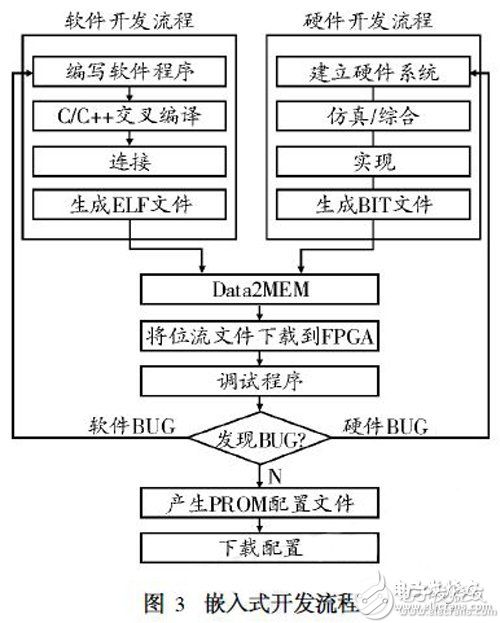

EDK環(huán)境為其自帶的IP提供了相應(yīng)的驅(qū)動(dòng)程序及相關(guān)的函數(shù),設(shè)計(jì)者可以通過(guò)調(diào)用這些函數(shù)加快應(yīng)用程序的開發(fā)。對(duì)于設(shè)計(jì)者自行研制的IP,則需要編寫相應(yīng)的驅(qū)動(dòng)程序。應(yīng)用程序編寫完成后,調(diào)用EDK下的GNU工具,編譯連接生成可執(zhí)行文件,再將硬件、軟件文件結(jié)合在一起,產(chǎn)生可下載的位流文件下載到FPGA,使用Xilinx微處理器調(diào)試工具(XMD ) 連接GNU調(diào)試工具進(jìn)行應(yīng)用程序調(diào)試,在確認(rèn)應(yīng)用程序正確無(wú)誤,能實(shí)現(xiàn)系統(tǒng)功能之后,即可將位流文件轉(zhuǎn)換成PROM的配置文件(MCS文件) 下載到目標(biāo)板上的PROM,從而完成整個(gè)設(shè)計(jì)開發(fā)。圖3為利用EDK工具進(jìn)行嵌入式系統(tǒng)開發(fā)的流程。

2. 2系統(tǒng)架構(gòu)及硬件設(shè)計(jì)

基于SoPC的嵌入式系統(tǒng)設(shè)計(jì)過(guò)程中,系統(tǒng)設(shè)計(jì)者首先要明確設(shè)計(jì)需求,這對(duì)于整個(gè)設(shè)計(jì)具有指導(dǎo)性作用,也是將來(lái)設(shè)計(jì)完成后檢驗(yàn)設(shè)計(jì)是否可用的標(biāo)準(zhǔn)之一。系統(tǒng)設(shè)計(jì)者根據(jù)設(shè)計(jì)需求來(lái)確定其系統(tǒng)架構(gòu),定義系統(tǒng)主要模塊組成,決定其接口類型、總線結(jié)構(gòu)、硬件功能及軟件功能,完備的系統(tǒng)架構(gòu)定義要能滿足基本的設(shè)計(jì)需求,并能最大限度的提高系統(tǒng)整體性能。

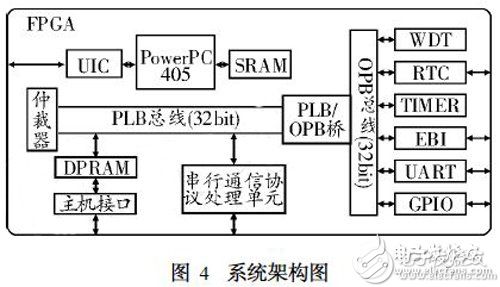

基于SoPC的多路傳輸數(shù)據(jù)總線接口的設(shè)計(jì)需求是在板級(jí)多路傳輸數(shù)據(jù)總線接口模塊的基礎(chǔ)上提出的,通過(guò)對(duì)板級(jí)器件的IP化,將原有板上芯片以IP的形式集成到FPGA中,用單片集成電路實(shí)現(xiàn)原板級(jí)電路的設(shè)計(jì)。根據(jù)板級(jí)多路傳輸數(shù)據(jù)總線接口模塊的系統(tǒng)結(jié)構(gòu),提出了如圖4所示的基于SoPC的嵌入式系統(tǒng)架構(gòu)圖,該嵌入式系統(tǒng)集成了PowerPC405處理器、串行通信總線協(xié)議處理器,具有實(shí)時(shí)時(shí)鐘(RTC) 、看門狗(WDT) 、計(jì)時(shí)器( TIMER)功能,可實(shí)現(xiàn)GJB289A-97(數(shù)字式時(shí)分制指令/響應(yīng)型多路傳輸數(shù)據(jù)總線)中規(guī)定的RT/BC功能,支持實(shí)現(xiàn)ISBC協(xié)議(改進(jìn)的靜態(tài)總線控制協(xié)議) ,通過(guò)方式選擇分別支持LBE總線訪問、VME總線訪問、PC I總線訪問(通過(guò)PLX9054 橋接器) 、PCI-Express總線訪問(通過(guò)PEX8311橋接器)四

種主機(jī)接口訪問方式。

硬件設(shè)計(jì)過(guò)程中,系統(tǒng)設(shè)計(jì)者在XPS圖形界面下調(diào)用現(xiàn)成的IP庫(kù),搭建SoPC的硬件環(huán)境,通過(guò)硬件平臺(tái)產(chǎn)生器(p latgen)生成硬件文件,其中PowerPC405處理器、雙口存儲(chǔ)器、SRAM、串行通信總線協(xié)議處理單元掛接在PLB總線上;實(shí)時(shí)時(shí)鐘(RTC) 、看門狗(WDT) 、計(jì)時(shí)器(TIMER) 、外部總線接口( EB I) 、通用輸入輸出接口( GPIO) 、串口控制器(UART)掛接在OPB 總線上;通用中斷控制器(UIC) 、仲裁器和PLB /OPB 橋的寄存器通過(guò)DCR總線訪問。硬件架構(gòu)搭建起后通過(guò)硬件仿真模型產(chǎn)生器( SimGen)對(duì)硬件的功能進(jìn)行仿真。

2. 3軟件設(shè)計(jì)

基于SoPC的嵌入式系統(tǒng)軟件設(shè)計(jì)過(guò)程中,軟件設(shè)計(jì)者要明確嵌入式系統(tǒng)的相關(guān)硬件配置,諸如內(nèi)存地址映射關(guān)系,硬件寄存器配置等,這將決定開發(fā)出的嵌入式軟件是否具備實(shí)用性。嵌入式軟件的設(shè)計(jì)通常包括CPU啟動(dòng)代碼,系統(tǒng)初始化代碼,硬件自測(cè)試程序,設(shè)備驅(qū)動(dòng)程序,實(shí)時(shí)操作系統(tǒng)及應(yīng)用軟件等,根據(jù)不同的系統(tǒng)需求,軟件包含的內(nèi)容稍有差異。軟件設(shè)計(jì)階段,設(shè)計(jì)者將選擇出編譯和調(diào)試工具并完成編程。

基于SoPC的多路傳輸數(shù)據(jù)總線接口的軟件由初始化程序、自測(cè)試程序、BC /RT控制程序組成。基于SoPC的嵌入式軟件開發(fā)是在EDK環(huán)境下采用C語(yǔ)言編程實(shí)現(xiàn)的,通過(guò)軟件平臺(tái)產(chǎn)生器( libgen) 、應(yīng)用軟件編譯工具(GNU Compiler)編譯連接得到可執(zhí)行文件,該文件可與生成的硬件位流文件通過(guò)JTAG接口一起下載到FPGA 運(yùn)行,也可先將位流文件固化到外部PROM中,應(yīng)用軟件的可執(zhí)行文件轉(zhuǎn)換成二進(jìn)制文件固化到外部FLASH中,系統(tǒng)上電后自動(dòng)加載硬件邏輯并將應(yīng)用軟件搬家到SRAM運(yùn)行。各部分軟件完成如下的功能:初始化程序完成CPU初始化及相關(guān)功能單元的初始化;自測(cè)試程序完成系統(tǒng)的上電自測(cè)試和內(nèi)部自檢; BC /RT控制程序完成該嵌入式系統(tǒng)作為BC或RT時(shí)的數(shù)據(jù)傳輸控制。基于SoPC的嵌入式系統(tǒng)硬件設(shè)計(jì)和軟件設(shè)計(jì)可以并行開展,利用軟硬件協(xié)同設(shè)計(jì)的思想,可加快整個(gè)嵌入式設(shè)計(jì)的速度。

2. 4測(cè)試驗(yàn)證

基于SoPC的嵌入式系統(tǒng)設(shè)計(jì)的測(cè)試驗(yàn)證用來(lái)保證系統(tǒng)不存在軟件和硬件上的缺陷。軟件測(cè)試驗(yàn)證旨在通過(guò)執(zhí)行軟件并觀察其行為是否滿足設(shè)計(jì)要求,而硬件測(cè)試驗(yàn)證則包括了確保硬件能夠?qū)ν庠诘募?lì)作出正確的響應(yīng)并能正確的執(zhí)行軟件。

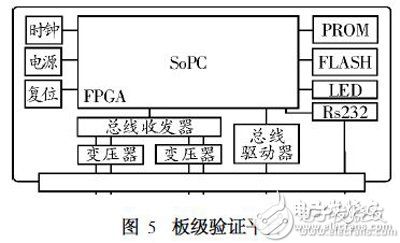

基于SoPC的多路傳輸數(shù)據(jù)總線接口中復(fù)雜的軟硬件結(jié)構(gòu)及其種類繁多的IP資源,使得該系統(tǒng)的測(cè)試驗(yàn)證工作也變得復(fù)雜。在測(cè)試驗(yàn)證過(guò)程中,采用多級(jí)測(cè)試驗(yàn)證技術(shù),首先對(duì)各單一模塊進(jìn)行仿真測(cè)試,進(jìn)行軟硬件協(xié)同驗(yàn)證,再通過(guò)集成各個(gè)功能模塊進(jìn)行系統(tǒng)集成驗(yàn)證,最后進(jìn)行板級(jí)驗(yàn)證。在進(jìn)行系統(tǒng)各模塊功能驗(yàn)證時(shí),軟件可以作為硬件測(cè)試的信號(hào)源,針對(duì)各個(gè)模塊都編寫相應(yīng)的C語(yǔ)言測(cè)試向量,進(jìn)行功能覆蓋率測(cè)試。在單一功能模塊驗(yàn)證測(cè)試的基礎(chǔ)上,將各模塊集成為一個(gè)完整的系統(tǒng),對(duì)整個(gè)系統(tǒng)進(jìn)行集成測(cè)試。進(jìn)行板級(jí)驗(yàn)證時(shí),可以運(yùn)行更為完整、更接近實(shí)際應(yīng)用的C程序測(cè)試向量,使得測(cè)試更全面、更可靠。圖5所示為板級(jí)驗(yàn)證平臺(tái)示意圖。

3結(jié)束語(yǔ)

本文通過(guò)對(duì)Xilinx公司Virtex-4 FX系列FPGA的介紹,分析了其內(nèi)嵌的PowerPC405處理器的體系結(jié)構(gòu)及CoreConnect總線的特點(diǎn),通過(guò)基于SoPC的多路傳輸數(shù)據(jù)總線接口的硬、軟件設(shè)計(jì)技術(shù)和驗(yàn)證技術(shù)的介紹,更好地闡述了基于SoPC的嵌入式系統(tǒng)設(shè)計(jì)方法。在基于SoPC的嵌入式系統(tǒng)設(shè)計(jì)中,通過(guò)單片F(xiàn)PGA實(shí)現(xiàn)多片專用芯片的功能,減少器件數(shù)目,縮小系統(tǒng)面積,增加系統(tǒng)可靠性,達(dá)到了對(duì)板級(jí)多路傳輸數(shù)據(jù)總線接口模塊小型化、集成化的目的。基于SoPC的嵌入式系統(tǒng)設(shè)計(jì)以其數(shù)據(jù)處理速度快、集成度高、開發(fā)周期短、應(yīng)用靈活方便等特點(diǎn),相信在航空航天領(lǐng)域?qū)?huì)得到廣泛的應(yīng)用。

-

FPGA設(shè)計(jì)

+關(guān)注

關(guān)注

9文章

428瀏覽量

26489 -

SOPC技術(shù)

+關(guān)注

關(guān)注

2文章

23瀏覽量

13960

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

探討基于sopc技術(shù)的fpga集成嵌入式系統(tǒng)設(shè)計(jì)

探討基于sopc技術(shù)的fpga集成嵌入式系統(tǒng)設(shè)計(jì)

評(píng)論