1引言

開關電源是目前用途非常廣泛的一種電源設備,然而隨著開關頻率以及開關速度的不斷提高,產生的電磁干擾越來越大,由于市場準入制度的實施,電磁干擾研究已引起了足夠的重視。干擾源是電磁干擾的三要素之一,是電磁干擾研究的重要部分,文獻[1~2]對干擾源進行了說明和描述,還有些學者對抑制干擾源發射的方法[3~5]和干擾源的輻射[6]進行了研究。本文從干擾源入手,對時域開關電壓信號進行電磁干擾特性研究,通過提取MOSFET時域電壓信號的特征參數,利用傅立葉變換(FFT)法,分析了開關信號電磁干擾的頻譜情況以及各參數對頻譜的影響,通過Matlab仿真證明了上述分析的正確性及工程實用性。由于FFT后頻域信號的幅值差別較大,難以研究,因此本文在FFT后,進行了對數變換,這樣既方便研究,又便于與實際進行對比。

2開關電源中的電磁干擾

由于開關電源運用了三極管的開關作用以及PWM技術,使得它與線性電源相比在效率上得到了極大的提高,但是也隨之帶來了許多問題,在三極管的開關過程中,其di/dt, dv/dt的值很大,這使得開關電源在很寬的頻率范圍內的噪聲都很大,這些噪聲經過電源線傳輸到電網或其它電子設備上,就會形成電磁干擾。開關管處的電磁干擾是引起開關電源中電磁干擾現象的重要部分,開關管是重要干擾源。

圖1所示是某型號開關電源中MOSFET漏源極的電壓波形,由一個梯形信號和一個阻尼振蕩信號疊加而成,梯形信號的上升時間和下降時間一般在十納秒到一百納秒之間,電壓和電流的變化率很快,而阻尼振蕩信號則成正弦波的指數衰減形式,它的振蕩周期一般為幾十到幾百納秒。由于梯形信號上升沿下降沿的di/dt, dv/dt很大,將產生很強的干擾電壓和電流,這些電壓和電流通過某種耦合方式傳輸到輸入和輸出端口就會形成電磁干擾。在開關電源中,干擾源處的電磁干擾通常具有頻譜范圍廣,干擾強度大的特點。

3 特征參數的確定

圖1中展示了一MOSFET的漏源極電壓波形,為了研究其上升時間、下降時間、阻尼振蕩等對其頻譜的影響,需要確定該波形的特征參數,然后運用Matlab編程仿真。由于該波形是由一個梯形信號和一個阻尼振蕩信號疊加而成,因此可以用分段函數進行模擬。上升沿可以用式(1)表示。

等特征參數,通過軟件就可以仿真出圖1中的波形。

4 仿真分析

本文采用了Matlab進行仿真。圖2是根據函數(1)~(4)及確定的特征參數對圖1仿真得到的開關信號及其頻譜情況,其

從圖中可以看出,該信號的頻率范圍很寬,頻域信號的幅值也很大,當然,這些干擾信號在耦合到電源外部形成電磁干擾時,能量會有很大的衰減。

仿真時,由于傅立葉變換后各頻率點的幅值變化太大,研究工作非常困難,因此本文對傅立葉變換后的幅值進行了取對數處理,另外對1dBuV的值也進行了歸零。

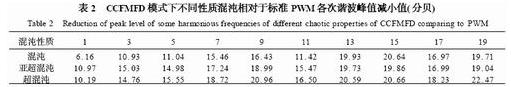

開關信號的上升和下降沿對干擾的幅值影響很大,圖3是上升時間或下降時間為10ns時的上升沿或下降沿的頻譜,把上升時間或下降時間改為100ns再仿真時發現:當上升時間或下降時間增加時,隨著頻率的升高,幅值減小的越快,也就是說,上升或下降時間的變化對高頻干擾幅值影響更大。表1中列出了上升時間或下降時間為10ns和100ns時,不同頻率的電磁干擾幅值和比較結果。從圖中還可以看出在頻率為及其諧波頻率附近,電磁干擾的幅值有一個很大的下降。

為了研究阻尼振蕩對電磁干擾的影響,本文同樣單獨對其進行了研究,圖4為其頻譜,

當把振蕩周期從10個變為5個時,對比發現:振蕩時間的長短對振蕩頻率附近的幅值影響最大,對其它頻率的幅值影響很小。表2列出了振蕩周期分別為10個和5個時不同頻率的幅值。

由以上分析可以看出,適當的增加開關信號的上升和下降時間,可以降低電磁干擾的發射,對高頻更為明顯,盡量減小阻尼振蕩的時間,對振蕩頻率附近的電磁干擾發射,具有明顯的效果。

5 結論

本文研究了開關電源中MOSFET漏源極電壓信號電磁干擾的頻譜特性,發現該信號上升和下降時間的變化對高頻干擾的幅值影響更大,且在頻率為上升和下降時間的倒數及其諧波附近,干擾幅值有一個突降。通過研究該信號中阻尼振蕩時間、周期等參數對電磁干擾的影響,得知振蕩時間的長短對振蕩頻率附近的幅值影響最大,對其它頻率的幅值影響很小。

-

開關電源

+關注

關注

6424文章

8197瀏覽量

477852 -

電磁干擾

+關注

關注

36文章

2229瀏覽量

105138

發布評論請先 登錄

相關推薦

開關電源中MOSFET漏源極電壓信號電磁干擾的頻譜特性研究

開關電源中MOSFET漏源極電壓信號電磁干擾的頻譜特性研究

評論