ESD(靜電放電)是CMOS電路中最為嚴重的失效機理之一,嚴重的會造成電路自我燒毀。論述了CMOS集成電路ESD保護的必要性,研究了在CMOS電路中ESD保護結(jié)構(gòu)的設(shè)計原理,分析了該結(jié)構(gòu)對版圖的相關(guān)要求,重點討論了在I/O電路中ESD保護結(jié)構(gòu)的設(shè)計要求。

1 引言

靜電放電會給電子器件帶來破壞性的后果,它是造成集成電路失效的主要原因之一。隨著集成電路工藝不斷發(fā)展,CMOS電路的特征尺寸不斷縮小,管子的柵氧厚度越來越薄,芯片的面積規(guī)模越來越大,MOS管能承受的電流和電壓也越來越小,而外圍的使用環(huán)境并未改變,因此要進一步優(yōu)化電路的抗ESD性能,如何使全芯片有效面積盡可能小、ESD性能可靠性滿足要求且不需要增加額外的工藝步驟成為IC設(shè)計者主要考慮的問題。

2 ESD保護原理

ESD保護電路的設(shè)計目的就是要避免工作電路成為ESD的放電通路而遭到損害,保證在任意兩芯片引腳之間發(fā)生的ESD,都有適合的低阻旁路將ESD電流引入電源線。這個低阻旁路不但要能吸收ESD電流,還要能箝位工作電路的電壓,防止工作電路由于電壓過載而受損。在電路正常工作時,抗靜電結(jié)構(gòu)是不工作的,這使ESD保護電路還需要有很好的工作穩(wěn)定性,能在ESD發(fā)生時快速響應(yīng),在保護電路的同時,抗靜電結(jié)構(gòu)自身不能被損壞,抗靜電結(jié)構(gòu)的負作用(例如輸入延遲)必須在可以接受的范圍內(nèi),并防止抗靜電結(jié)構(gòu)發(fā)生閂鎖。

3 CMOS電路ESD保護結(jié)構(gòu)的設(shè)計

大部分的ESD電流來自電路外部,因此ESD保護電路一般設(shè)計在PAD旁,I/O電路內(nèi)部。典型的I/O電路由輸出驅(qū)動和輸入接收器兩部分組成。ESD 通過PAD導(dǎo)入芯片內(nèi)部,因此I/O里所有與PAD直接相連的器件都需要建立與之平行的ESD低阻旁路,將ESD電流引入電壓線,再由電壓線分布到芯片各個管腳,降低ESD的影響。具體到I/O電路,就是與PAD相連的輸出驅(qū)動和輸入接收器,必須保證在ESD發(fā)生時,形成與保護電路并行的低阻通路,旁路 ESD電流,且能立即有效地箝位保護電路電壓。而在這兩部分正常工作時,不影響電路的正常工作。

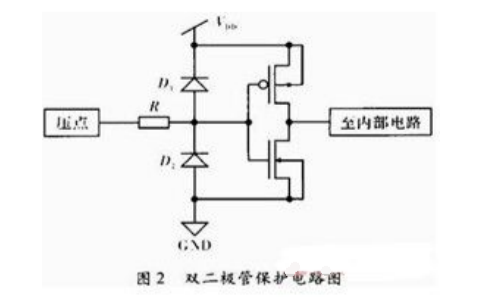

常用的ESD保護器件有電阻、二極管、雙極性晶體管、MOS管、可控硅等。由于MOS管與CMOS工藝兼容性好,因此常采用MOS管構(gòu)造保護電路。

CMOS工藝條件下的NMOS管有一個橫向寄生n-p-n(源極-p型襯底-漏極)晶體管,這個寄生的晶體管開啟時能吸收大量的電流。利用這一現(xiàn)象可在較小面積內(nèi)設(shè)計出較高ESD耐壓值的保護電路,其中最典型的器件結(jié)構(gòu)就是柵極接地NMOS(GGNMOS,GateGroundedNMOS)。

在正常工作情況下,NMOS橫向晶體管不會導(dǎo)通。當(dāng)ESD發(fā)生時,漏極和襯底的耗盡區(qū)將發(fā)生雪崩,并伴隨著電子空穴對的產(chǎn)生。一部分產(chǎn)生的空穴被源極吸收,其余的流過襯底。由于襯底電阻Rsub的存在,使襯底電壓提高。當(dāng)襯底和源之間的PN結(jié)正偏時,電子就從源發(fā)射進入襯底。這些電子在源漏之間電場的作用下,被加速,產(chǎn)生電子、空穴的碰撞電離,從而形成更多的電子空穴對,使流過n-p-n晶體管的電流不斷增加,最終使NMOS晶體管發(fā)生二次擊穿,此時的擊穿不再可逆,則NMOS管損壞。

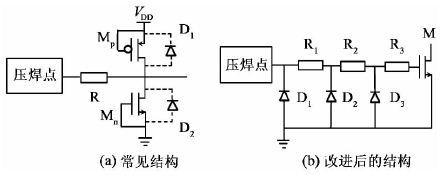

為了進一步降低輸出驅(qū)動上NMOS在ESD時兩端的電壓,可在ESD保護器件與GGNMOS之間加一個電阻。這個電阻不能影響工作信號,因此不能太大。畫版圖時通常采用多晶硅(poly)電阻。

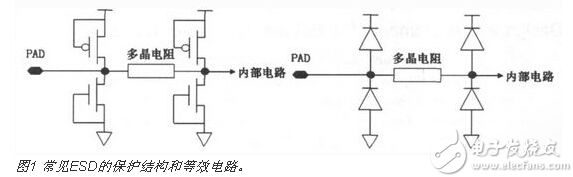

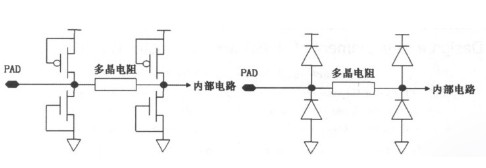

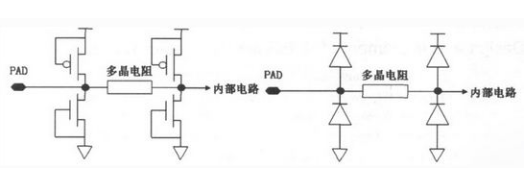

只采用一級ESD保護,在大ESD電流時,電路內(nèi)部的管子還是有可能被擊穿。GGNMOS導(dǎo)通,由于ESD電流很大,襯底和金屬連線上的電阻都不能忽略,此時GGNMOS并不能箝位住輸入接收端柵電壓,因為讓輸入接收端柵氧化硅層的電壓達到擊穿電壓的是GGNMOS與輸入接收端襯底間的IR壓降。為避免這種情況,可在輸入接收端附近加一個小尺寸GGNMOS進行二級ESD保護,用它來箝位輸入接收端柵電壓,如圖1所示。

在畫版圖時,必須注意將二級ESD保護電路緊靠輸入接收端,以減小輸入接收端與二級ESD保護電路之間襯底及其連線的電阻。為了在較小的面積內(nèi)畫出大尺寸的NMOS管子,在版圖中常把它畫成手指型,畫版圖時應(yīng)嚴格遵循I/OESD的設(shè)計規(guī)則。

如果PAD僅作為輸出,保護電阻和柵短接地的NMOS就不需要了,其輸出級大尺寸的PMOS和NMOS器件本身便可充當(dāng)ESD防護器件來用,一般輸出級都有雙保護環(huán),這樣可以防止發(fā)生閂鎖。

在全芯片的ESD結(jié)構(gòu)設(shè)計時,注意遵循以下原則:

(1)外圍VDD、VSS走線盡可能寬,減小走線上的電阻;

(2)設(shè)計一種 VDD-VSS之間的電壓箝位結(jié)構(gòu),且在發(fā)生ESD時能提供VDD-VSS直接低阻抗電流泄放通道。對于面積較大的電路,最好在芯片的四周各放置一個這樣的結(jié)構(gòu),若有可能,在芯片外圍放置多個VDD、VSS的PAD,也可以增強整體電路的抗ESD能力;

(3)外圍保護結(jié)構(gòu)的電源及地的走線盡量與內(nèi)部走線分開,外圍ESD保護結(jié)構(gòu)盡量做到均勻設(shè)計,避免版圖設(shè)計上出現(xiàn)ESD薄弱環(huán)節(jié);

(4)ESD保護結(jié)構(gòu)的設(shè)計要在電路的ESD性能、芯片面積、保護結(jié)構(gòu)對電路特性的影響如輸入信號完整性、電路速度、輸出驅(qū)動能力等進行平衡考慮設(shè)計,還需要考慮工藝的容差,使電路設(shè)計達到最優(yōu)化;

(5)在實際設(shè)計的一些電路中,有時沒有直接的VDD-VSS電壓箝位保護結(jié)構(gòu),此時,VDD-VSS之間的電壓箝位及ESD電流泄放主要利用全芯片整個電路的阱與襯底的接觸空間。所以在外圍電路要盡可能多地增加阱與襯底的接觸,且N+P+的間距一致。若有空間,則最好在VDD、VSS的PAD旁邊及四周增加VDD-VSS電壓箝位保護結(jié)構(gòu),這樣不僅增強了VDD-VSS模式下的抗ESD能力,也增強了I/O-I/O模式下的抗ESD能力。

一般只要有了上述的大致原則,在與芯片面積折中的考慮下,一般亞微米CMOS電路的抗ESD電壓可達到2500V以上,已經(jīng)可以滿足商用民品電路設(shè)計的ESD可靠性要求。

對于深亞微米超大規(guī)模CMOS IC的ESD結(jié)構(gòu)設(shè)計,常規(guī)的ESD保護結(jié)構(gòu)通常不再使用了,通常大多是深亞微米工藝的Foundry生產(chǎn)線都有自己外圍標準的ESD結(jié)構(gòu)提供,有嚴格標準的ESD結(jié)構(gòu)設(shè)計規(guī)則等,設(shè)計師只需調(diào)用其結(jié)構(gòu)就可以了,這可使芯片設(shè)計師把更多精力放在電路本身的功能、性能等方面的設(shè)計。

4 結(jié)束語

ESD保護設(shè)計隨著CMOS工藝水平的提高而越來越困難,ESD保護已經(jīng)不單是輸入腳或輸出腳的ESD保護設(shè)計問題,而是全芯片的靜電防護問題。

芯片里每一個I/O電路中都需要建立相應(yīng)的ESD保護電路,此外還要從整個芯片全盤考慮,采用整片(whole-chip)防護結(jié)構(gòu)是一個好的選擇,也能節(jié)省I/OPAD上ESD元件的面積。

-

CMOS

+關(guān)注

關(guān)注

58文章

5684瀏覽量

235148 -

ESD

+關(guān)注

關(guān)注

48文章

2012瀏覽量

172736

發(fā)布評論請先 登錄

相關(guān)推薦

亞微米CMOS電路中VDD-VSSESD保護結(jié)構(gòu)設(shè)計

CMOS電路中ESD保護結(jié)構(gòu)的設(shè)計要求

觸摸感應(yīng)電路中的ESD保護結(jié)構(gòu)設(shè)計方案

ESD(靜電放電)介紹及ESD保護電路的設(shè)計

如何設(shè)計ESD保護電路?

在I/O電路中ESD保護結(jié)構(gòu)的設(shè)計要求

CMOS工藝中GG2NMOS結(jié)構(gòu)ESD保護電路設(shè)計

CMOS電路中ESD保護結(jié)構(gòu)的設(shè)計

CMOS工藝中GG—NMOS結(jié)構(gòu)ESD保護電路設(shè)計

SCR器件在CMOS靜電保護電路中的應(yīng)用

基于CMOS電路的ESD保護設(shè)計

CMOS電路的ESD保護結(jié)構(gòu)設(shè)計

CMOS芯片的ESD保護電路設(shè)計

CMOS電路的ESD保護結(jié)構(gòu)設(shè)計資料下載

全面了解cmos電路中esd保護結(jié)構(gòu)原理及應(yīng)用

全面了解cmos電路中esd保護結(jié)構(gòu)原理及應(yīng)用

評論