最近一直在做嵌入式系統,畫原理圖。最后,為了保證原理圖準確無誤,檢查原理圖花費我近兩周的時間,在此,把我在檢查原理圖方面的心得體會總結在此,供大家參考,說得不對的地方歡迎大家指出。

往往我們畫完電路原理圖后,也知道要檢查檢查,但從哪些地方入手檢查呢?檢查原理圖需要注意哪些地方呢?下面聽我根據我的經驗一一道來。

1. 檢查所有的芯片封裝圖引腳是否有誤

當然,我指的是自己畫的芯片封裝。我在項目中曾經把一個芯片的2個引腳畫反了,導致最后制版出來后不得不跳線,這樣就很難看了。

所以,檢查與原理圖前一定要從芯片的封裝入手,堅決把錯誤的封裝扼殺在搖籃中!

2. 使用protel的Tools->ERC電氣規則檢查,根據其生成的文件來排錯

這個指的是protel99的ERC電氣規則檢查,DXP應該也會有相應的菜單可以完成這樣一個檢查。很有用,它可以幫你查找出很多錯誤,根據它生成的錯誤文件,對照著錯誤文件檢查一下你的原理圖,你應該會驚嘆:“我這么仔細地畫圖,竟然還會有這么多錯誤啊?”

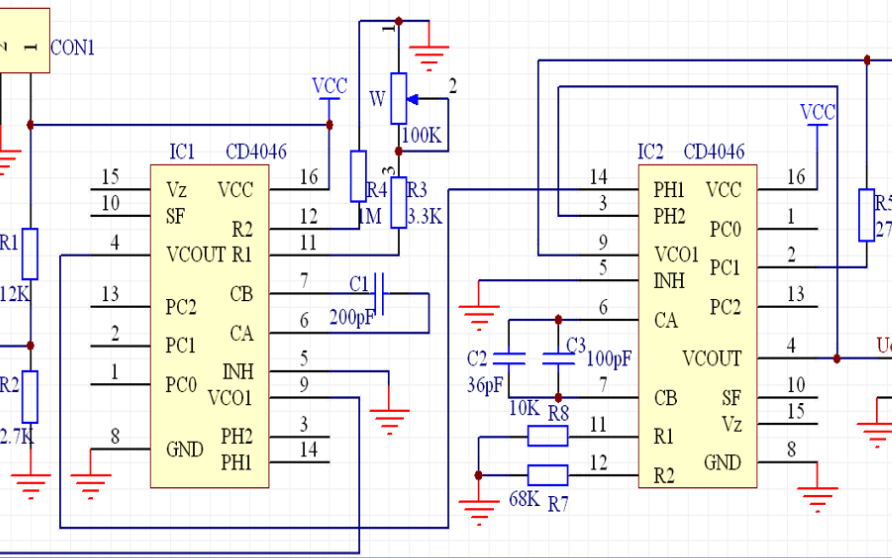

3. 檢測所有的網絡節點net是否都連接正確(重點)

一般容易出現的錯誤有:

(1) 本來兩個net是應該相連接的,卻不小心標得不一致,例如我曾經把主芯片的DDR時鐘腳標的是DDR_CLK,而把DDR芯片對應的時鐘腳標成了DDRCLK,由于名字不一致,其實這兩個腳是沒有連接在一起的。

(2) 有的net只標出了一個,該net的另一端在什么地方卻忘記標出。

(3) 同一個net標號有多個地方重復使用,導致它們全部連接到了一起。

4. 檢測各個芯片功能引腳是否都連接正確,檢測所有的芯片是否有遺漏引腳,不連接的劃X

芯片的功能引腳一定不要連錯,例如我使用的音頻處理芯片有LCLK、BCLK、MCLK三個時鐘引腳,與主芯片的三個音頻時鐘引腳一定要一一對應,連反一個就不能工作了。

是否有遺漏引腳其實很容易排查,仔細觀察各個芯片,看是否有沒有遺漏沒有連接出去的引腳,查查datasheet,看看該引腳什么功能,如果系統中不需要,就使用X把該引腳X掉。

5. 檢測所有的外接電容、電感、電阻的取值是否有根據,而不是隨意取值

其實新手在畫原理圖時,時常不清楚某些外圍電阻、電容怎么取值,這時千萬不要隨意取值,往往這些外圍電路電阻、電容的取值在芯片的datasheet上都有說明的,有的datasheet上也給出了典型參考電路,或者一些電阻電容的計算公式,只要你足夠細心,大部分電阻電容的取值你都是可以找到依據的。偶爾實在找不到依據的,可以在網上搜搜其他人的設計案例或者典型連接,參考一下。總之,不要隨意設置這些取值。

6. 檢查所有芯片供電端是否加了電容濾波

電源端的電容濾波的重要性就不用我多說了,其實做過硬件的人都應該知道。一般情況下,電路電源輸入端會引進一些紋波,為了防止這些紋波對芯片的邏輯造成太大的影響,往往需要在芯片供電端旁邊加上一些0.1uf之類的電容,起到一些濾波效果,檢查電路原理圖時,你可以仔細觀察一下是否在必要地芯片電源端加上了這樣的濾波電路呢?

7. 檢測系統所有的接口電路

接口電路一般包括系統的輸入和輸出,需要檢查輸入是否有應有的保護等,輸出是否有足夠的驅動能力等

輸出驅動能力不足的需要加上一些上拉電阻提高驅動能力。

8. 檢查各個芯片是否有上電、復位的先后順序要求,若有要求,則需要設計相應的時延電路

例如我項目中使用的DM6467芯片,對供電電壓的上電有先后順序要求,必須先給1.2V電源端供電,然后給1.8V電源端供電,最后給3.3V電源端供電。因此,我們將電源芯片產生的三種電壓通過一個時延芯片的處理(其實也可以使用一個三極管,利用鉗位電壓),然后再依次輸送到主芯片中。

9. 檢查各個芯片的地,該接模擬地的接模擬地,該接數字地的是否接的數字地,數字地與模擬地之間是否隔開

一般處理模擬信號的芯片有:傳感器芯片、模擬信號采集芯片、AD轉換芯片、功放芯片、濾波芯片、載波芯片、DA轉換芯片、模擬信號輸出芯片等等,往往只有當系統中存在這些處理模擬信號的芯片或者電路時才會涉及模擬地和數字地。

一般芯片的接地腳該連接模擬地還是數字地在芯片手冊中都有說明,按照datasheet上連接就可以了。

10. 觀察各個模塊是否有更優的解決方案(可選)

其實,剛剛設計原理圖初稿時,往往沒有想那么多,當整個系統成型后,你往往會發現其實很多地方是可以改進可以優化的。我們項目中的電源模塊前前后后改版了4次,每過一段時間往往又發現了更好的解決方案,現在的電源方案又簡潔又實用,效果也高很多,我想這就是不斷改進不斷優化的好處吧!

-

電路原理圖

+關注

關注

40文章

345瀏覽量

38272

原文標題:教你怎么檢查電路原理圖

文章出處:【微信號:wujianying_danpianji,微信公眾號:單片機精講吳鑒鷹】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

【畫板經驗9】如何檢查電路原理圖

PCB畫原理圖的十大注意事項

PCB設計七大步驟

設計完美PCB的七大步驟

Altium原理圖的編譯與檢查

【免費領取】運放十大經典電路(視頻21集)

運放十大經典電路(視頻21集)【免費領取!!】

protel 99 se原理圖設計步驟

常見led驅動電源電路設計大全(十款電路設計原理圖詳解)

電路原理圖檢查的十大步驟詳解

電路原理圖檢查的十大步驟詳解

評論