原型驗證是一種在FPGA平臺上驗證芯片設計的過程,通過在FPGA上實現芯片的設計原型,使得開發人員可以在硬件完成之前提前開始軟件開發和系統驗證。然而,如何快速確保在原型驗證平臺上開發的軟件能夠順利移植到最終芯片上,并完成"bring-up"(即系統啟動并正常運行),成為了開發團隊面臨的一個重要挑戰。

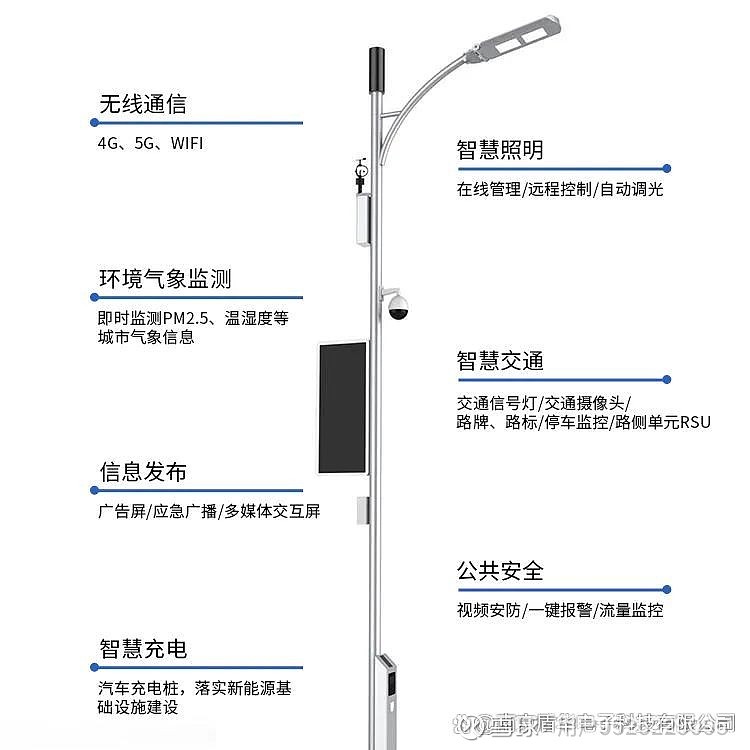

為了實現這一目標,雖然原型驗證具備高性能,能夠快速模擬真實芯片的運行環境,但要進一步滿足客戶對快速開發和驗證的需求,縮短開發周期,還必須依賴于靈活的子卡(Daughter Boards)、降速橋(Speed Bridge)方案、AXI協同仿真軟件以及優化的I/O分割(Partition)設計。這些工具不僅為軟件開發提供了真實的數據交互環境,還顯著加快了軟硬件的bring-up過程。因此,在選擇商用原型驗證平臺時,資源的多樣性與靈活性成為提升驗證效率的關鍵因素。

1. 如何快速進行原型設計?

在原型驗證過程中,"bring-up" 是一個關鍵階段,涉及一系列操作,從硬件配置、基本功能驗證到復雜系統的運行調試。這個過程不僅僅是硬件的連接和配置,還涉及到軟件的運行、設計加載、錯誤調試等多個步驟。最終的目標是確保系統能夠在預期的條件下順利運行,從而為進一步的功能測試和性能評估做好準備。

快速完成“bring-up”依賴于多個關鍵因素:

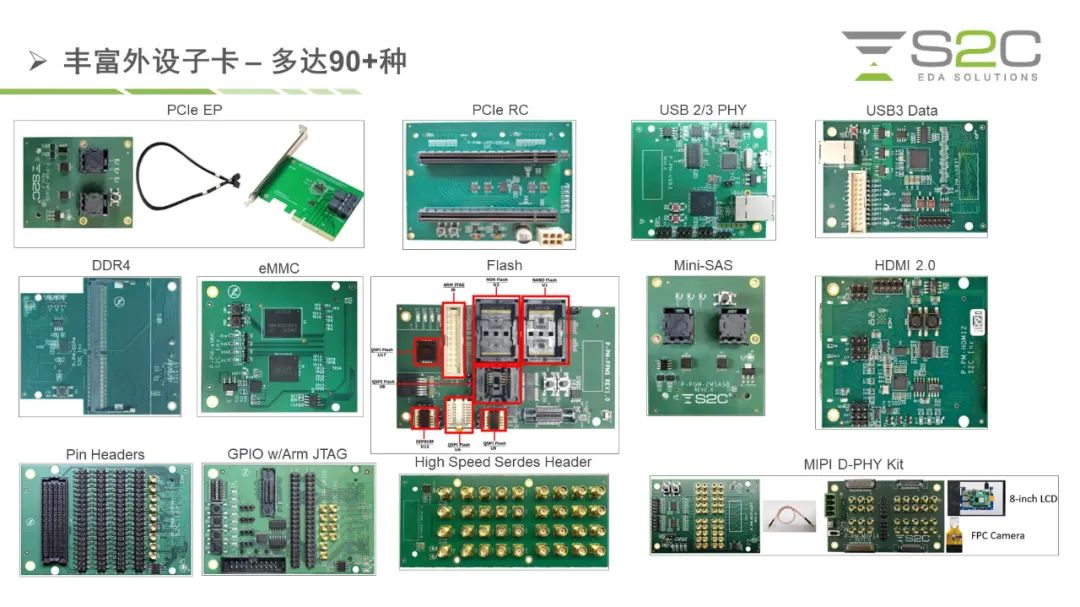

首先,靈活的接口方案對于快速部署至關重要,能夠支持與外部真實設備的連接。子卡是原型系統與外部設備交互的核心組件,它們支持多種通信協議,如MIPI、DDR4、PCIe等,滿足多種應用場景需求。通過靈活的子卡配置,開發團隊能夠根據項目需求,快速搭建符合真實使用環境的接口,加快系統驗證的進程。

降速橋以及相應的IP開發套件也是實現快速“bring-up”的關鍵。它能夠有效地協調高速與低速設備的通信,確保原型系統與外部設備之間的數據傳輸穩定流暢。降速橋的接口方案通過高效的數據轉接機制,保證了系統與實際應用環境之間的適配,并最大程度地提高了原型驗證系統的可靠性。

除了硬件支持外,AXI協同仿真軟件和參考設計也在快速部署中發揮了重要作用。AXI協同仿真軟件憑借其高效的數據傳輸和處理能力,幫助開發人員在接近真實芯片運行速度的環境中進行仿真和驗證。而參考設計提供了經過驗證的成熟解決方案,幫助開發團隊快速集成和驗證設計,從而減少從頭開發的時間和成本。這些工具和技術的結合,顯著提高了開發團隊的生產力,幫助他們在最短時間內達到驗證目標,并加速生成所需的波形數據(Fast Time to Waveform)。

此外,分割是大規模SoC設計中設計加載的核心挑戰之一。為了支持大規模設計,系統需要提供豐富的I/O接口以及高速SerDes接口,以實現分割后的互連和外設連接。

2. 芯神瞳Prodigy原型驗證

- 子卡:

子卡在原型系統與真實芯片環境之間提供了靈活的接口,能夠根據不同應用需求進行配置。子卡支持多種通信協議,滿足多媒體接口(如 MIPI)、SoC軟硬件協同(如 DDR4)、存儲(如 PCIe)和網絡接口等需求。這種靈活性確保了原型系統可以模擬真實使用環境的接口和帶寬要求,使得設計團隊能夠快速適配不同應用場景,加速原型系統的部署。

當前FPGA廠商提供的測試套件和內部FPGA板在應用上存在一定局限性。大多數評估板上的固定接口往往無法滿足SoC/ASIC原型驗證的需求,且難以在新項目中重復使用。這一限制同樣適用于許多自制的FPGA板。一些公司選擇自行開發(BYO)子卡接口,但這不僅增加了驗證接口正確性的難度,還可能在沒有現成子卡或設計的情況下,使快速部署變得十分困難,常常需要從頭設計或修改。這種開發成本和復用困難在激烈的市場競爭中往往會成為一大負擔。

思爾芯的芯神瞳 Prodigy 原型驗證解決方案為用戶提供了多種靈活的接口方案,包括豐富的外部子卡集合,涵蓋了多種模塊類別,包括 Arm 處理器接口模塊、嵌入式模塊、多媒體模塊等。這些模塊覆蓋了主流應用領域,經過市場驗證,用戶可以直接使用,避免了自行開發的復雜性和潛在風險。

這些預先測試過的廣泛子卡集合幫助用戶減少開發風險,能夠滿足當前芯片接口的行業標準,例如 USB、HDMI、PCIe、以太網和 DDR。以 Prodigy 三通道 RGMII/GMII PHY 接口模塊為例,通過嚴格的設計流程,確保子卡能夠在超過125MHz的頻率下穩定運行,支持千兆以太網的性能。自動檢測技術使全球團隊能夠遠程識別并測試子卡,同時集成的 IO 電壓檢測功能可以防止由于輸入錯誤電壓而導致的硬件損壞。

- 降速橋:

降速橋方案與相關IP模塊能夠有效協調數據傳輸,確保原型系統能夠與低速外部設備進行接口適配。通過靈活設計,降速橋IP支持高速傳輸協議的轉換,保證系統性能與實際應用環境一致。

在大規模復雜SoC設計中,高速接口IP(如PCIe Gen3/Gen4)在FPGA原型驗證階段往往由于工藝限制只能運行在較低速度,無法直接連接實際外部接口。因此,需要相應的高速接口降速橋方案進行適配。降速橋IP通常有兩種形式:基于硬件的降速橋和基于軟核IP的降速橋。思爾芯都有相應的解決方案。

此外,先進的Memory控制器IP(如LPDDR4/5,HBM2E/3)的驗證在FPGA原型系統中也是一大挑戰。由于這些控制器IP標準較新,主流FPGA供應商無法提供相應的PHY解決方案,導致這些IP在FPGA原型驗證系統中無法正常運行,思爾芯便為此提供了相應的解決方案。

例如,有客戶在設計中使用了LPDDR4 Memory控制器,但由于在原型驗證階段缺少基于FPGA的LPDDR4物理層IP,無法進行驗證。通過采用思爾芯提供的基于DFI接口的Memory控制器IP適配方案,客戶將LPDDR4控制器的讀寫操作通過DFI接口成功轉接到FPGA廠商的DDR4 Memory控制器上,順利完成了LPDDR4控制器的驗證。

- 調試時的AXI協同仿真:

基于 FPGA 的原型系統在運行速度和精度上接近流片后的實際芯片,對于芯片的完整功能性確認和早期軟件開發來說至關重要。然而,構建一個符合標準的原型驗證系統,需要豐富的專業知識、大量資源以及額外的硬件環境和互聯技術方案支持。

思爾芯的芯神瞳協同仿真軟件 ProtoBridge 通過采用廣泛使用的 AXI-4 總線協議以及獨有的專利技術,實現了設計到 FPGA 原型驗證環境的連接。通過高吞吐量的數據通道,ProtoBridge 實現了 FPGA 與 PC 主機之間的快速數據交互。使用這些工具,開發團隊可以在接近真實芯片速度的環境中進行早期的軟件調試和功能驗證,減少了芯片回片后的適配工作,顯著提升了設計移植的效率。

- 分割時的I/O優化:

在原型驗證中,系統需要提供豐富的I/O接口和高速SerDes接口,以支持分割(partition)互連及外設子卡的連接,確保高效的數據傳輸與系統協同工作。然而,分割過程往往是一個復雜且反復的迭代過程,涉及設計映射到設備的多次判斷和調整,必須從RTL或軟件中的錯誤中篩選并糾正映射錯誤。

思爾芯的芯神瞳 Player Pro – CompileTime(PPro-CT)工具為此提供了一種高效解決方案。它通過圖形化界面逐步引導用戶完成所有編譯步驟,并支持Tcl腳本模式下的自動ECO流程執行。尤其在I/O管腳分配方面,Player Pro 通過集成思爾芯子板I/O管腳對應關系的庫文件,自動匹配到I/O連接器,顯著提升了效率并減少了人為錯誤的可能性。

傳統I/O布局的局限性極大地限制了驗證系統的規模。為突破這一瓶頸,新一代的PPro-CT 具有SerDes的TDM模式,使級聯規模至少提升1倍,打破了I/O數量的限制,從而使更大規模的原型系統驗證成為可能。通過這一優化,開發團隊能夠更加靈活地處理復雜設計,并加速原型驗證進程。

3. 寫在最后

總的來說,快速原型設計依賴于多個關鍵因素的協調與整合。子卡與外部接口的搭配與數據交互是系統驗證的基礎,降速橋IP則通過高效的轉接性能實現不同設備間的協同工作。調試方面,思爾芯的 ProtoBridge 軟件通過軟硬件協同,確保了設計能夠在接近真實芯片的環境中進行調試與驗證。而在系統分割過程中,通過豐富的I/O接口和高速SerDes接口,保證了分割設計的有效互連與高效數據傳輸。這些要素的緊密配合,極大提升了系統的穩定性與部署效率,使得快速原型驗證成為可能。

而思爾芯為用戶提供了多種靈活的接口方案,包括豐富的外部子卡集合、降速橋方案、調試時需要的AXI協同仿真軟件,以及分割時I/O優化等,提供了超過90種不同子卡和配件,使得他們能夠更快速地搭建原型驗證環境并應對不同的項目需求。這些預先測試過的,并久經市場驗證的方案不僅幫助用戶減少開發風險,還能顯著減少開發工程資源,加速芯片設計的驗證與優化過程,從而在競爭激烈的市場中保持領先地位。

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602004 -

芯片

+關注

關注

454文章

50460瀏覽量

421960 -

原型驗證

+關注

關注

0文章

22瀏覽量

10727

發布評論請先 登錄

相關推薦

全方位解剖MOS管

FPGA算法工程師、邏輯工程師、原型驗證工程師有什么區別?

深度學習的模型優化與調試方法

FPB-RA2E3快速原型板的介紹和演示概述

快速部署原型驗證:從子卡到調試的全方位優化

快速部署原型驗證:從子卡到調試的全方位優化

評論