可測(cè)試性定義為:產(chǎn)品能及時(shí)準(zhǔn)確地確定其狀態(tài),隔離其內(nèi)部故障的設(shè)計(jì)特性,以提高產(chǎn)品可測(cè)試性為目的而進(jìn)行的設(shè)計(jì)被稱為可測(cè)試性設(shè)計(jì)。可測(cè)試性是同可靠性、維修性相并列的一門新型學(xué)科,其發(fā)展和應(yīng)用對(duì)于提高產(chǎn)品的質(zhì)量,降低產(chǎn)品的全壽命周期費(fèi)用具有重要意義。隨著集成電路設(shè)計(jì)方法與工藝技術(shù)的不斷進(jìn)步,集成電路的可測(cè)性已經(jīng)成為提高產(chǎn)品可靠性和成品率的重要因素。文中針對(duì)遙測(cè)產(chǎn)品中信號(hào)處理器的設(shè)計(jì)原理,通過(guò)增加BIT以提高信號(hào)處理器的測(cè)試覆蓋率。

1 信號(hào)處理器簡(jiǎn)介

硬件電路軟件化是電路設(shè)計(jì)的發(fā)展趨勢(shì)。借助大規(guī)模集成的FPGA和高效的設(shè)計(jì)軟件,不僅可通過(guò)直接對(duì)芯片結(jié)構(gòu)的設(shè)計(jì)實(shí)現(xiàn)多種數(shù)字邏輯系統(tǒng)功能,而且由于管腳定義靈活,從而減輕了信號(hào)處理器電路圖設(shè)計(jì)和電路板設(shè)計(jì)的工作量及難度。這種基于可編程邏輯器件的設(shè)計(jì)大幅減少了芯片的數(shù)量,縮小了系統(tǒng)的體積,提高了系統(tǒng)的可靠性,同時(shí)也增加了信號(hào)處理器的測(cè)試復(fù)雜度,降低了故障隔離率。

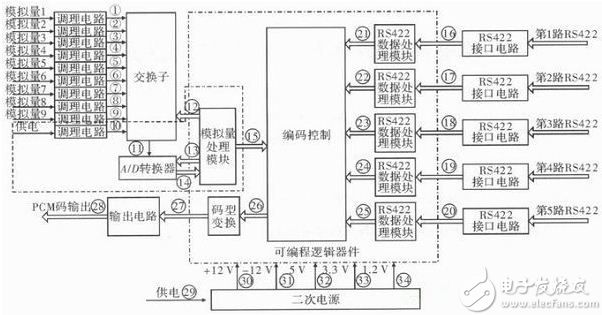

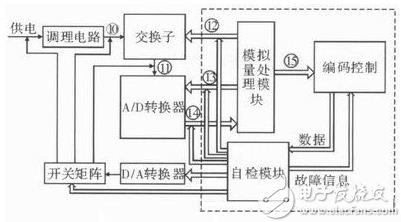

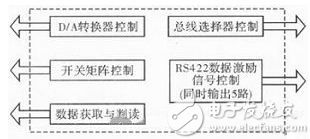

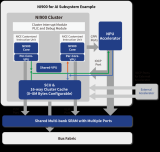

信號(hào)處理器主要完成電壓模擬信號(hào)的分時(shí)采集、RS422總線信號(hào)的接收和編碼輸出等功能,原理框圖如圖1所示。

圖1 信號(hào)處理器原理框圖

2 信號(hào)處理器測(cè)試現(xiàn)狀分析

信號(hào)處理器作為遙測(cè)產(chǎn)品的重要部件,其可測(cè)試性基本決定了遙測(cè)產(chǎn)品的可測(cè)試性,因此提高信號(hào)處理器的可測(cè)試性意義重大。由圖1可知信號(hào)處理器需要進(jìn)行測(cè)試的節(jié)點(diǎn)較多,主要包括多路模擬信號(hào)調(diào)理電路、交換子、A/D轉(zhuǎn)換器、RS422總線接口芯片、PCM碼輸出電路、FPGA內(nèi)部的各邏輯模塊、二次電源等,共計(jì)約34個(gè)測(cè)試節(jié)點(diǎn)。

在地面或試驗(yàn)室環(huán)境中,采用信號(hào)模擬器、萬(wàn)用表、示波器、數(shù)據(jù)接收設(shè)備等對(duì)信號(hào)處理器進(jìn)行測(cè)試,可以考核全部測(cè)試節(jié)點(diǎn),基本實(shí)現(xiàn)信號(hào)處理器100%的測(cè)試覆蓋率和故障隔離率。

在供電、二次電源變換以及PCM輸出正常的前提下,在掛機(jī)自檢過(guò)程中通過(guò)接收到的PCM數(shù)據(jù)僅可獲取部分模塊的工作狀態(tài),主要包括“供電”信號(hào)所在的調(diào)理電路、交換子、A/D轉(zhuǎn)換器、模擬量處理模塊和編碼控制模塊的部分功能,測(cè)試覆蓋率約為24%。當(dāng)4個(gè)單元中任意一個(gè)單元或多個(gè)單元出現(xiàn)故障時(shí),無(wú)法通過(guò)數(shù)據(jù)分析完成故障的進(jìn)一步隔離,從而形成一個(gè)模糊度為4的模糊組,故障隔離率0%。

3 BIT設(shè)計(jì)分析

3.1 單一模擬信號(hào)采集通路BIT分析

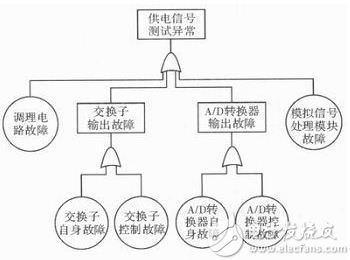

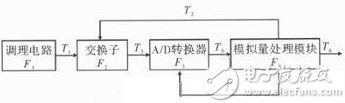

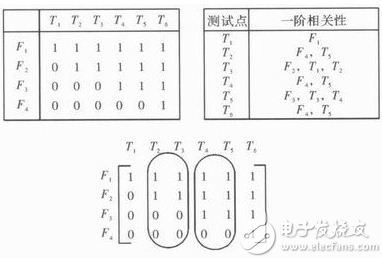

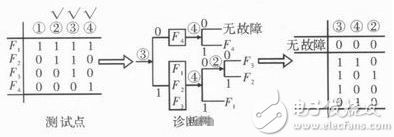

通過(guò)對(duì)圖1中雙點(diǎn)劃線部分電路進(jìn)行分析,建立故障樹如圖2所示,根據(jù)故障樹形成相關(guān)性圖形模型如圖3所示,獲得一階相關(guān)性及相關(guān)D矩陣如圖4所示。

圖2 故障樹

圖3 相關(guān)性圖形模型

圖4 一階相關(guān)性及相關(guān)D矩陣

圖5 診斷樹和故障字典

通過(guò)對(duì)D矩陣分析,識(shí)別冗余測(cè)試點(diǎn)和模糊組,完成檢測(cè)用測(cè)試點(diǎn)選擇,生成診斷樹和故障字典如圖5所示。

3.2 單一模擬信號(hào)采集通路的BIT設(shè)計(jì)

部分電路BIT分析是基于通過(guò)獲得測(cè)試點(diǎn)的狀態(tài)來(lái)識(shí)別故障和故障定位。根據(jù)信號(hào)處理器的特殊性,設(shè)計(jì)采用為電路各測(cè)試點(diǎn)引入激勵(lì)信號(hào)的方式,實(shí)現(xiàn)判斷功能模塊是否存在故障的功能,其BIT方案如圖6所示。

圖6 模擬信號(hào)BIT方案

在信號(hào)處理器上增加D/A轉(zhuǎn)換器電路和開關(guān)矩陣模塊,F(xiàn)PGA中增加自檢模塊;信號(hào)處理器加電時(shí),自檢模塊控制開關(guān)矩陣接入各測(cè)試點(diǎn),由D/A轉(zhuǎn)換器接入特定電壓值;通過(guò)比較電路最終測(cè)試返回值與引入值即可了解各模塊的狀態(tài)。以模擬信號(hào)“供電”測(cè)試通道為例說(shuō)明BIT工作流程。

(1)自檢模塊預(yù)設(shè)D/A輸出值為4 V.(2)通過(guò)開關(guān)矩陣將4 V電壓接入“供電”信號(hào)所在調(diào)理電路前端。(3)自檢模塊將通過(guò)A/D轉(zhuǎn)換器獲得的數(shù)據(jù)同預(yù)定值進(jìn)行比較。(4)如果比較結(jié)果一致,則輸出“000”表示無(wú)故障,自檢結(jié)束。(5)如果比較結(jié)果不一致,則控制開關(guān)矩陣將4 V電壓接入調(diào)理電路后端,即交換子前端,自檢模塊將通過(guò)A/D轉(zhuǎn)換器獲得的數(shù)據(jù)同預(yù)定值比較。(6)如果比較結(jié)果相一致,則輸出“110”表示調(diào)理電路故障,自檢結(jié)束。(7)如果比較結(jié)果不一致,則控制開關(guān)矩陣將4 V電壓接入交換子后端,即A/D轉(zhuǎn)換器前端,自檢模塊將通過(guò)A /D轉(zhuǎn)換器的獲得的數(shù)據(jù)同預(yù)定值進(jìn)行比較。(8)如果比較結(jié)果相一致,則輸出“101”表示交換子故障,自檢結(jié)束。(9)如果比較結(jié)果不一致,則通過(guò)“100”表示A/D轉(zhuǎn)換器故障,自檢結(jié)束。

此流程存在盲點(diǎn),即模擬信號(hào)處理模塊故障。因?yàn)樵摴收弦部赡軐?dǎo)致交換子輸出和A/D轉(zhuǎn)換器輸出故障,單一流程無(wú)法進(jìn)行識(shí)別和隔離。全部模擬通道均加入到此流程后,就可以通過(guò)多數(shù)原則判定和隔離上述故障。

3.3 RS422數(shù)據(jù)通道BIT設(shè)計(jì)

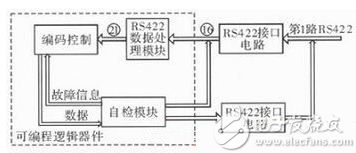

RS422數(shù)據(jù)接收只有兩級(jí)功能模塊,故障判定和隔離相對(duì)簡(jiǎn)單。只需要在FPGA中增加相應(yīng)數(shù)量的標(biāo)準(zhǔn)RS422總線數(shù)據(jù)流,通過(guò)RS422總線接口芯片、開關(guān)矩陣和總線選擇器接入RS422總線接口芯片輸入端或RS422數(shù)據(jù)處理模塊。RS422數(shù)據(jù)通道BIT方案如圖7所示。

圖7 RS422數(shù)據(jù)通道BIT方案

信號(hào)處理器加電后,自檢模塊首先發(fā)出預(yù)定格式的RS422信息,并控制開關(guān)矩陣切入RS422接口電路的輸入端,將接收到的數(shù)據(jù)同原始數(shù)據(jù)進(jìn)行比對(duì)。如果一致則代表無(wú)故障;否則,將預(yù)定數(shù)據(jù)通過(guò)總線選擇器切入RS422接口電路后端,再將收到的數(shù)據(jù)與預(yù)定數(shù)據(jù)比較,比對(duì)結(jié)果數(shù)據(jù)一致則RS422接口電路存在故障,反之RS422數(shù)據(jù)處理模塊故障,但不能同時(shí)識(shí)別RS422接口電路是否故障。

3.4 信號(hào)處理器整體BIT設(shè)計(jì)

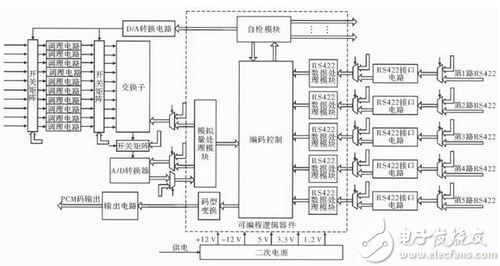

通過(guò)對(duì)單一模擬信號(hào)采集通道以及RS422數(shù)據(jù)通道的BIT設(shè)計(jì)實(shí)現(xiàn),最終信號(hào)處理器整體BIT設(shè)計(jì)結(jié)果如圖8所示。

圖8 信號(hào)處理器完善BIT后的設(shè)計(jì)框圖

自檢模塊為整個(gè)BIT設(shè)計(jì)的核心,自檢模塊需要控制D/A轉(zhuǎn)換、開關(guān)矩陣的切換、總線選擇器工作狀態(tài)、產(chǎn)生需要的激勵(lì)信號(hào)、完成數(shù)據(jù)判讀以及生成故障代碼。自檢模塊的功能框圖如圖9所示。

圖9 自檢模塊的功能框圖

4 結(jié)束語(yǔ)

信號(hào)處理器完善BIT設(shè)計(jì)后,在掛機(jī)自檢狀態(tài)測(cè)試覆蓋率接近100%。如果信號(hào)處理器只有單一故障發(fā)生,則故障隔離率高達(dá)100%;如果多個(gè)故障發(fā)生,則故障發(fā)生越靠近信號(hào)輸入前端,故障隔離率越高,反之越低,平均故障隔離率約為70%。總之,信號(hào)處理器在增加BIT后,在掛機(jī)自檢狀態(tài)下的測(cè)試覆蓋率和故障隔離率有較大提高。

-

AD

+關(guān)注

關(guān)注

27文章

868瀏覽量

150170 -

RS422

+關(guān)注

關(guān)注

4文章

78瀏覽量

36542 -

bit

+關(guān)注

關(guān)注

0文章

48瀏覽量

31990 -

遙測(cè)信號(hào)處理器

+關(guān)注

關(guān)注

0文章

1瀏覽量

4659

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

經(jīng)過(guò)TAS5548EVM評(píng)估板處理輸出的PWM信號(hào),可以用哪一款型號(hào)的數(shù)字功放評(píng)估板處理?

音頻信號(hào)處理器有哪些作用

支持K歌音箱方案應(yīng)用的高性能 32 位藍(lán)牙音頻應(yīng)用處理器-BP1048B2

投影融合處理器測(cè)試標(biāo)準(zhǔn)

全球首款生物處理器開放服務(wù),功耗號(hào)稱比傳統(tǒng)數(shù)字處理器低一百萬(wàn)倍

數(shù)字信號(hào)處理器的特點(diǎn)、作用及種類

英特爾Sierra Forest-SP處理器浮出水面,總緩存容量達(dá)180M

dsp和嵌入式微處理器的區(qū)別和聯(lián)系

一款以32位ARMCortexTM-M0處理器內(nèi)核為基礎(chǔ)的高性價(jià)比安全MCU

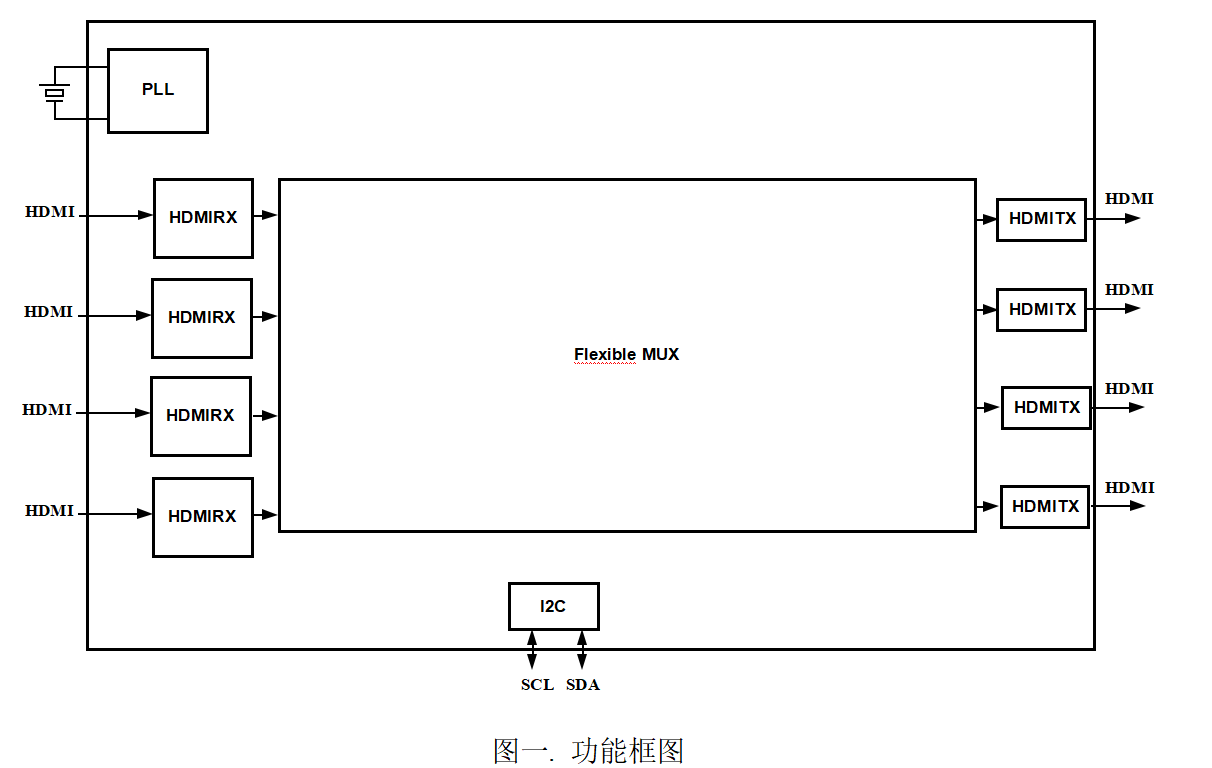

MS9604:一款 HDMI 視頻處理器,包含 4 路獨(dú)立 HDMI 音視頻輸入通道

芯來(lái)科技正式發(fā)布首款專用處理器產(chǎn)品線Nuclei Intelligence系列

簡(jiǎn)單認(rèn)識(shí)數(shù)字信號(hào)處理器

這是一款經(jīng)典的遙測(cè)信號(hào)處理器測(cè)試方案

這是一款經(jīng)典的遙測(cè)信號(hào)處理器測(cè)試方案

評(píng)論