對處于惡劣環境中的外部接口需要予以電流隔離,以增強安全性、功能性或是抗擾能力。這包括工業測量和控制所用數據采集模塊當中的模擬前端,以及處理節點之間的數字接口。

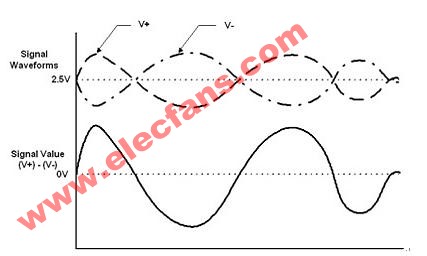

低壓差分信號傳輸(LVDS)是一種在更高性能轉換器和高帶寬FPGA或ASICI/O中常用的高速接口。差分信號傳輸對于外部電磁干擾(EMI)具有很強的抑制能力(因為反相與同相信號之間的互相耦合所致),同時也相應地可以將任何因為LVDS信號傳輸所造成的EMI最小化。在LVDS接口上增加隔離是一種透明解決方案,可以將其插入高速和精密測量以及控制應用的現有信號鏈當中。

當今有哪些選擇?

對于轉換器和處理器接口的電流隔離,同光耦合器相比,標準數字隔離器是快得多、魯棒且更為可靠的解決方案。然而,支持高速或精密轉換器的典型LVDS數據速率為數百Mbps,但最快速的標準數字隔離器最多支持150 Mbps。

為了支持更高帶寬的隔離,系統設計者當前已轉向定制化設計密集型解決方案,像是解串行化或利用變壓器、電容器的分離方案。這些方案會增加成本與設計時間,解串行化方案甚至可能需要外加一組簡單的FPGA,其目的僅僅是為了實現隔離功能。

變壓器和電容器需要對LVDS信號加以謹慎的信號調理,由此得到的應用和數據速率特定的解決方案將需要交流平衡編碼。進一步的解決方案是使用光纖通信鏈路,但考慮到成本和更高的復雜度,這更適合于數Gb的需求。圖1所示為高速隔離的各種方案選擇,以價值主張(依據設計的難易和成本)相對于方案的最大速度所繪制。

圖1. 隔離器實施的價值主張與隔離器速度的關系

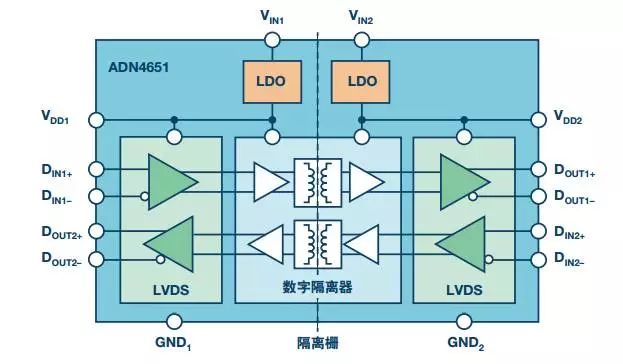

作為對比(如圖2所示),ADI公司已經推出了一系列直接可用的LVDS隔離器:ADN4650/ADN4651/ADN4652,采用針對高達600Mbps速率而增強的iCoupler?技術。

圖2. ADN4651600 Mbps LVDS隔離器框圖

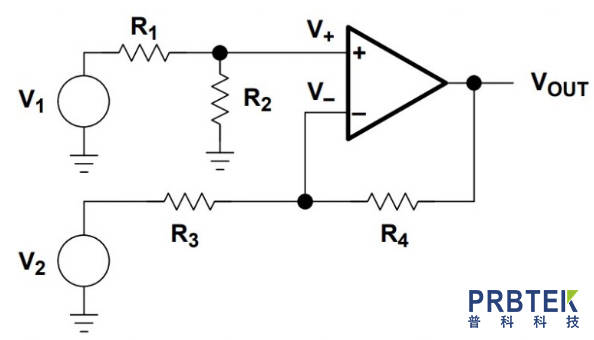

除了TIA/EIA-644-ALVDS兼容I/O之外,其完整的隔離器信號鏈是全差分式,實現了高抗擾能力及低輻射的解決方案。它提供兩個隔離式LVDS通道,一個發射一個接收(ADN4651,ADN4652相反),或是兩個發射或接收(ADN4650)。內部高速電路以2.5 V電壓工作,工業系統中可能沒有這種供電軌,因此其內置圖3所示的低壓差穩壓器(LDO)以支持單一寬體SOIC解決方案,即使采用3.3 V電源供電也無妨。

這些新型LVDS隔離器是否是直接可用的解決方案?

為了保證這些LVDS隔離器能夠插入轉換器至處理器的接口中,或是以高達600 Mbps運行的處理器內鏈路中,ADN465x系列有著超低抖動的精密時序。這點相當重要,因為在600 Mbps下,單位間隔(UI,例如位時間)只有1.6 ns,因此邊緣上的抖動必須非常小,以便接收器件有足夠的時間去對位進行采樣。ADN465x的典型總抖動為70 ps,或在600 Mbps下小于5% UI,假設誤碼率為1×10-12。

如何量化抖動?

查看抖動的最基本方法是用差分探針去測量LVDS信號對,并且上升沿和下降沿上均要觸發,示波器設定為無限持續。這意味著高至低和低至高的躍遷會相互迭加,因此可以測量交越點。交越寬度對應于峰峰值抖動或截至目前所測得的時間間隔誤差(TIE)(比較圖3所示的眼圖和直方圖)。有一些抖動是隨機來源(像是熱噪聲)所導致,此隨機抖動(RJ)意味著示波器上所看到的峰峰值抖動會受到運行時間的限制;隨著運行時間增加,直方圖上的尾巴會升高。

圖3a. ADN4651的眼圖

圖3b. ADN4651的直方圖

相比之下,確定性抖動(DJ)的來源是有界限的,例如脈沖偏斜所導致的抖動、數據速率相關抖動(DDJ)和符碼間干擾(ISI)。脈沖偏斜源于高至低與低至高傳播延遲之間的差異。這可以通過偏移交越實現可視化,即在0 V時,兩個邊沿分開(很容易通過圖3中直方圖內的分隔看出來)。DDJ源于不同工作頻率時的傳播延遲差異,而ISI源于前一躍遷頻率對當前躍遷的影響(邊沿時序在一連串的1秒或0秒與1010模式碼之后通常會有所不同)。

為了完整地估算特定誤碼率下的總抖動(TJ@BER),RJ與DJ可以依據測量得到的TIE分布所適配的模型來計算。此類模型中的一種是雙狄拉克模型,它假設高斯隨機分布與雙狄拉克δ函數卷積(兩個狄拉克δ函數之間的分隔距離對應于確定性抖動)。對于具有明顯確定性抖動的TIE分布而言,該分布在視覺上近似于此模型。有一項困難是某些確定性抖動會對高斯分量帶來影響,亦即雙狄拉克函數可能低估確定性抖動,高估隨機抖動。然而,兩者結合仍能精確估計特定誤碼率下的總抖動。

RJ規定為高斯分布模型中的1 σ rms值,若要推斷更長的運行長度(低BER),只需選擇適當的多σ,使其沿著分布的尾端移動足夠長的距離(1×10-12位錯誤需要14 σ)即可。接著加入DJ以提供TJ@BER的估計值。對于信號鏈中的多個元件,與其增加會導致高估抖動的多個TJ值,不如將RJ值進行幾何加總,將DJ值進行代數加總,這樣將能針對完整的信號鏈提供更為合理的完整TJ@BER估計。

ADN4651的RJ、DJ和TJ@BER全都是分別指定的,依據多個單元的統計分析提供各自的最大值,藉以確保這些抖動值在電源、溫度和工藝變化范圍內都能維持。

不同LVDS接口如何仰賴精密數據躍遷?

典型接收器可以容許10%至20% UI的抖動,舉例來說,利用ADN465x隔離外部LVDS端口將能使工業背板在PLC與I/O模塊間的纜線上安全地延伸。最大纜線距離取決于容許數據速率、纜線結構以及連接器類型,但在較低數據速率(例如200 Mbps)且使用高速連接器和適當的屏蔽雙絞線時,數米纜線長度是有可能實現的。

ADC接口通常利用LVDS進行信號源同步數據發送。這意味著LVDS時鐘會與其他LVDS通道上的一個或多個數據位流并行發送。ADN4650的低通道間和器件間偏斜(分別為≤300 ps和≤500 ps)對此很有利。這些偏斜值說明了多個通道上的高至低(或低至高)傳播延遲之間的最大差異,從統計意義上保證了所有ADN4650器件在電源、溫度和工藝變化范圍內的性能。在上升和下降時鐘沿上均進行數據傳輸以實現雙倍數據速率(DDR) 時(某些轉換器會利用DDR來提高輸出帶寬),≤100 ps的低脈沖偏斜支持時鐘同步。

ADC采樣時鐘可能需要加以隔離,以便將使用外部時鐘源的模擬前端成功地完全隔離;舉例來說,為一組多重數據采集通道同時提供時鐘信號。這對任何隔離器來說都是挑戰,因為時鐘上的任何抖動都會直接增加到孔徑抖動上,進而降低測量質量。同時鐘源一樣,LVDS信號鏈中用于時鐘分配的器件,例如扇出緩沖器,通常都會將此抖動規定為加性相位抖動。這意味著輸入時鐘的相位噪聲會與輸出時鐘的相位噪聲進行比較,并將其差值在相關頻率范圍(一般為12 kHz至20 MHz)上進行積分。

ADN465x系列本質上屬于集成隔離功能的LVDS緩沖器,所以同樣的觀點也適用于分析對ADC采樣的影響。使用ADN465x時,確保典型加性相位抖動只有376 fs,這樣即使增加電流隔離,也能維持原始測量質量,因為增加隔離可以消除處理器端數字電路中的噪聲。

在采樣時鐘被隔離的情況下,600 Mbps的無錯誤傳輸、與300 MHz時鐘同步以及最高ADC性能和分辨率,已經通過參考電路CN-0388中的AD7960(18位、5 MSPS、SAR ADC)加以驗證,如圖4所示。

圖4.用于AD7960和SDP-H1的ADN4651隔離電路

利用能夠透明隔離模擬前端的轉接卡,將ADC電路板與高速SDP-H1評估平臺之間的現有ADC評估平臺進行隔離。軟件沒有更動,利用精密模擬信號源對數據手冊規格所做的評估確認其具有與非隔離平臺相同的性能。

還有哪些應用可以使用LVDS隔離?

隔離式模擬前端或隔離式工業背板是兩個很有用的應用范例,可以很好地展示LVDS隔離所提供的機會,但此技術還有很多其他應用。送到平板顯示器的視頻信號通常使用LVDS信號,而HDMI?信號使用類似的差分信號共模邏輯(CML)。這些通常不需要隔離,但是對于醫療成像或工業PC中的外部顯示端口之類的應用而言,電流隔離可以保護人體或設備。

-

差分信號

+關注

關注

3文章

367瀏覽量

27658

原文標題:ADI深度丨五個問題,鬧明白低壓差分信號隔離那些事

文章出處:【微信號:analog_devices,微信公眾號:analog_devices】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

低壓差分信號隔離怎么整?這些技巧get到了就可以

低壓差分信號隔離怎么整?這些技巧get到了就可以

評論