X86架構(gòu)(The X86 architecture)是微處理器執(zhí)行的計(jì)算機(jī)語(yǔ)言指令集,指一個(gè)intel通用計(jì)算機(jī)系列的標(biāo)準(zhǔn)編號(hào)縮寫,也標(biāo)識(shí)一套通用的計(jì)算機(jī)指令集合。

x86是一個(gè)intel通用計(jì)算機(jī)系列的標(biāo)準(zhǔn)編號(hào)縮寫,也標(biāo)識(shí)一套通用的計(jì)算機(jī)指令集合,X與處理器沒有任何關(guān)系,它是一個(gè)對(duì)所有*86系統(tǒng)的簡(jiǎn)單的通配符定義,例如:i386, 586,奔騰(pentium)。由于早期intel的CPU編號(hào)都是如8086,80286來編號(hào),由于這整個(gè)系列的CPU都是指令兼容的,所以都用X86來標(biāo)識(shí)所使用的指令集合如今的奔騰,P2,P4,賽揚(yáng)系列都是支持X86指令系統(tǒng)的,所以都屬于X86家族 。

X86指令集是美國(guó)Intel公司為其第一塊16位CPU(i8086)專門開發(fā)的,美國(guó)IBM公司1981年推出的世界第一臺(tái)PC機(jī)中的CPU--i8088(i8086簡(jiǎn)化版)使用的也是X86指令,同時(shí)電腦中為提高浮點(diǎn)數(shù)據(jù)處理能力而增加的X87芯片系列數(shù)學(xué)協(xié)處理器則另外使用X87指令,以后就將X86指令集和X87指令集統(tǒng)稱為X86指令集。雖然隨著CPU技術(shù)的不斷發(fā)展,Intel陸續(xù)研制出更新型的i80386、i80486直到今天的Pentium 4(以下簡(jiǎn)為P4)系列,但為了保證電腦能繼續(xù)運(yùn)行以往開發(fā)的各類應(yīng)用程序以保護(hù)和繼承豐富的軟件資源,所以Intel公司所生產(chǎn)的所有CPU仍然繼續(xù)使用X86指令集,所以它的CPU仍屬于X86系列。

另外除Intel公司之外,AMD和Cyrix等廠家也相繼生產(chǎn)出能使用X86指令集的CPU,由于這些CPU能運(yùn)行所有的為Intel CPU所開發(fā)的各種軟件,所以電腦業(yè)內(nèi)人士就將這些CPU列為Intel的CPU兼容產(chǎn)品。由于Intel X86系列及其兼容CPU都使用X86指令集,所以就形成了今天龐大的X86系列及兼容CPU陣容。當(dāng)然在臺(tái)式(便攜式)電腦中并不都是使用X86系列CPU,部分服務(wù)器和蘋果(Macintosh)機(jī)中還使用美國(guó)DIGITAL(數(shù)字)公司的Alpha 61164和PowerPC 604e系列CPU。

Intel從8086開始,286、386、486、586、P1、P2、P3、P4都用的同一種CPU架構(gòu),統(tǒng)稱X86。

X86架構(gòu)CPU的邏輯原理

一、馮洛伊曼體系的運(yùn)作過程:

1、CPU的歷史就不扯了,有興趣的朋友可以網(wǎng)上搜一下。

2、X86CPU是基于馮洛伊曼架構(gòu)體系,所以大致上無非就這幾點(diǎn):

①、指令集和數(shù)據(jù)都用二進(jìn)制來表示,且混在一個(gè)存儲(chǔ)器。

②、計(jì)算機(jī)由運(yùn)算器、控制器、存儲(chǔ)器(cache)、輸入設(shè)備、輸出設(shè)備所組成。PS:cache不同于寄存器,寄存器是分布在控制器和運(yùn)算器里面的。

③、指令是一條接著一條順序的執(zhí)行。

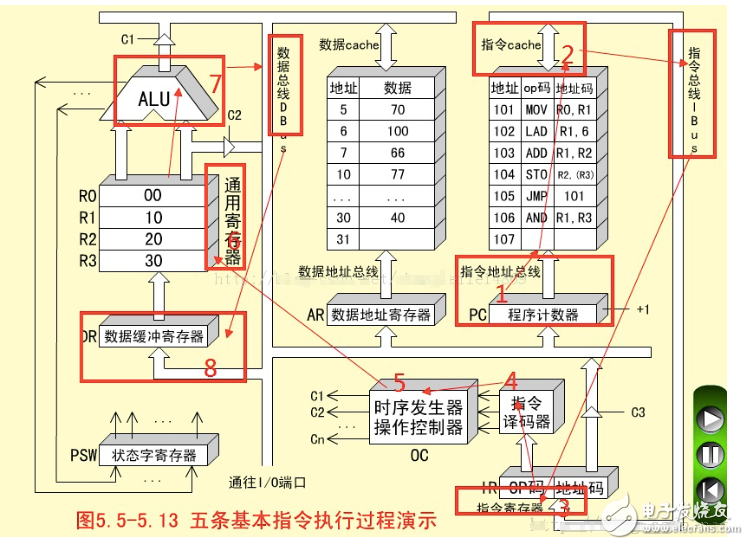

如下圖所示:

二、下面分別討論幾個(gè)主要組件:

寄存器:處于CPU存儲(chǔ)金字塔的最頂層,容量最小,速度最快(1-10個(gè)指令周期)。主要作用是用來存儲(chǔ)數(shù)據(jù)供運(yùn)算器運(yùn)算的。各自都有不同的功能。

控制器:數(shù)據(jù)寄存器,指令寄存器,程序計(jì)數(shù)器,指令譯碼器,時(shí)序產(chǎn)生器,操作控制器所組成。

運(yùn)算器:運(yùn)算器由算術(shù)邏輯單元(ALU)、累加寄存器、數(shù)據(jù)緩沖寄存器和狀態(tài)條件寄存器組成。

三、執(zhí)行過程:

當(dāng)執(zhí)行一條指令時(shí),程序計(jì)數(shù)器先記錄當(dāng)前的地址,把他放到地址記錄器,程序計(jì)數(shù)器再加一(指向下一條指令的地址),

然后就從內(nèi)存讀取指令放到指令寄存器(IR)。然后在傳到指令譯碼器,具體功能如下:

指令譯碼器:

(1)譯碼分析。確定指令應(yīng)完成的操作,產(chǎn)生相應(yīng)操作的控制電位。去參與形成該指令功能所需要的全部控制命令(微操作控制信號(hào))。

(2)根據(jù)尋址方式(8086是采用段地址+偏移地址合成一個(gè)20bit的尋址范圍,從32bit開始淘汰)的分析和指令功能要求,形成操作數(shù)的有效地址,并按此地址取出操作數(shù)(運(yùn)算型指令)或形成轉(zhuǎn)移地址(轉(zhuǎn)移類指令),以實(shí)現(xiàn)程序轉(zhuǎn)移。

指令寄存器中操作碼字段的輸出就是指令譯碼器的輸入。操作碼一經(jīng)譯碼后,即可向操作控制器發(fā)出具體操作的特定信號(hào)。

時(shí)序發(fā)生器: 時(shí)序信號(hào)發(fā)生器是產(chǎn)生指令周期控制時(shí)序信號(hào)的部件,當(dāng)CPU開始取指令并執(zhí)行指令時(shí),操作控制器利用時(shí)序信號(hào)發(fā)生器產(chǎn)生的定時(shí)脈沖的順序和不同的脈沖間隔,提供計(jì)算機(jī)各部分工作時(shí)所需的各種微操作定時(shí)控制信號(hào),有條理、有節(jié)奏地指揮機(jī)器各個(gè)部件按規(guī)定時(shí)間動(dòng)作。(區(qū)分?jǐn)?shù)據(jù)和指令的一種方法。詳細(xì)可看我CPU架構(gòu)的區(qū)別一文)

然后把指令傳到運(yùn)算器。寄存器得到譯碼后的結(jié)果,通過數(shù)據(jù)總線,去數(shù)據(jù)cache獲取數(shù)據(jù)。然后根據(jù)需求進(jìn)行邏輯運(yùn)算(與或非)算術(shù)運(yùn)算,然后在通過數(shù)據(jù)緩沖寄存器通往IO端口傳輸?shù)酵饨纭?/p>

操作控制器:常用的控制方式有同步控制、異步控制、聯(lián)合控制。

1.同步控制方式:任何指令的運(yùn)行或指令中各個(gè)微操作的執(zhí)行,均由確定的,具有統(tǒng)一基準(zhǔn)時(shí)標(biāo)的時(shí)序信號(hào)所控制。即所有的操作均由統(tǒng)一的時(shí)鐘控制,在標(biāo)準(zhǔn)時(shí)間內(nèi)完成。(在同步控制下,每個(gè)時(shí)序信號(hào)的結(jié)束就意味著安排完成的工作已經(jīng)完成,隨即開始執(zhí)行后續(xù)的微操作或自動(dòng)轉(zhuǎn)向下條指令的運(yùn)行。)

2.異步控制方式:沒有統(tǒng)一的同步信號(hào),采用問答方式進(jìn)行時(shí)序協(xié)調(diào),將前一操作的回答作為下一操作的啟動(dòng)信號(hào)。

3.聯(lián)合控制方式:將同步控制和異步控制相結(jié)合。其通常設(shè)計(jì)思想為:在功能部件內(nèi)部采用同步方式或以同步方式為主的控制方式;在功能部件間采用異步方式。

而運(yùn)算器又大致上分為邏輯運(yùn)算(與或非)和數(shù)值運(yùn)算(用加法的形式轉(zhuǎn)變成加減乘除)。

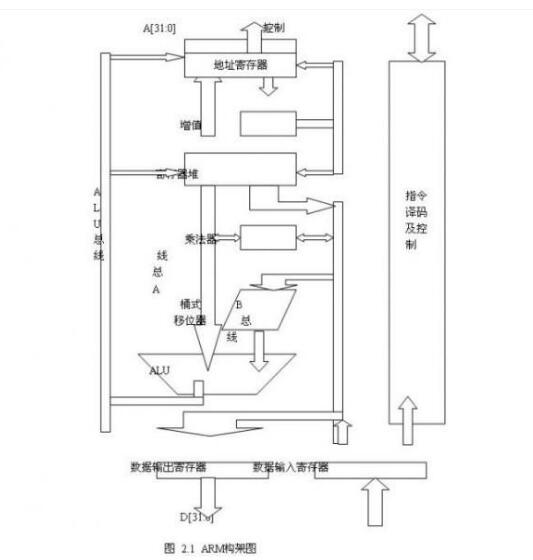

如下圖所示:

-

cpu

+關(guān)注

關(guān)注

68文章

10829瀏覽量

211193 -

微處理器

+關(guān)注

關(guān)注

11文章

2247瀏覽量

82331 -

X86架構(gòu)

+關(guān)注

關(guān)注

8文章

45瀏覽量

23637

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

[X86架構(gòu)和ARM架構(gòu),在工業(yè)領(lǐng)域的優(yōu)勢(shì)爭(zhēng)霸] X86與ARM誰更勝...

x86架構(gòu)和arm架構(gòu)的區(qū)別

適用于x86架構(gòu)的快速啟動(dòng)步驟是什么?

ARM架構(gòu)的系統(tǒng)與X86架構(gòu)系統(tǒng)的特性有什么不同?

Powerpc架構(gòu)與X86架構(gòu)的區(qū)別

x86架構(gòu)的最大特色在哪

arm架構(gòu)和x86架構(gòu)有什么區(qū)別

X86架構(gòu)和ARM架構(gòu)

X86架構(gòu)和ARM架構(gòu),在工業(yè)領(lǐng)域的優(yōu)勢(shì)爭(zhēng)霸

一文看懂a(chǎn)rm架構(gòu)和x86架構(gòu)有什么區(qū)別

X86架構(gòu)CPU的邏輯原理

X86架構(gòu)CPU的邏輯原理

評(píng)論