FPGA/CPLD器件的設計輸入有很多種方式,如繪制原理圖、編寫代碼或是調用IP核。早期的工程師對原理圖的設計方式情有獨鐘,這種輸入方式應付簡單的邏輯電路還湊合,應該算得上簡單實用,但隨著邏輯規模的不斷攀升,這種落后的設計方式已顯得力不從心。取而代之的是代碼輸入的方式,當今絕大多數的設計都采用代碼來完成。

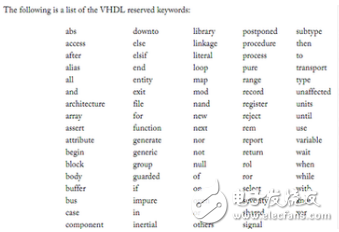

FPGA/CPLD開發所使用的代碼,我們通常稱之為硬件描述語言(Hardware Description Language),目前最主流的是VHDL和Verilog。VHDL發展較早,語法嚴謹;Verilog類似C語言,語法風格比較自由。IP核調用通常也是基于代碼設計輸入的基礎之上,今天很多EDA工具的供應商都在打FPGA/CPLD的如意算盤,FPGA/CPLD的設計也在朝著軟件化、平臺化的方向發展,也許在不久的將來,越來越多的工程只需要設計者從一個類似蘋果商店的IP核庫中索取組件進行配置,最后像搭積木一樣完成一個項目,或者整個設計都不需要見到一句代碼。當然了,未來什么情況都有可能發生,但是底層的代碼邏輯編寫方式無論如何還是有其生存空間的,畢竟一個個IP核組件都是從代碼開始的,所以對于初入這個行當的新手而言,掌握基本代碼設計的技能是必須的。

我們不過多談論VHDL和Verilog語言孰優孰劣,總之這兩種語言是當前業內絕大多數開發設計所使用的語言,從二者對電路的描述和實現上看,有許多相通之處。無論是VHDL還是Verilog,建議初學者先掌握其中一門,至于到底先下手哪一門,則需要讀者根據自身的情況做考量。對于沒有什么外部情況限制的朋友,若之前有一定的C語言基礎,不妨先學Verilog,這有助于加快對語法本身的理解。在將其中一門語言學精、用熟之后,最好也能夠著手掌握另一門語言。雖然在單個項目中,很少需要大家“雙語齊下”,但在實際工作中,還是很有可能需要去接觸另一門語法所寫的工程。網絡上有很多很好的開源實例,若你只會Verilog,而參考實例卻是VHDL的,那么就讓你很尷尬了;忽然有一天A同事離職,老板把他寫個半半的Verilog工程扔給只會VHDL的你維護,那你可就被動難堪了……所以嘛,對于VHDL和Verilog的取舍問題,建議先學精一門,也別忘了兼故另一門,無論哪一種語言,至少咱也要能看懂別人的設計。

HDL語言雖然和軟件語言有許多相似之處,但由于其實現對象是硬件電路,所以他們之間的設計思想存在較大差異。尤其是那些做過軟件編程的朋友,很喜歡用軟件的順序思想來駕驅HDL語言,豈不知HDL實現的硬件電路大都是并行處理的。也許就是這么個大彎轉不過來,所以很多朋友在研究HDL語言所實現的功能時常常百思不得其解。對于初學者,尤其是軟件轉行過來的初學者,筆者的建議是不要拋開實際電路而研究語法,在一段代碼過后,多花些精力比對實際邏輯電路,必要時做做仿真,最好能再找些直觀的外設在實驗板上看看結果。長此以往,若能達到代碼和電路都心中有數,那才證明真真正正掌握HDL語言的精髓了。

HDL語言的語法條目雖多,但并非所有的HDL語法都能夠實現到最終的硬件電路,由此進行劃分,可實現為硬件電路的語法我們常稱為可綜合的語法,而不能夠實現到硬件電路中,卻常常可作為仿真驗證的高層次語法我們則稱之為行為級語法。很多朋友在初學語法時,抱著一本語法書暈頭轉向的看,最后實戰的時候卻常常碰到這語法不能用那語法不支持的報錯信息,從而更加抱怨HDL不是好東西,學起來真困難。其實不然,可綜合的語法是一個很小的子集,對于初學者,建議先重點掌握好這個子集,實際設計中或許靠著10來條基本語法就可以打天下了,怎么樣?HDL語言一下變簡單了吧。這么說一點不夸張,本書的重點就是要通過各種可實現到板級的例程讓大家快速的掌握如何使用可綜合的語法子集完成一個設計。后面一節我們會將常用的可綜合語法子集逐一羅列并簡單介紹。

對于入了門的同學們,也不是說掌握了可綜合的語法子集就萬事大吉了,話說“革命尚未成功,同志還需努力”。行為級語法也非一無是處,都說“存在即是合理”,行為級語法也大有用處。一個稍微復雜的設計,若是在板級調試前不經過幾次三番的仿真測試,一次性成功的概率幾乎為零。而仿真驗證也有自己的一套高效便捷的語法,如果再像底層硬件電路一樣搭仿真平臺,恐怕就太浪費時間了。行為級語法最終的實現對象不是FPGA/CPLD器件,而是咱手中的電腦,動輒上G甚至雙核、四核的CPU可不愿做老牛拉破車的活,所以行為級語法幫助我們在仿真過程中利用好手中的資源,能夠快速、高效的完成設計的初期驗證平臺搭建。因此,掌握行為級的語法,可以服務于我們在設計的仿真驗證階段的工作。說多了,大家不要暈,本書重點在可綜合語法,也是初學者重點突擊方向,行為級語法是更高層次設計的追求,作為初學者,咱可以緩一緩,話說“先會走路再學飛”嘛。

對于HDL語言的學習,筆者根據自身的經驗,提幾點建議。

首先,手中需要準備一本比較完整的語法書籍,這類書市場上已經是滿天飛了,內容相差無幾,初學者最好能在在開始FPGA/CPLD的學習前花些時間認真的看過一遍語法,盡可能的理解每條語法的基本功能和用法。當然了,只需要大家認真看過、理解過,做到相關語法心中有數就行,咱也不是為了應付考試,也沒必要去死記硬背任何東西。語法的理論學習是必須的,能夠為后面的實踐打下堅實的基礎。有些實在不好理解的語法,也不要強求,今后在遇到類似語法在實例中的參考用法時再掌握不遲。

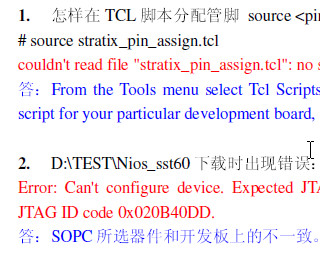

其次,參考一些簡單的例程,并且自己動手寫寫代碼實現相同或相近的電路功能。這個過程中可能需要結合實際的FPGA/CPLD開發工具和入門級學習套件。FPGA/CPLD的開發工具前面章節已經有所介紹,主要是掌握Quartus II(Altera公司的器件使用)或ISE(Xilinx公司的器件使用)的使用,學會使用這些工具新建一個工程、編寫代碼、分配管腳、進行編譯、下載配置文件到目標電路板中。入門級的學習套件,簡單的說,就是一塊板載FPGA/CPLD器件的電路板,這塊電路板不需要有很多高級的外設,一些簡單的常見外設即可(如蜂鳴器、流水燈、數碼管、UART、IIC等);一條下載線和相關的連接線。通過開發工具我們可以進行工程的建立和管理;而通過學習套件,我們就可以直觀的驗證工程是否實現了既定的功能。在實踐的過程中,大家一定要注意自己的代碼風格,當然了,這很大程度上取決于參考例程的代碼風格。至于什么樣的學習套件配套的參考例程是規范的,倒也沒有一個界定之說,在建議大家選擇口碑較好的學習套件的同時,也非常推薦大家多去讀讀FPGA/CPLD原廠Altare(qts_qii5v1.pdf)或Xilinx(xst.pdf)的官方文檔,在他們的一些文檔手冊中有各種常見電路的實現代碼風格和參考實例。在練習的過程中,大家也要學會使用開發工具生產的各種視圖,尤其是RTL視圖。RTL視圖是用戶輸入代碼進行綜合后的邏輯功能視圖,這個視圖很好的將用戶的代碼用邏輯門的方式詮釋出來,初學者可以通過查看RTL視圖的方式來看看自己寫的代碼所能實現的邏輯電路,以加深對語法的理解;反之,也可以通過RTL視圖來檢驗當前所寫的代碼是否實現了期望的功能。

總之,HDL語言的學習,簡單的歸納,就是需要初學者多看、多寫、多思考、多比對。

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602034 -

Verilog

+關注

關注

28文章

1345瀏覽量

109996 -

vhdl

+關注

關注

30文章

816瀏覽量

128082

原文標題:FPGA入門:Verilog/VHDL語法學習的經驗之談

文章出處:【微信號:gh_bee81f890fc1,微信公眾號:面包板社區】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

verilog語法學習心得

FPGA入門學習經驗總結(轉)

FPGA入門:Verilog/VHDL語法學習的經驗之談

FPGA實戰演練邏輯篇35:語法學習的經驗之談

勇敢的芯伴你玩轉Altera FPGA連載29:語法學習的經驗之談

掌握VHDL語法 ,VHDL語法學習筆記

Verilog代碼的基本程序框架

VHDL語法學習筆記

Verilog到VHDL轉換的經驗與技巧總結

Verilog/VHDL語法學習是掌握基本代碼設計的技能以及經驗總結

Verilog/VHDL語法學習是掌握基本代碼設計的技能以及經驗總結

評論