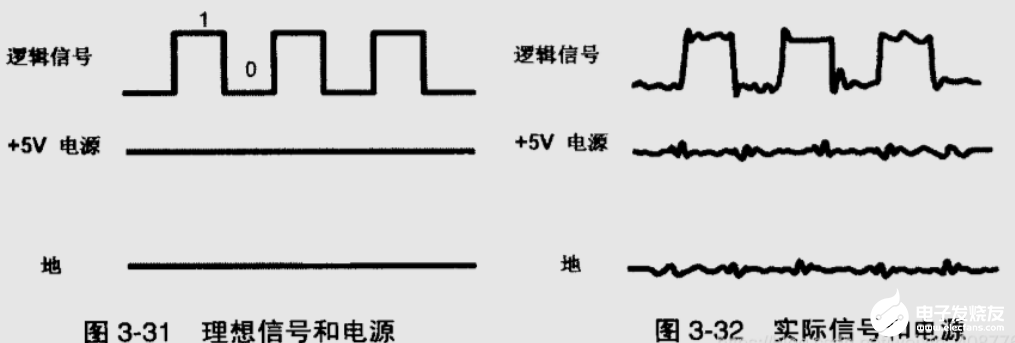

電源完整性是指電源波形的質量,研究的是電源分配網絡(PDN)。并從系統供電網絡綜合考慮,消除 / 降低噪聲對電源的影響。電源完整性的設計目標是把電源噪聲控制在運行的范圍內,為芯片提供干凈穩定的電壓,并使它能夠維持在一個很小的容差范圍內(通常為 5% 以內),實時響應負載對電流的快速變化,并能夠為其他信號提供低阻抗的回流路徑。

電源噪聲的主要來源:

走線的直流電阻與寄生電感

同步開關噪聲(SSN)

電源與地平面諧振噪聲

臨近電源網絡耦合噪聲

其他部件耦合噪聲

大量的芯片引腳在進行邏輯狀態切換時,會有一個大的瞬態電流流過回路,造成地平面的波動,會造成芯片的地與系統地不一致,稱為地彈;造成芯片和系統的電源有差壓,稱為電源彈。在進行 PCB 疊層設計時,盡可能增大電源平面疊層之間的垂直距離,減少電源平面和地平面之間的垂直間距。

電源完整性設計策略

關注過孔、走線和電源平面的通流能力;當在一個平面上布置多個電源時,需要進行電源平面的分割,分割方式要簡潔合理,分割區域的大小要滿足載流能力的要求;

盡可能使電源平面與地平面成對相鄰出現,且盡可能接近;

關注去耦電容的設計,電容的去耦作用是有一定的距離要求的,即去耦半徑。電容焊盤的扇出方式推薦采用多過孔的方式。

關注同步開關噪聲(SSN,地彈和電源彈)的影響,可增加去耦電容;在滿足系統整體性能需求前提下,盡可能使用平緩的驅動信號(減緩驅動器的上升沿和下降沿時間)

電源完整性的測試項目

電壓值(精度)

測試儀器:萬用表

測試方法:分別在測試空載 / 滿載下測試

合格標準:一般在標稱電壓值 ±5% 范圍內(根據芯片的電壓要求來確定)

電源噪聲 / 紋波

定義

紋波:出現在輸出端子間的一種與輸入頻率和開關頻率同步的成分,用有效值表示,一般在輸出電壓的 0.5% 以下

噪聲:出現在輸出端子間的紋波以外的一種高頻成分,也用峰 - 峰(peak to peak)值表示,一般在輸出電壓的 1% 以下

紋波噪聲:兩者合成,用峰 - 峰(peak to peak)值表示,要求一般在輸出電壓的 2% 以下

測試儀器:示波器

測試方法

分別在測試空載 / 滿載下測試

紋波:采用地線環靠接測量法(靠接測量),示波器設置帶寬(bandwidth)為 20MHz,直流偏置電壓(offset)為上面電壓精度測量值。

紋波噪聲:把示波器帶寬設置成全帶寬(Full)

測試點:輸出電容兩端

合格標準:

一般要求紋波 < 輸出電壓的 1%(在 20MHz 帶寬下測試,結果可視為單純的紋波)

一般要求紋波噪聲 < 輸出電壓的 2%(在全帶寬下測試,結果可視為紋波 + 噪聲)

注意事項

測試時注意就近原則,保持地環線最短

測試使用無源探頭

測試紋波時記錄其頻率,以便分析

電壓上下電波形

測試儀器:示波器

測試方法:示波器設置為上升 / 下降沿觸發,開關電源觀察上下電波形,能完整顯示出來以看出問題

測試點:電源芯片的輸出管腳、系統上的電源線

合格標準

電源輸出端電壓上下電過沖一般要求不超過被測電壓的 10%。在芯片前端測試時,可參考電平通用標準

電源上電時電壓不得有很大的跌落,下電時不能有很大的反沖和回勾(跌落和反沖不能跨越芯片啟動工作電壓),如出現臺階現象需要評估影響。

如果出現負電壓,就需要結合實際情況討論

注意芯片的上下電時序要求

注意事項:需要遍歷系統上下電、單板插拔、電源板插拔的情況

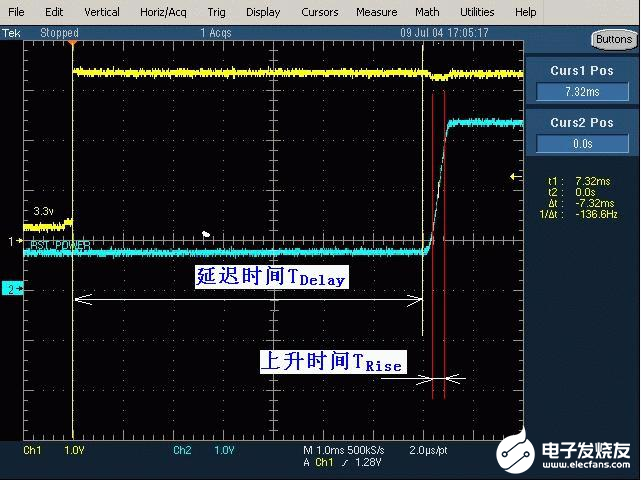

緩啟動電路參數

測試儀器:示波器

測試方法:使用多通道測試,上電觀察時間差

測試點:一路在緩啟動之前的電路,一路在緩啟動之后

合格標準

延遲時間(??????):一般要求其范圍 20 ~ 200ms

上升時間(?????,輸出電壓從 10% 上升到 90% 的時間):要求其范圍越小越好,但同時要求沖擊電流滿足合格標準

沒有多次振蕩現象

注意事項:需要遍歷系統上下電、單板插拔、電源板插拔的情況

電源電流和沖擊電流

測試儀器:示波器

測試方法:

電源電流:使用電流探頭,觀察電源上電電流波形和上電后電流的平穩波形

沖擊電流:同上。上電沖擊電流最好在冷機時測試(沖擊電流最大);下電沖擊電流最好在單板滿載時進行

測試點:將電流探頭卡在被測試電流通路上

合格標準

電源電流穩定值不能超過 90% 最大額定輸出電流

沖擊電流值不能超過額定輸出電流的 5 倍(3 倍以上應引起注意)

任何情況下的電流一定要大于電源的最小負載,且須滿足最大容性負載要求

注意事項

需要遍歷系統上下電、單板插拔、電源板插拔的情況

測試沖擊電流,需要取下感性元件如電感,因為感性器件本身具有抑制沖擊電流的作用。

電源告警信號

測試方法:使系統產生告警條件,測試告警信號的電平大小

測試點:告警信號的接收末端

合格標準:參考電源芯片的規格書

冗余電源的均流參數

測試方法:用測試電源輸出電流的方法,測試冗余電源的每路電流的輸出值,比較每路輸出電流的大小

測試點:冗余電源的每路電流輸出鏈路

合格標準:系統電源、其冗余電源(均流)的各路電流輸出值相差 10% 以下

-

電源

+關注

關注

184文章

17605瀏覽量

249557 -

電源完整性

+關注

關注

9文章

209瀏覽量

20708 -

PDN

+關注

關注

0文章

83瀏覽量

22688 -

電源分配網絡

+關注

關注

0文章

14瀏覽量

8383

發布評論請先 登錄

相關推薦

信號完整性與電源完整性的仿真分析與設計

信號完整性為什么寫電源完整性?

高速PCB電源完整性設計與分析

大話電源完整性

電源完整性設計【硬件干貨】

電源完整性設計【硬件干貨】

評論