在PCB(印刷電路板)設計中,降低電磁兼容性(EMC)問題是一個至關重要的環節。EMC問題主要涉及電磁干擾(EMI)和電磁敏感度(EMS)兩個方面,其中EMI是指設備或系統在其正常工作過程中產生的電磁場對其他設備或系統造成的干擾,而EMS則是指設備或系統對外部電磁場的敏感程度。以下將從多個方面詳細探討在PCB設計中如何有效降低EMC問題。

一、接地設計

- 設計PCB接地層

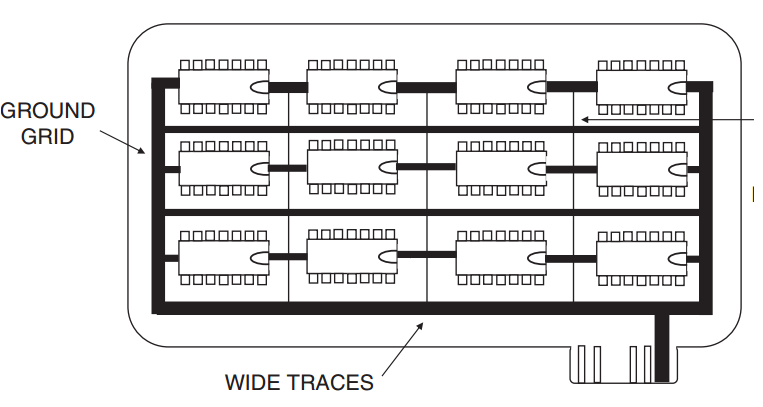

- 降低EMI的一個重要途徑是設計PCB接地層。應使PCB電路板總面積內的接地面積盡可能大,以減少發射、串擾和噪聲。

- 將每個元器件連接到接地點或接地層時必須特別小心,以確保充分利用可靠的接地層的中和效果。

- 理想情況下,每個參考電壓都有自己對應的接地層。然而,接地層過多會增加PCB的制造成本。折衷的辦法是在三到五個不同的位置分別使用接地層,每一個接地層可包含多個接地部分,以控制成本并降低EMI和EMC。

- 低阻抗接地系統

- 模擬與數字電路分開接地

- 模擬電路的安培數較高或電流較大,應遠離高速走線或開關信號。如果可能,應使用接地信號保護它們。

- 在多層PCB上,模擬走線的布線應在一個接地層上,而開關走線或高速走線應在另一個接地層上,以分開不同特性的信號。

二、走線設計

- 走線長度與返回路徑

- 向/從信號源傳輸電流的走線應盡可能短,以避免源路徑和返回路徑長度不相等導致的接地反彈和EMI。

- 返回路徑走線的長度應與發送走線的長度相同,以減少串擾和EMI。

- 并行走線處理

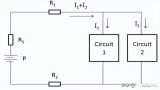

- 兩個并行的高速信號會產生EMC和EMI,特別是串擾。應使電阻路徑最短,并使返回電流路徑也盡可能短。

- 如果使并行走線之間的寬度為走線寬度的兩倍,則串擾的影響可降至最低。例如,走線寬度為5密耳時,兩條并行走線之間的最小距離應為10密耳或更大。

- 避免直角走線

- 直角走線會產生輻射,增加電容和特性阻抗的變化,導致反射和EMI。因此,走線應避免90°角,而應至少以兩個45°角布線到拐角處。

- 關鍵信號的帶狀線布局

- 對于關鍵信號,應采用帶狀線布局,以提供更好的電磁屏蔽和降低串擾。

三、電源與接地平面設計

- 電源與接地面相鄰

- 將電源和接地面盡可能地放在相鄰的層上,以減少電磁干擾。

- 平行電源和地平面對

- 使用盡可能多的平行電源和地平面對,以增強電磁屏蔽效果。

- 電源平面邊緣內縮

- 電源平面邊緣應內縮,以小于接地平面的尺寸,并沿邊緣在接地平面之間通孔互連,以減少電磁泄漏。

四、元器件布局與布線

- 元器件分組與濾波

- PCB上的組件應根據功能進行分組,每個組件的信號走線必須保持在定義的區域內。

- 當信號需要從一個子系統連接到另一個子系統時,可以使用濾波器來減少電磁干擾。

- 高速信號與接地層鄰近

- 在高速情況下,信號和時鐘應盡可能短并鄰近接地層,以控制串擾、噪聲和輻射。

- 數字信號與電源平面的距離

- 數字信號應遠離電源平面,以減少噪聲和感應,從而保持信號強度。

五、去耦電容與濾波器的使用

- 去耦電容的放置

- 去耦電容可減少串擾的不良影響,應位于設備的電源引腳和接地引腳之間,以確保交流阻抗較低。

- 為了在寬頻率范圍內實現低阻抗,應使用多個去耦電容。電容值最小的電容器要盡可能靠近設備,以減少對走線產生電感影響。

- 濾波器的應用

- 有時可以用一個低通濾波器來消除與周圍走線耦合的高頻噪聲。濾波器可以抑制噪聲,返回穩定的電流。

- 所有外部I/O信號應進行低通濾波,使用可容忍的最長信號上升時間,以減少電磁干擾。

六、差分信號與對稱設計

- 差分信號的走線設計

- 盡量減少每對差分線之間的非對稱現象,以保持信號的完整性并減少電磁干擾。

- 對稱布局

- 在PCB布局中,應保持對稱布局,以減少電磁場的不均勻分布和降低EMI。

七、物理屏蔽與接地

- 物理屏蔽的使用

- 使用金屬封裝包住整個或部分系統,以防止EMI進入PCB電路。這種屏蔽像是封閉的接地導電容器,可減小天線環路尺寸并吸收EMI。

- 屏蔽層與金屬機殼的接觸

- 連接屏蔽電纜時,盡量保障屏蔽層和金屬機殼之間的接觸完整,將屏蔽作為外殼的延伸。

- 避免使用“豬尾巴”辮線用于線纜屏蔽層和金屬機殼之間的連接,以減少電磁泄漏。

八、其他設計考慮

- 了解電路板的諧振頻率

- 如果存在與使用時鐘信號重疊的諧波,嘗試改變封裝的幾何形狀,以消除該諧波,從而減少EMI。

- 避免信號參考不同的電源平面層

- 信號應盡可能在同一電源平面層上傳輸,以減少不同電源平面層之間的電磁干擾。

- 合理使用磁珠

- 磁珠可用于消除表層諧振,特別是在高頻應用中。它們可用于抑制高頻噪聲,并吸收電磁干擾。

- 跨板設計的處理

- 在PCB跨板設計時,應在連接處使用共模電感,以減少電磁干擾的傳播。

- 外接線纜的處理

- 外接線纜時,在線纜上使用共模電感或者扼流圈,以減少電磁干擾的輻射和接收。

- 孔縫設計

- PCB設計不能破壞金屬機殼的完整性。孔縫的設計應使其最大尺寸明顯小于可能泄漏的最低頻率輻射的波長,以減少電磁泄漏。

- 數量多而尺寸小的孔縫設計通常比數量少而尺寸大的孔縫設計具有更好的屏蔽效果。

九、信號完整性考量

在PCB設計中,信號完整性(Signal Integrity, SI)與EMC問題密切相關。確保信號的完整性不僅可以提高系統的性能,還能有效降低電磁干擾。

- 阻抗匹配

- 阻抗匹配是確保信號在傳輸線上不產生反射的關鍵。傳輸線的阻抗應與源和負載的阻抗相匹配,以減少信號的損失和反射。

- 在PCB設計中,可以通過選擇合適的走線寬度、介質厚度和介電常數來實現阻抗匹配。

- 減少傳輸線效應

- 傳輸線效應,如延遲、衰減和色散,會對信號的完整性產生負面影響。在高速信號傳輸中,這些效應尤為明顯。

- 通過縮短傳輸線長度、使用低損耗材料和增加傳輸線的寬度,可以減少這些效應的影響。

- 避免信號間的串擾

- 串擾是信號完整性問題的常見來源,它會導致信號失真和誤碼率增加。

- 在PCB設計中,可以通過增加走線間距、使用差分信號和屏蔽技術來減少串擾。

- 終端電阻的使用

- 在某些情況下,使用終端電阻可以幫助吸收反射波,從而改善信號的完整性。

- 終端電阻的選擇應基于傳輸線的阻抗和信號的特性。

十、電源管理

電源管理對于降低EMC問題同樣至關重要。不穩定的電源會導致電壓波動和噪聲,進而增加電磁干擾。

- 電源去耦

- 電源去耦是減少電源噪聲的有效方法。通過在電源引腳附近放置去耦電容,可以吸收電源線上的高頻噪聲。

- 去耦電容的選擇應基于電源噪聲的頻率特性和電容的阻抗特性。

- 電源濾波

- 電源濾波是另一種減少電源噪聲的方法。通過在電源線上添加濾波器,可以濾除不需要的高頻成分。

- 濾波器的設計應基于電源噪聲的頻率特性和系統的性能要求。

- 電源完整性

- 電源完整性(Power Integrity, PI)是指電源在系統中的穩定性和可靠性。確保電源完整性可以降低電磁干擾并提高系統的性能。

- 在PCB設計中,可以通過優化電源布局、使用低阻抗電源平面和增加電源去耦電容來提高電源完整性。

十一、軟件層面的優化

雖然本文主要討論的是PCB設計中的硬件層面優化,但軟件層面的優化同樣重要。通過軟件層面的優化,可以進一步降低EMC問題。

- 時鐘頻率的選擇

- 時鐘頻率是電磁干擾的主要來源之一。通過選擇較低的時鐘頻率,可以減少電磁輻射和接收。

- 在可能的情況下,可以使用分頻器或鎖相環(PLL)來降低時鐘頻率。

- 信號編碼與調制

- 使用適當的信號編碼和調制技術可以減少電磁干擾。例如,差分信號編碼和擴頻調制都可以降低電磁輻射。

- 軟件濾波

- 在軟件層面添加濾波器可以進一步減少噪聲和電磁干擾。例如,可以使用數字濾波器來平滑信號并去除高頻噪聲。

十二、測試與驗證

在PCB設計完成后,進行測試與驗證是確保EMC性能的關鍵步驟。通過測試,可以發現潛在的問題并進行修正。

- EMC測試

- 進行EMC測試是驗證PCB設計是否符合相關標準和法規的必要步驟。測試包括輻射發射測試和傳導發射測試等。

- 根據測試結果,可以對PCB設計進行調整和優化,以降低電磁干擾。

- 信號完整性測試

- 信號完整性測試是驗證信號在PCB上傳輸過程中是否保持完整性的關鍵步驟。測試包括時域反射測試(TDR)和眼圖測試等。

- 通過信號完整性測試,可以發現潛在的信號傳輸問題并進行修正。

- 熱測試

- 熱測試是驗證PCB在正常工作過程中是否會產生過熱問題的關鍵步驟。過熱會導致電磁干擾增加和元件失效。

- 通過熱測試,可以發現潛在的散熱問題并進行修正,以確保PCB的可靠性和穩定性。

十三、總結與最佳實踐

在PCB設計中降低EMC需要綜合考慮多個方面,包括接地設計、走線設計、電源與接地平面設計、元器件布局與布線、去耦電容與濾波器的使用、差分信號與對稱設計、物理屏蔽與接地以及其他設計考慮。通過遵循以下最佳實踐,可以顯著降低EMC問題:

- 最大化接地面積,使用低阻抗接地系統。

- 保持走線長度一致,避免直角走線。

- 將電源和接地面相鄰放置,使用平行電源和地平面對。

- 根據功能分組元器件,使用濾波器減少電磁干擾。

- 放置去耦電容,確保交流阻抗較低。

- 盡量減少差分線之間的非對稱現象。

- 使用物理屏蔽防止EMI進入PCB電路。

- 了解并避免電路板的諧振頻率。

- 合理使用磁珠和共模電感抑制高頻噪聲。

- 在跨板設計和外接線纜時使用共模電感或扼流圈。

- 設計孔縫時確保其尺寸小于最低頻率輻射的波長。

綜上所述,通過綜合運用這些最佳實踐,可以顯著提高PCB的EMC性能,降低電磁干擾和電磁敏感度,從而確保設備的可靠性和穩定性。

-

電路板

+關注

關注

140文章

4911瀏覽量

97453 -

emc

+關注

關注

169文章

3884瀏覽量

182891 -

PCB

+關注

關注

1文章

1777瀏覽量

13204

發布評論請先 登錄

相關推薦

PCB設計中EMC/EMI的仿真

EMC之PCB設計技巧

PCB設計考慮EMC的接地技巧

PCB設計中的EMC概念

PCB設計中怎么降低EMC

PCB設計中怎么降低EMC

評論