IC前端設計(邏輯設計)和后端設計(物理設計)的區分:

以設計是否與工藝有關來區分二者;從設計程度上來講,前端設計的結果就是得到了芯片的門級網表電路。

前端設計的流程及使用的EDA工具

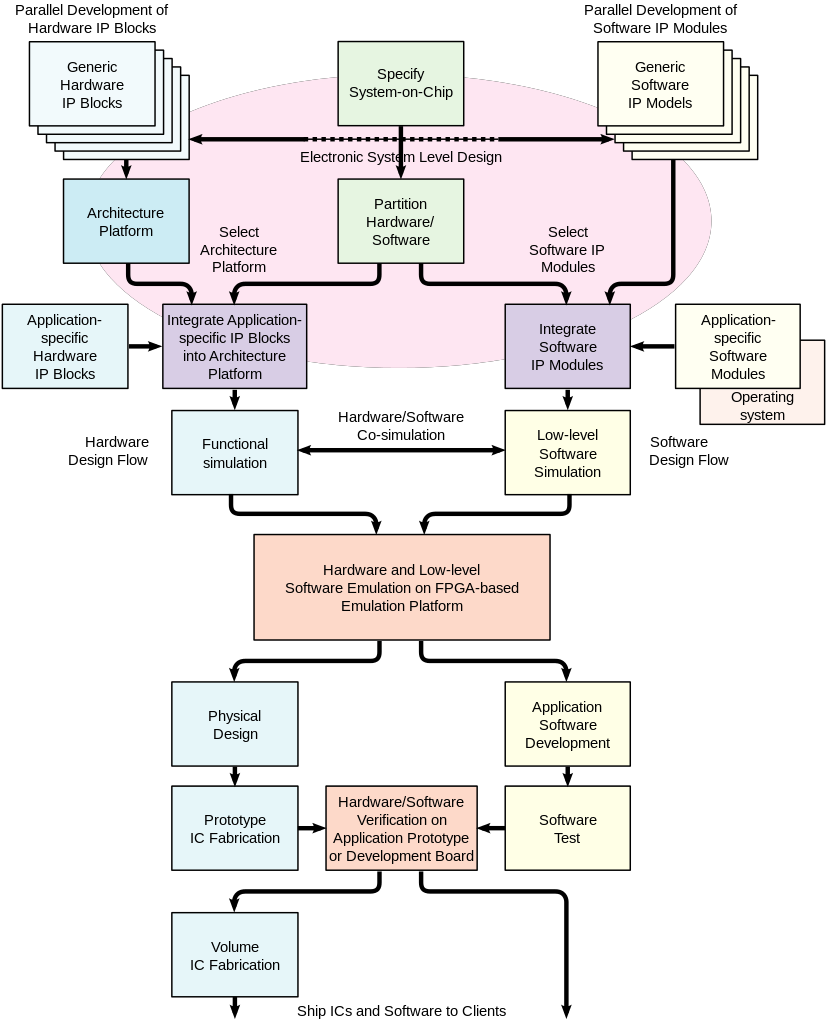

1、架構的設計與驗證

按照要求,對整體的設計劃分模塊。架構模型的仿真可以使用Synopsys公司的CoCentric軟件,它是基于System C的仿真工具。2、HDL設計輸入

設計輸入方法有:HDL語言(Verilog或VHDL)輸入、電路圖輸入、狀態轉移圖輸入。

使用的工具有:Active-HDL,而RTL分析檢查工具有Synopsys的LEDA。3、前仿真工具(功能仿真)

初步驗證設計是否滿足規格要求。

使用的工具有:Synopsys的VCS,Mentor的ModelSim,Cadence的Verilog-XL,Cadence的NC-Verilog。4、邏輯綜合

將HDL語言轉換成門級網表Netlist。綜合需要設定約束條件,就是你希望綜合出來的電路在面積,時序等目標參數上達到的標準;邏輯綜合需要指定基于的庫,使用不同的綜合庫,在時序和面積上會有差異。邏輯綜合之前的仿真為前仿真,之后的仿真為后仿真。

使用的工具有:Synopsys的Design Compiler,Cadence的 PKS,Synplicity的Synplify等。5、靜態時序分析工具(STA)

在時序上,檢查電路的建立時間(Setuptime)和保持時間(Hold time)是否有違例(Violation)。

使用的工具有:Synopsys的Prime Time。6、形式驗證工具

在功能上,對綜合后的網表進行驗證。常用的就是等價性檢查(Equivalence Check)方法,以功能驗證后的HDL設計為參考,對比綜合后的網表功能,他們是否在功能上存在等價性。這樣做是為了保證在邏輯綜合過程中沒有改變原先HDL描述的電路功能。

使用的工具有:Synopsys的Formality

后端設計的流程及使用的EDA工具

1. 數據準備

對于 CDN 的 Silicon Ensemble而言后端設計所需的數據主要有是Foundry廠提供的標準單元、宏單元和I/O Pad的庫文件,它包括物理庫、時序庫及網表庫,分別以.lef、.tlf和.v的形式給出。前端的芯片設計經過綜合后生成的門級網表,具有時序約束和時鐘定義的腳本文件和由此產生的.gcf約束文件以及定義電源Pad的DEF(Design Exchange Format)文件。(對synopsys 的Astro 而言, 經過綜合后生成的門級網表,時序約束文件 SDC 是一樣的,Pad的定義文件--tdf, .tf 文件 --technology file,Foundry廠提供的標準單元、宏單元和I/O Pad的庫文件 就與FRAM, CELL view, LM view形式給出(Milkway 參考庫 and DB, LIB file)2. 布局規劃

主要是標準單元、I/O Pad和宏單元的布局。I/OPad預先給出了位置,而宏單元則根據時序要求進行擺放,標準單元則是給出了一定的區域由工具自動擺放。布局規劃后,芯片的大小,Core的面積,Row的形式、電源及地線的Ring和Strip都確定下來了。如果必要 在自動放置標準單元和宏單元之后, 你可以先做一次PNA(power network analysis)--IR drop and EM .3.Placement -自動放置標準單元

布局規劃后,宏單元、I/O Pad的位置和放置標準單元的區域都已確定,這些信息SE(Silicon Ensemble)會通過DEF文件傳遞給PC(Physical Compiler),PC根據由綜合給出的.DB文件獲得網表和時序約束信息進行自動放置標準單元,同時進行時序檢查和單元放置優化。如果你用的是PC +Astro那你可用write_milkway, read_milkway傳遞數據。4.時鐘樹生成(CTS Clock tree synthesis)

芯片中的時鐘網絡要驅動電路中所有的時序單元,所以時鐘源端門單元帶載很多,其負載延時很大并且不平衡,需要插入緩沖器減小負載和平衡延時。時鐘網絡及其上的緩沖器構成了時鐘樹。一般要反復幾次才可以做出一個比較理想的時鐘樹。---Clock skew.5.STA 靜態時序分析和后仿真

時鐘樹插入后,每個單元的位置都確定下來了,工具可以提出Global Route形式的連線寄生參數,此時對延時參數的提取就比較準確了。SE把.V和.SDF文件傳遞給PrimeTime做靜態時序分析。確認沒有時序違規后,將這來兩個文件傳遞給前端人員做后仿真。對Astro 而言,在detail routing 之后,用starRC XT 參數提取,生成的E.V和.SDF文件傳遞給PrimeTime做靜態時序分析,那將會更準確。6.ECO(Engineering Change Order)

針對靜態時序分析和后仿真中出現的問題,對電路和單元布局進行小范圍的改動.7. Filler的插入(padfliier, cell filler)

Filler指的是標準單元庫和I/O Pad庫中定義的與邏輯無關的填充物,用來填充標準單元和標準單元之間,I/O Pad和I/O Pad之間的間隙,它主要是把擴散層連接起來,滿足DRC規則和設計需要。8. 布線(Routing)

Global route-- Trackassign --Detail routing--Routingoptimization 布線是指在滿足工藝規則和布線層數限制、線寬、線間距限制和各線網可靠絕緣的電性能約束的條件下,根據電路的連接關系將各單元和I/O Pad用互連線連接起來,這些是在時序驅動(Timing driven ) 的條件下進行的,保證關鍵時序路徑上的連線長度能夠最小。--Timing report clear9. Dummy Metal的增加

Foundry廠都有對金屬密度的規定,使其金屬密度不要低于一定的值,以防在芯片制造過程中的刻蝕階段對連線的金屬層過度刻蝕從而降低電路的性能。加入Dummy Metal是為了增加金屬的密度。10. DRC和LVS

DRC是對芯片版圖中的各層物理圖形進行設計規則檢查(spacing ,width),它也包括天線效應的檢查,以確保芯片正常流片。LVS主要是將版圖和電路網表進行比較,來保證流片出來的版圖電路和實際需要的電路一致。DRC和LVS的檢查--EDA工具Synopsy hercules/ mentor calibre/ CDN Dracula進行的.Astro also include LVS/DRCcheck commands.11.Tape out

在所有檢查和驗證都正確無誤的情況下把最后的版圖GDSⅡ文件傳遞給Foundry廠進行掩膜制造。

-

IC

+關注

關注

36文章

5907瀏覽量

175274 -

eda

+關注

關注

71文章

2712瀏覽量

172937 -

vhdl

+關注

關注

30文章

816瀏覽量

128082

原文標題:IC設計前后端流程與EDA工具

文章出處:【微信號:eetop-1,微信公眾號:EETOP】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

數字IC后端設計介紹,寫給哪些想轉IC后端的人!

數字IC前端和后端有何區別

IC設計可以分為哪幾個部分?有哪些流程

ASIC與大型邏輯設計實習教程

解析邏輯設計和物理設計流程

IC設計完整流程及工具

IC前端設計工程師

IC設計完整流程

IC前端設計(邏輯設計)和后端設計(物理設計)的詳細解析

IC前端設計(邏輯設計)和后端設計(物理設計)的詳細解析

評論