OrCAD PSpice A/D和高級分析技術(A/A)結合了業界先進的模擬、模數混合信號以及分析工具,以提供一個完整的電路仿真和驗證解決方案。

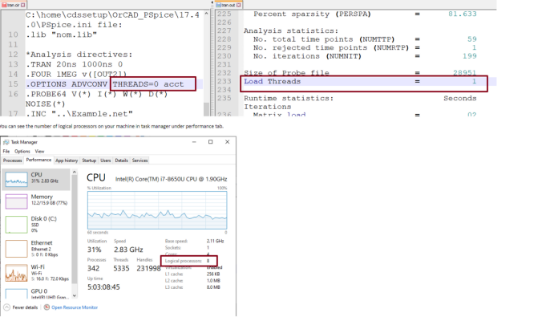

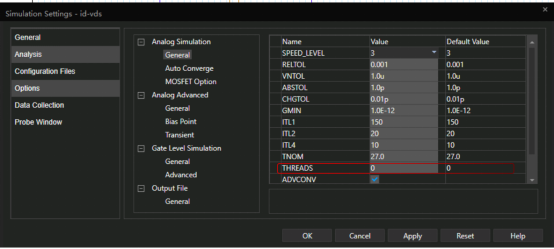

PSpice嘗試使用機器資源的優化數量來提供高效性能。這由選項THREADS控制,

“THREADS=0”是默認值,這意味著線程數由PSpice確定。

PSpice根據以下因素創建默認數量的模擬線程:

器件計數:如果器件計數過低,則創建額外線程沒有幫助。大約每10個器件創建1個線程。

系統上的內核數:模擬線程數不超過邏輯處理器數。

PSpice在內部為每個器件提供一個數字。例如,電阻為0.5,而BSIM mosfet可能為1.5。這是基于該器件模型的計算復雜性。核心數量取決于加權器件計數。例如,如果器件數量為200個,但都是電阻器,那么與200個MOSFET相比,pspice將使用更少的芯。

當器件計數較少時,由于額外的線程創建和調度時間,增加線程會使性能更差,而減少的器件加載時間并不能補償額外的線程創建和調度時間。因此,它不應用于器件少的電路。

注:此選項將模擬瞬態模擬的每個時間步的計算并行化。參數掃描、蒙特卡羅和數字器件模擬的不同運行沒有并行化。

如果你為線程指定了一個非零值,PSpice會接受這個值,并創建指定數量的線程。

例如:THREADS=1表示創建了單個線程。

現在,您可以在中轉儲線程使用情況。通過在中添加帳戶來輸出文件。選項行輸入.cir文件,以查看正在使用的線程數。將其與計算機上可用的邏輯處理器數量進行比較。如果您認為增加線程數會有所幫助,請在設置中增加它,然后查看模擬速度是否會增加。

總結:建議將THREADS=0(默認值),并讓系統確定值。當然也可以根據實際情況添加分析線程。

-

混合信號

+關注

關注

0文章

470瀏覽量

64934 -

仿真

+關注

關注

50文章

4048瀏覽量

133431 -

PSPICE

+關注

關注

18文章

227瀏覽量

71676 -

orcad

+關注

關注

27文章

297瀏覽量

117366

原文標題:【技術指南】如何提升Pspice仿真速度?

文章出處:【微信號:封裝與高速技術前沿,微信公眾號:封裝與高速技術前沿】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

請問硬件仿真的速度能達到甚至超過軟件仿真的速度嗎?

如何提高MPLAB X仿真速度?

請問硬件仿真的速度能達到甚至超過軟件仿真的速度嗎?

Cadence PSpice仿真技術的優勢有哪些

Spice仿真器:仿真速度和容量的提升

解析BOOST電路的PSpice仿真

放大器仿真模型可提高SPICE仿真速度

開關電源的PSPICE仿真分析

如何提升Pspice仿真速度

如何提升Pspice仿真速度

評論