以下文章來源于芯系半導(dǎo)體,作者向陽青年

隨著工藝節(jié)點(diǎn)的進(jìn)步,英特爾也在不斷推進(jìn)下一代封裝技術(shù)的發(fā)展。對高性能硅需求與工藝節(jié)點(diǎn)開發(fā)相結(jié)合,創(chuàng)造了一種新的方案,即處理器不再是單片硅,而是依賴于多個(gè)較小(且可能優(yōu)化過)的芯粒或芯片,通過一種有利于性能、功耗和最終產(chǎn)品的方式封裝在一起。

單個(gè)大型芯片已不再是明智的商業(yè)決策——它們可能因?yàn)槿毕荻y制造,或者制造它們的技術(shù)未針對芯片上的任何一個(gè)特定功能進(jìn)行優(yōu)化。然而,將處理器分成獨(dú)立的硅片會(huì)在這些片之間傳輸數(shù)據(jù)時(shí)產(chǎn)生額外的障礙——如果數(shù)據(jù)必須從硅片過渡到其他介質(zhì)(如封裝或中介層),那么就需要考慮功耗和延遲的成本。權(quán)衡的結(jié)果是,為特定目的優(yōu)化的硅芯片,例如用邏輯工藝制造的邏輯芯片,用內(nèi)存工藝制造的內(nèi)存芯片,而且較小的芯片在分檔時(shí)通常比較大的芯片具有更好的電壓/頻率特性。但支撐這一切的是芯片的組裝方式,這就需要封裝技術(shù)。

英特爾的兩大主要專業(yè)封裝技術(shù)是EMIB和Foveros。英特爾解釋了這兩者在其未來節(jié)點(diǎn)開發(fā)中的應(yīng)用前景。

嵌入式多互連橋(EMIB)相比傳統(tǒng)的硅中介層具有幾個(gè)相當(dāng)明顯的優(yōu)勢。在需要的地方嵌入一小塊硅片而不是使用大面積的中介層具有明顯的成本優(yōu)勢。第一代EMIB產(chǎn)品已經(jīng)在包括該公司高端Stratix X FPGA和Kaby Lake G移動(dòng)芯片在內(nèi)的多個(gè)產(chǎn)品中使用了一段時(shí)間。截至去年初,英特爾已經(jīng)出貨了超過一百萬件基于EMIB的產(chǎn)品。盡管這些是超高端產(chǎn)品,因而其出貨量并不如他們希望的那樣高以攤銷技術(shù)成本,但這足以改進(jìn)該技術(shù),并開始在更多產(chǎn)品中使用。與EMIB類似,F(xiàn)overos通過將兩個(gè)芯片直接面對面堆疊,顯著增加了焊點(diǎn)密度,但這也帶來了更高的成本。

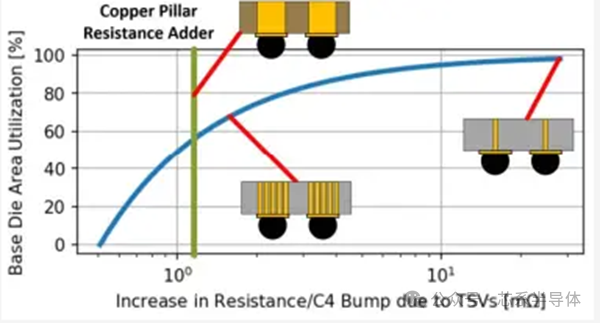

EMIB 和 Foveros 各有優(yōu)劣,但它們都不完美。以Foveros 為例,它在頂層和底層芯片之間提供非常高的帶寬。為了將電力傳輸?shù)巾攲有酒枰ㄟ^底層芯片引入硅通孔(TSV)。TSV 會(huì)增加電阻,雖然可以通過增加更多的通孔來緩解,但這會(huì)占用額外的面積。此外,隔離區(qū)和固有擁塞問題會(huì)使情況更加惡化。根據(jù)英特爾的說法,保守估計(jì)芯片面積會(huì)增加約20%。在某些情況下,這個(gè)比例可能高達(dá)70%。然后是熱管理問題。對于高性能應(yīng)用,熱量的散發(fā)是一個(gè)主要問題,因?yàn)轫攲有酒璧K了熱量傳遞到散熱器的路徑,從而增加了熱阻。傳統(tǒng)的硅中介層可以通過將芯片分布在一大片硅片上來避免這個(gè)問題,從而實(shí)現(xiàn)更好的散熱。同樣,它也消除了邏輯芯片中使用 TSV 的需求,因此不會(huì)影響面積利用率。然而,較大的中介層會(huì)增加成本。此外,2.5D 解決方案失去了3D封裝的優(yōu)勢。

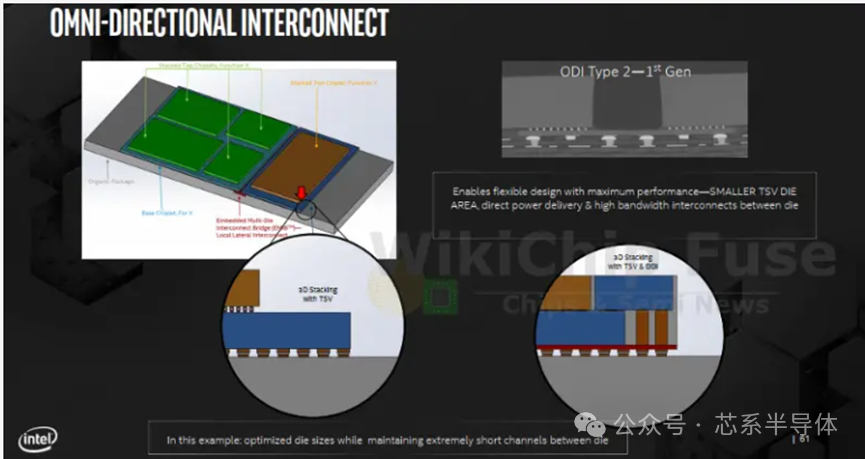

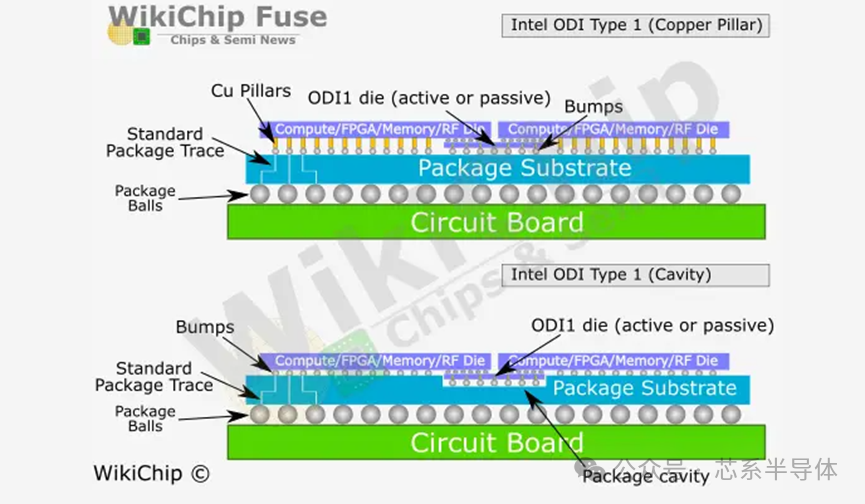

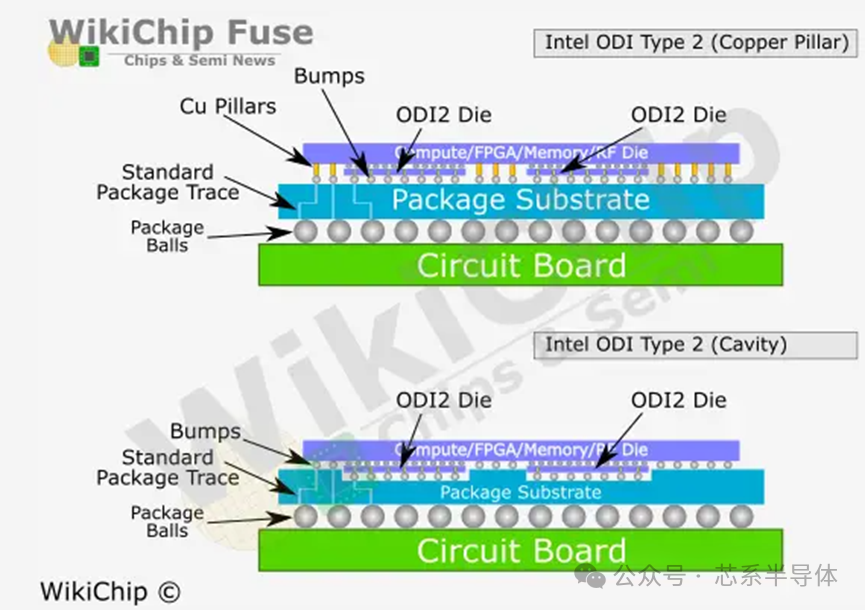

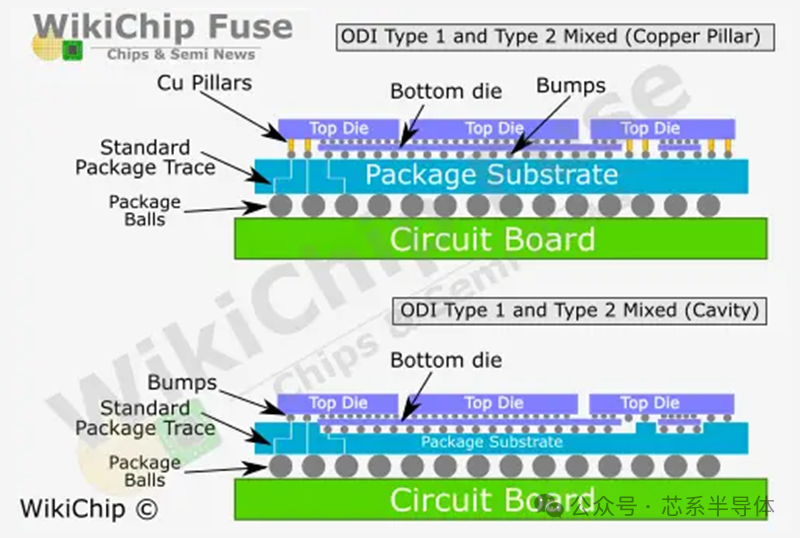

全向互連(ODI)是一新封裝互連技術(shù)。ODI 通過多種3D封裝流程,在功率傳輸和冷卻能力方面相比于硅中介層等替代技術(shù)有顯著提升,從而彌補(bǔ)了EMIB和Foveros之間的差距。ODI目前有四種變體。兩種主要選項(xiàng)分別為“類型1”和“類型2”。每種類型都有兩種風(fēng)格——銅柱和空腔,所有四種變體可以根據(jù)需要組合在一起。同樣,底部ODI芯片可以是有源芯片、無源芯片或兩者的組合。

在ODI類型1中,底部芯片放置在兩個(gè)頂層芯片的下方,或者放置在一個(gè)不能完全覆蓋底部芯片的單個(gè)芯片下方。在ODI1中,底部芯片僅覆蓋頂層芯片需要連接的部分,繼承了Foveros類互連的優(yōu)點(diǎn),同時(shí)消除了TSV的缺點(diǎn)。ODI1可以是無源的,例如在芯片之間簡單地進(jìn)行路由,或者是有源的,例如在多個(gè)芯片之間主動(dòng)路由數(shù)據(jù)或在多個(gè)芯片下方提供高度本地化的緩存。這種類型也可以用于單個(gè)芯片,例如在處理器與HBM或其他邏輯結(jié)合的情況下。

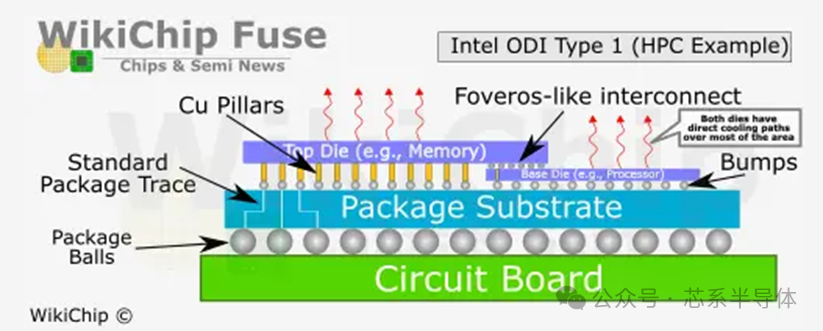

對于高性能應(yīng)用而言,熱量問題尤為重要,ODI1 提供了標(biāo)準(zhǔn) 2.5D 中介層所具備的額外優(yōu)勢,即直接訪問冷卻解決方案而無任何障礙。英特爾提供的一個(gè)示例是一個(gè)微處理器與堆疊內(nèi)存的直接連接。ODI 避免了將兩個(gè)芯片完全堆疊,從而使得兩個(gè)芯片都可以直接接觸冷卻解決方案。同時(shí),這個(gè)版本保留了類似 Foveros 的芯片間高帶寬互連,消除了通過硅中介層的長通道的需求。

表面上看,1型版本可能與標(biāo)準(zhǔn)的EMIB非常相似,但實(shí)際上卻有很大不同。在這一版本中,ODI芯片并未嵌入具有四周布線能力的硅中。相反,基礎(chǔ)的ODI芯片是通過熱壓鍵合以受控高度放置在腔體內(nèi),然后使用熱壓鍵合(TCB)連接頂部芯片。通過獨(dú)立控制底部芯片的高度,他們能夠最大化C4工藝的效果。

在ODI類型2中,芯片完全位于頂層芯片下方。在這種情況下,底層芯片可以精確地定位在所需的位置,盡可能接近頂層芯片中所需邏輯的布線路徑,就像使用底面電容(LSC)一樣,以最大化它們的效率。ODI2可以用來增強(qiáng)頂層芯片的優(yōu)勢,比如增加額外的I/O功能或本地緩存。或者,它可以用來增加另一層主要功能,例如在處理器下方直接附加一個(gè)加速器。

混合搭配:ODI 的一個(gè)有趣特性是可以根據(jù)需要和實(shí)際情況自由混合搭配各種選項(xiàng)。例如,可以將基底做得更大,以包含多個(gè)頂部芯片,這種配置屬于 Type 2 型配置,但邊緣芯片可以采用 Type 1 型配置,使它們的電力通過銅柱進(jìn)行傳輸。

英特爾推出了許多新的封裝技術(shù),涵蓋了各種功能和能力。自首次披露EMIB以來,經(jīng)過了數(shù)年的時(shí)間,Kaby Lake G等芯片才開始投產(chǎn)。然而,隨著EMIB和Foveros技術(shù)的成熟,我們可能會(huì)看到新能力的進(jìn)一步整合,超越ODI,并以更快速度進(jìn)入生產(chǎn)階段。

任何芯片間連接的一個(gè)問題就是連接本身。在目前提到的所有這些技術(shù)中,我們處理的是微凸點(diǎn)焊接連接——帶有錫焊帽的小銅柱,這些銅柱被組合在一起并‘焊接’以創(chuàng)建連接。隨著這些技術(shù)的不斷發(fā)展,銅的生長和錫焊的沉積變得越來越困難,而且電子元件在不同金屬間傳輸時(shí)也存在功率損耗的問題。Foveros Direct 通過直接銅對銅焊接解決了這個(gè)問題。

研究人員已經(jīng)探索了若干年的直接硅對硅連接的概念,而不是依賴于柱和凸點(diǎn)的結(jié)合。如果一塊硅片直接與另一塊硅片對齊,那么幾乎不需要額外的步驟來生長銅柱等。問題在于確保所有連接都能實(shí)現(xiàn),確保上下兩個(gè)芯片是如此平坦,以至于沒有任何東西能阻礙連接。而且,這兩塊硅片必須融為一體,永久焊接在一起,無法分開。

Foveros Direct是一項(xiàng)技術(shù),它幫助英特爾將芯片間連接的凸點(diǎn)間距縮小到10微米,相較于Foveros Omni密度提高了6倍。通過實(shí)現(xiàn)平坦的銅對銅連接,凸點(diǎn)密度得以增加,而全銅連接的使用意味著低阻連接,從而降低了功耗。英特爾表示,借助Direct,功能芯片的劃分變得更加容易,功能模塊可以根據(jù)需要拆分到多個(gè)層次上。

從技術(shù)上講,F(xiàn)overos Direct作為芯片間鍵合可以視為Foveros Omni的補(bǔ)充,后者將電源連接置于基底之外——兩者可以獨(dú)立使用。直接鍵合會(huì)使內(nèi)部電源連接更容易,但可能仍會(huì)存在干擾問題,而Omni可以解決這一問題。需要注意的是,臺積電也有類似的技術(shù),稱為Chip-on-Wafer(或Wafer-on-Wafer)。

-

芯片

+關(guān)注

關(guān)注

453文章

50387瀏覽量

421783 -

英特爾

+關(guān)注

關(guān)注

60文章

9880瀏覽量

171482 -

封裝技術(shù)

+關(guān)注

關(guān)注

12文章

545瀏覽量

67961 -

先進(jìn)封裝

+關(guān)注

關(guān)注

1文章

373瀏覽量

223

原文標(biāo)題:淺談Intel在先進(jìn)封裝領(lǐng)域的探索:EMIB、Foveros、ODI、Direct

文章出處:【微信號:封裝與高速技術(shù)前沿,微信公眾號:封裝與高速技術(shù)前沿】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

測試芯片出爐 Altera/英特爾搶得14nm頭籌

英特爾轉(zhuǎn)型移動(dòng)領(lǐng)域難言樂觀

產(chǎn)業(yè)風(fēng)暴,英特爾能否扳倒ARM?

英特爾愛迪生閃存失敗

為什么選擇加入英特爾?

在移動(dòng)領(lǐng)域,ARM在哪些方面領(lǐng)先英特爾

英特爾重點(diǎn)發(fā)布o(jì)neAPI v1.0,異構(gòu)編程器到底是什么

英特爾重新思考解決芯片短缺的常用基板

關(guān)于英特爾神秘實(shí)驗(yàn)室的分析和介紹

英特爾封裝技術(shù)路線

淺談?dòng)⑻貭栐谙冗M(jìn)封裝領(lǐng)域的探索

淺談?dòng)⑻貭栐谙冗M(jìn)封裝領(lǐng)域的探索

評論