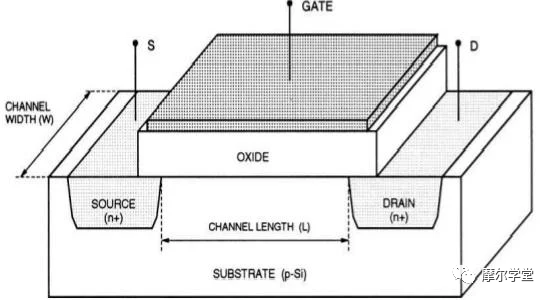

MOS管(金屬氧化物半導體場效應晶體管)的泄漏電流是指在MOS管關斷狀態下,從源極或漏極到襯底之間仍然存在的微弱電流。這些泄漏電流可能對電路的性能和穩定性產生不利影響,因此需要深入了解其類型和產生原因。

一、MOS管泄漏電流的類型

MOS管的泄漏電流主要包括以下幾種類型:

- 柵極泄漏電流(I_g)

柵極泄漏電流是指通過柵極氧化層隧穿進入襯底的電流。當柵極上施加高電場時,電子可能通過Fowler-Nordheim隧道效應穿過柵極氧化層進入襯底,形成柵極泄漏電流。柵極氧化層的厚度和柵極電壓的大小是影響柵極泄漏電流的主要因素。隨著晶體管尺寸的不斷縮小和電源電壓的降低,柵極氧化層的厚度也在不斷減小,導致柵極泄漏電流呈指數級增加。

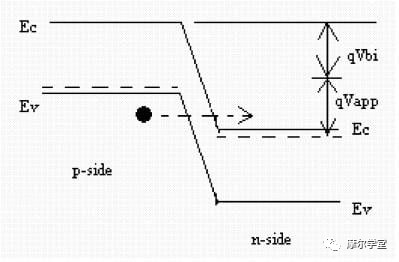

- 反向偏置pn結漏電流(I_rev)

MOS管的源極和漏極與襯底之間形成了pn結。當這些pn結處于反向偏置狀態時,會產生反向偏置pn結漏電流。這種漏電流主要由耗盡區邊緣的擴散和漂移電流以及耗盡區中產生的電子-空穴對組成。在一些重摻雜的pn區,還可能存在帶間隧穿(BTBT)現象貢獻的泄漏電流。反向偏置pn結漏電流的大小取決于摻雜濃度、結面積以及電場強度等因素。

- 亞閾值漏電流(I_sub)

亞閾值漏電流是指在柵源電壓低于閾值電壓(V_th)時,MOS管仍然存在的微弱電流。當柵源電壓低于閾值電壓時,器件不會立即關閉,而是進入“亞閾值區”。在亞閾值區,溝道中的電荷積累較少,但仍然存在少數載流子的擴散電流,導致亞閾值漏電流的產生。亞閾值漏電流與閾值電壓成反比,隨著溫度的升高而增加。

- 柵極感應漏極降低(GIDL)漏電流

GIDL漏電流是指柵極與漏極重疊區域下的強電場導致的漏極到阱的電流。當柵極與漏極之間的電場強度過高時,會導致深度耗盡區以及漏極和阱交界處耗盡層變薄,從而有效形成漏極到阱的電流。GIDL漏電流與柵極和漏極之間的電壓差(V_GD)有關,通常NMOS的GIDL漏電流會比PMOS的大兩個數量級。

- 熱載流子注入漏電流

在MOS管工作過程中,載流子在通道中的散射和碰撞會產生熱能,使部分載流子獲得足夠的能量越過勢壘,形成熱載流子注入漏電流。熱載流子注入漏電流主要發生在襯底-氧化物界面附近的高電場區域。這種現象對電子的影響比對空穴的影響更大,因為電子具有較小的有效質量和較小的勢壘高度。

二、MOS管泄漏電流的產生原因

MOS管泄漏電流的產生原因多種多樣,主要包括以下幾個方面:

- 柵極氧化層質量

柵極氧化層是MOS管的關鍵組成部分,其質量直接影響柵極泄漏電流的大小。柵極氧化層中存在缺陷、雜質或損傷時,會導致電子隧穿概率增加,從而增大柵極泄漏電流。因此,提高柵極氧化層的質量和完整性是降低柵極泄漏電流的關鍵。

- 摻雜濃度和結面積

反向偏置pn結漏電流的大小與摻雜濃度和結面積密切相關。重摻雜的pn結中,帶間隧穿(BTBT)效應在反向偏置漏電流中占主導地位。此外,結面積的增加也會使反向偏置漏電流增大。因此,合理控制摻雜濃度和結面積是降低反向偏置pn結漏電流的有效方法。

- 閾值電壓

亞閾值漏電流與閾值電壓成反比,因此閾值電壓的大小直接影響亞閾值漏電流的大小。隨著CMOS技術的不斷發展,現代CMOS器件中的閾值電壓相對較低,導致亞閾值漏電流成為主要的泄漏電流分量之一。為了降低亞閾值漏電流,可以采取提高閾值電壓、優化器件結構等方法。

- 電場強度

柵極與漏極之間的電場強度是影響GIDL漏電流的主要因素之一。當電場強度過高時,會導致深度耗盡區和漏極到阱的電流產生。因此,合理控制柵極與漏極之間的電壓差以及優化器件結構是降低GIDL漏電流的有效方法。

- 溫度效應

溫度是影響MOS管泄漏電流的重要因素之一。溫度升高會使雜質活化、表面態密度增加,進一步增加漏電流。此外,溫度升高還會導致載流子的熱激活和增加電子-空穴對的生成速率,從而促使漏電流增加。因此,合理控制工作溫度是降低MOS管泄漏電流的有效手段之一。

- 制造工藝

MOS管的制造工藝對其泄漏電流也有重要影響。例如,制造過程中引入的缺陷、雜質或損傷都可能導致泄漏電流的增加。因此,提高制造工藝的質量控制、減少雜質與缺陷以及增強絕緣層的性能是降低MOS管泄漏電流的關鍵措施之一。

三、降低MOS管泄漏電流的策略與技術

為了降低MOS管的泄漏電流,業界已經開發并實施了多種策略和技術。以下是一些關鍵的策略和技術,旨在提高MOS管的性能和穩定性:

- 采用先進的柵極氧化層技術

柵極氧化層的質量對泄漏電流有著至關重要的影響。為了提高柵極氧化層的質量,可以采用先進的氧化工藝,如原子層沉積(ALD)或化學氣相沉積(CVD)技術,來精確控制氧化層的厚度和均勻性。此外,使用高k介電材料(如HfO2、Al2O3等)替代傳統的SiO2作為柵極氧化層,可以在保持相同電場強度的同時,增加氧化層的物理厚度,從而降低隧穿電流。

- 優化摻雜工藝

合理的摻雜濃度和分布對于控制泄漏電流至關重要。通過精確控制摻雜過程,可以減少雜質和缺陷的產生,從而降低由這些缺陷引起的泄漏電流。此外,采用梯度摻雜或變摻雜技術,可以在溝道中形成更平滑的勢能分布,有助于減少亞閾值漏電流。

- 創新器件結構

通過創新器件結構,如三維鰭式場效應晶體管(FinFET)或納米線FET,可以更有效地控制溝道中的載流子分布,從而降低泄漏電流。這些新型器件結構具有更小的溝道寬度和更高的柵極控制能力,使得在相同柵極電壓下,溝道中的載流子濃度更低,從而減少了泄漏電流。

- 采用多柵極結構

多柵極結構,如雙柵極或環繞柵極(GAA)FET,通過增加柵極與溝道的接觸面積,提高了柵極對溝道載流子的控制能力。這種結構有助于降低亞閾值漏電流和柵極泄漏電流,同時提高了器件的開關速度和性能。

- 應用先進的封裝技術

先進的封裝技術,如三維集成(3D IC)和系統級封裝(SiP),可以實現更緊密的器件連接和更小的封裝尺寸。這些技術有助于降低由于封裝過程中的熱應力和機械應力引起的泄漏電流。此外,通過優化封裝材料和工藝,還可以減少封裝過程中的缺陷和污染,從而降低泄漏電流。

- 實施溫度管理策略

溫度是影響泄漏電流的重要因素之一。因此,實施有效的溫度管理策略對于降低泄漏電流至關重要。這包括使用散熱片、風扇或液冷等散熱技術來降低器件的工作溫度,以及采用熱敏電阻或熱電偶等溫度傳感器來監測和控制溫度。此外,通過優化電路設計和材料選擇,也可以降低器件在工作過程中產生的熱量。

- 引入智能控制算法

隨著人工智能和機器學習技術的不斷發展,智能控制算法在半導體器件設計和制造中的應用越來越廣泛。通過引入智能控制算法,可以根據實時數據和反饋來動態調整工藝參數和設備設置,從而優化器件的性能和降低泄漏電流。例如,使用機器學習算法來預測和優化摻雜濃度和分布,或使用神經網絡來實時監測和控制溫度。

四、未來展望

隨著半導體技術的不斷發展和創新,MOS管的泄漏電流控制技術也將不斷演進和升級。未來,我們可以期待以下幾個方面的進展:

- 新材料的應用 :隨著新型半導體材料(如二維材料、拓撲絕緣體等)和新型柵極氧化層材料(如二維高k介電材料等)的研發和應用,有望為降低MOS管的泄漏電流提供新的解決方案。

- 更先進的制造工藝 :隨著原子層沉積、電子束光刻等先進制造工藝的不斷成熟和應用,將能夠更精確地控制器件的尺寸和結構,從而降低泄漏電流并提高器件的性能。

- 智能化和自動化技術的融合 :隨著智能化和自動化技術的不斷發展,將能夠更高效地監測和控制MOS管的制造過程,從而進一步提高器件的質量和穩定性,降低泄漏電流。

- 環保和可持續發展 :在未來的MOS管設計和制造中,將更加注重環保和可持續發展。例如,通過使用無毒或低毒的制造材料,以及采用節能和高效的制造工藝來降低對環境的影響。

五、結論

MOS管的泄漏電流是影響其性能和穩定性的重要因素之一。了解泄漏電流的類型和產生原因對于優化MOS管的設計和制造具有重要意義。通過提高柵極氧化層質量、合理控制摻雜濃度和結面積、優化器件結構、合理控制電場強度和溫度以及提高制造工藝的質量控制等措施,可以有效地降低MOS管的泄漏電流。未來,隨著CMOS技術的不斷發展和創新,相信會有更多先進的泄漏電流控制技術涌現出來,為MOS管的設計和應用提供更加可靠和高效的解決方案。

-

MOS管

+關注

關注

108文章

2397瀏覽量

66627 -

晶體管

+關注

關注

77文章

9641瀏覽量

137876 -

泄漏電流

+關注

關注

0文章

22瀏覽量

6927

發布評論請先 登錄

相關推薦

探究MOS晶體管中各種類型的泄漏電流的原因

MOS管的漏電流

基于TMS320F2812泄漏電流測試系統的設計

影響測量泄漏電流的因素及排除方法

淺析MOS 晶體管的核心概念

電容器漏電流產生原因有哪些

什么是泄漏電流試驗?

MOS管泄漏電流的類型和產生原因

MOS管泄漏電流的類型和產生原因

評論