GPIO的功能,簡單說就是可以根據(jù)自己的需要去配置為輸入或輸出。但是在配置GPIO管腳的時候,常會見到兩種模式:開漏(open-drain,漏極開路)和推挽(push-pull)。

Push-Pull推挽輸出

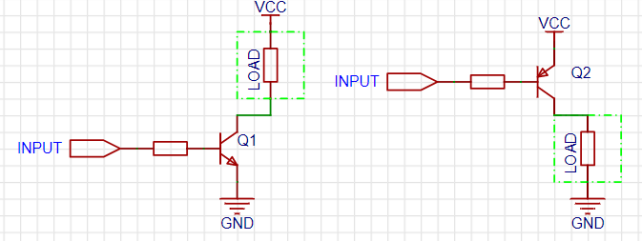

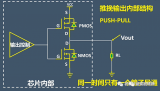

輸出的器件是指輸出腳內(nèi)部集成有一對互補的MOSFET,當Q1導通、Q2截止時輸出高電平;而當Q1截止導通、Q2導通時輸出低電平。

Push-pull輸出,實際上內(nèi)部是用了兩個晶體管(transistor),此處分別稱為top transistor和bottom transistor。通過開關對應的晶體管,輸出對應的電平。top transistor打開(bottom transistor關閉),輸出為高電平;bottom transistor打開(top transistor關閉),輸出低電平。Push-pull即能夠漏電流(sink current),又可以集電流(source current)。其也許有,也許沒有另外一個狀態(tài):高阻抗(high impedance)狀態(tài)。除非Push-pull需要支持額外的高阻抗狀態(tài),否則不需要額外的上拉電阻。

Open-Drain開漏輸出

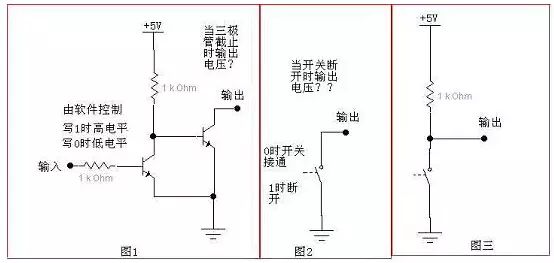

開漏電路就是指以MOSFET的漏極為輸出的電路。指內(nèi)部輸出和地之間有個N溝道的MOSFET(Q1),這些器件可以用于電平轉換的應用。輸出電壓由Vcc'決定。Vcc'可以大于輸入高電平電壓VCC(up-translate)也可以低于輸入高電平電壓VCC(down-translate)。

Open-drain輸出,則是比push-pull少了個top transistor,只有那個bottom transistor。(就像push-pull中的那樣)當bottom transistor關閉,則輸出為高電平。此處沒法輸出高電平,想要輸出高電平,必須外部再接一個上拉電阻(pull-up resistor)。Open-drain只能夠漏電流(sink current),如果想要集電流(source current),則需要加一個上拉電阻。

老外的理解

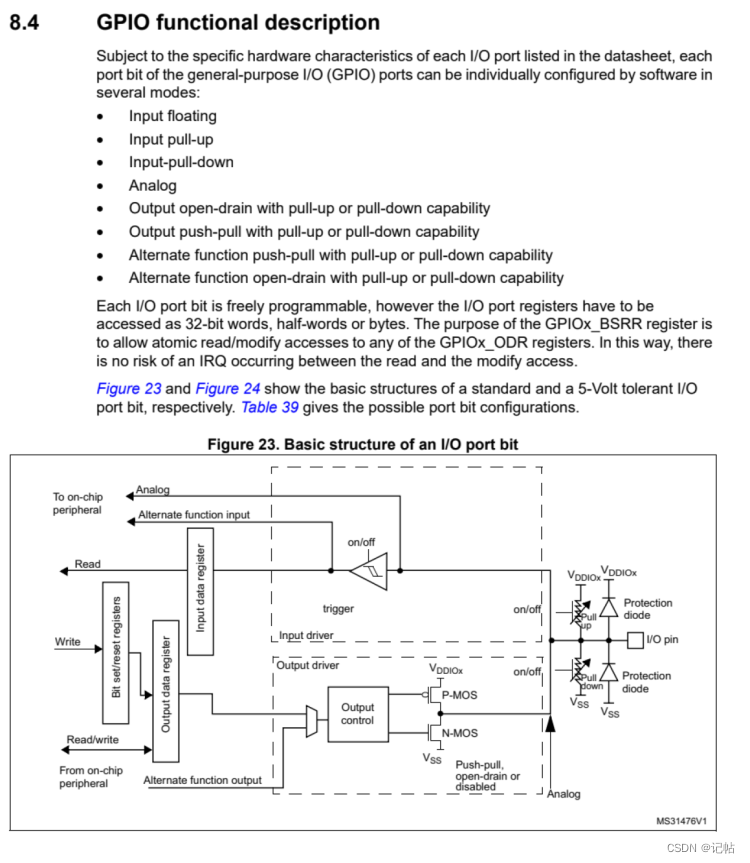

常見的GPIO的模式可以配置為open-drain或push-pull,具體實現(xiàn)上,常為通過配置對應的寄存器的某些位來配置為open-drain或是push-pull。當我們通過CPU去設置那些GPIO的配置寄存器的某位(bit)的時候,其GPIO硬件IC內(nèi)部的實現(xiàn)是,會去打開或關閉對應的top transistor。相應地,如果設置為了open-d模式的話,是需要上拉電阻才能實現(xiàn),也能夠輸出高電平的。因此,如果硬件內(nèi)部(internal)本身包含了對應的上拉電阻的話,此時會去關閉或打開對應的上拉電阻。如果GPIO硬件IC內(nèi)部沒有對應的上拉電阻的話,那么你的硬件電路中,必須自己提供對應的外部(external)的上拉電阻。而push-pull輸出的優(yōu)勢是速度快,因為線路(line)是以兩種方式驅(qū)動的。而帶了上拉電阻的線路,即使以最快的速度去提升電壓,最快也要一個常量的R×C的時間。其中R是電阻,C是寄生電容(parasitic capacitance),包括了pin腳的電容和板子的電容。但是,push-pull相對的缺點是往往需要消耗更多的電流,即功耗相對大。而open-drain所消耗的電流相對較小,由電阻R所限制,而R不能太小,因為當輸出為低電平的時候,需要sink更低的transistor,這意味著更高的功耗。(此段原文:because the lower transistor has to sink that current when the output is low; that means higher power consumption.)而open-drain的好處之一是,允許你cshort(?)多個open-drain的電路,公用一個上拉電阻,此種做法稱為wired-OR連接,此時可以通過拉低任何一個IO的pin腳使得輸出為低電平。為了輸出高電平,則所有的都輸出高電平。此種邏輯,就是“線與”的功能,可以不需要額外的門(gate)電路來實現(xiàn)此部分邏輯。

圖表 4 open-drain“線與”功能

優(yōu)點

Push-Pull推挽輸出

(1)可以吸電流,也可以貫電流;

(2)和開漏輸出相比,push-pull的高低電平由IC的電源低定,不能簡單的做邏輯操作等。

Open-Drain開漏輸出

(1)對于各種電壓節(jié)點間的電平轉換非常有用,可以用于各種電壓節(jié)點的Up-translate和down-translate轉換

(2)可以將多個開漏輸出的Pin腳,連接到一條線上,形成“與邏輯”關系,即“線與”功能,任意一個變低后,開漏線上的邏輯就為0了。這也是I2C,SMBus等總線判斷總線占用狀態(tài)的原理。

(3)利用 外部電路的驅(qū)動能力,減少IC內(nèi)部的驅(qū)動。當IC內(nèi)部MOSFET導通時,驅(qū)動電流是從外部的VCC流經(jīng)R pull-up ,MOSFET到GND。IC內(nèi)部僅需很下的柵極驅(qū)動電流。

(4)可以利用改變上拉電源的電壓,改變傳輸電平:圖表 5 open-drain輸出電平的原理,IC的邏輯電平由電源Vcc1決定,而輸出高電平則由Vcc2決定。這樣我們就可以用低電平邏輯控制輸出高電平邏輯了。

缺點

Push-Pull推挽輸出

一條總線上只能有一個push-pull輸出的器件;

在CMOS電路里面應該叫CMOS輸出更合適,因為在CMOS里面的push-pull輸出能力不可能做得雙極那么大。輸出能力看IC內(nèi)部輸出極N管P管的面積。push-pull是現(xiàn)在CMOS電路里面用得最多的輸出級設計方式

Open-Drain開漏輸出

開漏Pin不連接外部的上拉電阻,則只能輸出低電平。當輸出電平為低時,N溝道三極管是導通的,這樣在Vcc'和GND之間有一個持續(xù)的電流流過上拉電阻R和三極管Q1。這會影響整個系統(tǒng)的功耗。采用較大值的上拉電阻可以減小電流。但是,但是大的阻值會使輸出信號的上升時間變慢。即上拉電阻R pull-up的阻值 決定了邏輯電平轉換的沿的速度。阻值越大,速度越低功耗越小。反之亦然。

-

GPIO

+關注

關注

16文章

1196瀏覽量

51916 -

開漏輸出

+關注

關注

0文章

34瀏覽量

7311 -

推挽輸出

+關注

關注

0文章

41瀏覽量

6512

原文標題:GPIO的推挽輸出和開漏輸出

文章出處:【微信號:mcugeek,微信公眾號:MCU開發(fā)加油站】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

GPIO實現(xiàn)推挽輸出和開漏輸出的關鍵是什么

STM32的GPIO知識點:開漏輸出和推挽輸出

從硬件方面理解GPIO的開漏輸出和推挽輸出

GPIO推挽輸出和開漏輸出模式區(qū)別詳解

GPIO的推挽輸出和開漏輸出以及其優(yōu)缺點分析

GPIO的推挽輸出和開漏輸出以及其優(yōu)缺點分析

評論