摘要:碳化硅(SiC)功率模塊在電動汽車驅動系統中起著至關重要的作用。為了提高功率模塊的性能、減小體積、提高生產效率,本文提出了一種基于多堆疊直接鍵合銅(DBC)單元的功率模塊封裝方法,以并行更多的芯片。該方法利用互感對消效應來減小寄生電感。由于新封裝中的導電面積增加了一倍,因此可以減小功率模塊的整體面積。整個功率模塊被分成更小的單元,以提高制造成品率,并提高設計自由度。

本文對所提出的封裝結構提供了詳細的設計、分析和制作過程。此外,本文還提出了幾種可行的電源終端與DBC Units的連接方案。采用這種結構,在一個商用尺寸的功率模塊中,每個相腿并聯18個芯片。仿真和雙脈沖測試結果表明,與傳統的封裝方式相比,該封裝方式的寄生電感減小了74.8%,占地面積減小了34.9%。

一、介紹

隨著電動汽車的發展,人們對功率器件性能的要求不斷提高,寬禁帶器件變得越來越流行,并得到了廣泛的應用和研究。例如,碳化硅器件具有低導通電阻、高開關速度、高導熱性和高耐壓性,顯示出其替代硅基功率模塊的巨大潛力。然而,制造限制帶來過多的內部缺陷,限制了單個芯片的電流傳導能力。因此,在大功率、大電流應用中,電源模塊往往需要并聯大量SiC芯片,多芯片并聯的電源模塊的布局設計就顯得尤為重要。

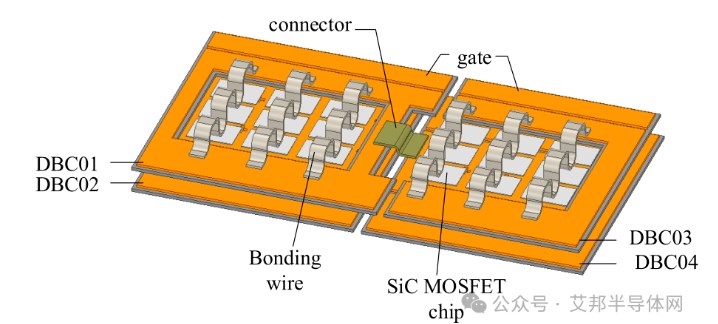

圖1 傳統2D布局功率模塊結構

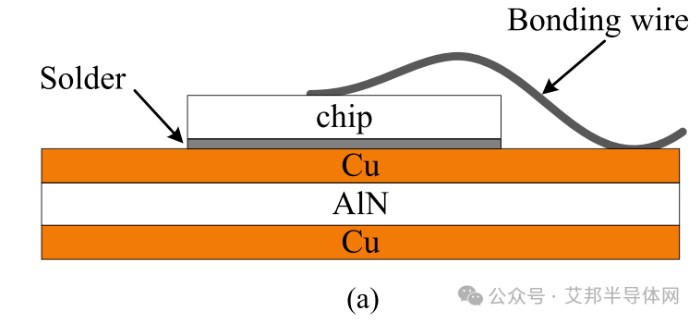

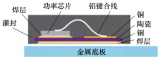

由于成熟且制造工藝簡單,傳統的2D引線鍵合封裝結構仍然廣泛應用于商用SiC功率模塊中。如圖1所示,引線鍵合互連具有相對較大的寄生電感,這可能會顯著限制SiC器件的開關速度。典型的引線鍵合連接如圖2(a)所示。

圖2(a) 傳統的引線鍵合封裝

因此,多SiC芯片并聯的功率模塊主要存在兩個問題:

1)功率模塊的寄生電感會帶來較大的電壓過沖,di/dt急劇增加。目前,越來越多的電動汽車需要800V母線電壓來支持1200V功率模塊。出于安全原因,寄生電感越小越好。

2)更高的功率額定值需要更好的電流平衡能力和更寬的DBC傳導路徑。一般來說,1mm寬的DBC設計用于傳導100A電流,這意味著1000A的功率模塊需要在DBC上有10mm的電流傳導路徑。在一篇參考文獻中,功率模塊的總面積估計為芯片總面積的4-5倍。更寬的傳導路徑可能會阻礙功率模塊設計人員控制整齊的布線、良好的電流共享和先進的散熱平衡,因此,當芯片數量增加時,整體面積增加更多,導致功率密度下降。

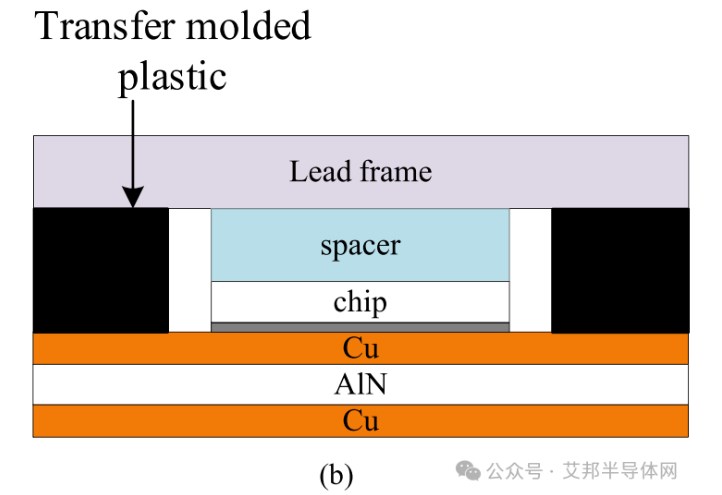

這些問題嚴重限制了寬帶隙功率器件的應用,進一步制約了開關頻率、功率密度和轉換效率的提高。因此,有必要探索新的高功率密度封裝設計來減少寄生,并改善功率模塊內部的電流平衡。 近年來,許多研究人員提出了不同的新布局方法。如圖2(b)所示,平面封裝結構利用DBC的寬銅箔來降低寄生阻抗并具有更高的功率密度,并且可以實現雙面冷卻。但平面封裝也有缺點:平面模組生產過程中需要引入注塑機等專用設備,導致工藝成熟度較低,短期內發展受到限制。此外,并行芯片的數量也受到限制。上述原因導致平面結構的商用模組最多只能并聯8顆芯片。

圖2(b) 平面封裝結構

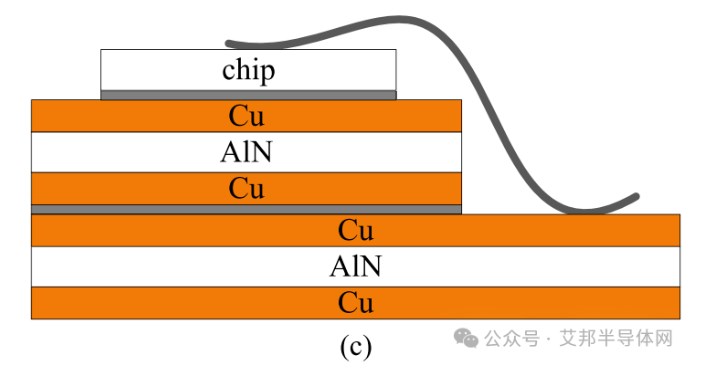

T. Huber 提出了一種1000V/200A半橋模塊,其基板類似于多層基板,這兩種模塊都通過多個陶瓷基板實現了低寄生電感。然而,如圖2(c)所示,兩個模塊都焊接在兩個陶瓷基板的頂層上,這不僅使制造工藝復雜化,而且與常見的2D布局相比也增加了熱阻。

圖2(c) T.Huber提出的封裝結構

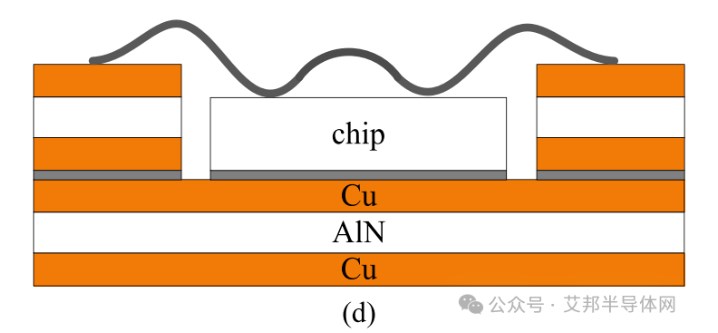

如圖2(d)所示,陳等人改進芯片位置開發1200V/60A堆疊DBC封裝SiC功率模塊,將功率回路電感降至5nH,并將驅動器和散熱器集成到封裝中,但這種設計容錯能力較低,沒有考慮柵極對稱性問題,無法并聯多個芯片。

圖2(d) 陳等人改進的封裝結構

二、DBC固定單元包設計

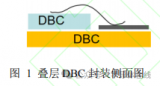

針對上述問題,本文提出了一種低寄生電感、小尺寸、高生產率的多DBC堆疊單元封裝功率模塊。如圖3所示,模塊基板由DBC堆疊而成,底部兩個DBC上各焊接9個SiC MOSFET裸片,形成半橋電路。MOSFET的漏極焊盤通過焊料連接到底部DBC,而MOSFET的柵極和源極焊盤通過引線鍵合連接到頂部DBC。連接器被焊接以連接DBC 02上開關的源極和DBC 04上開關的漏極。DBC 02和DBC 04通過DBC 01的底部銅層連接。

圖3 模擬 DBC 單元圖示

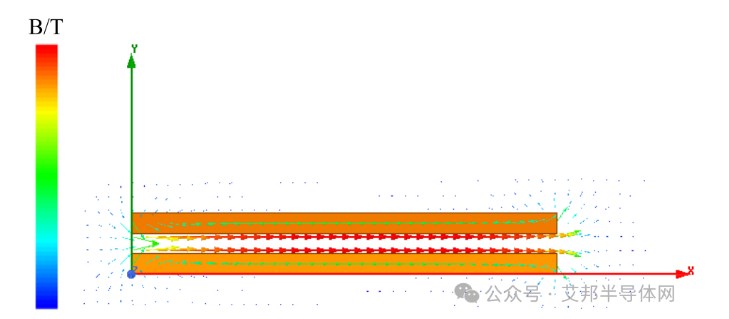

由于這種封裝方法,整個DBC被分成更小的單元,以提高制造良率。小型DBC單元可以靈活組合,提高設計自由度并實現更復雜的模塊布局。另外,該方法利用互感抵消效應,顯著降低寄生電感,在堆疊母線設計中得到了廣泛的應用。如圖4所示,堆疊導體周圍的磁場幾乎被抵消。

圖4 堆疊母線導體周圍的電磁場分布

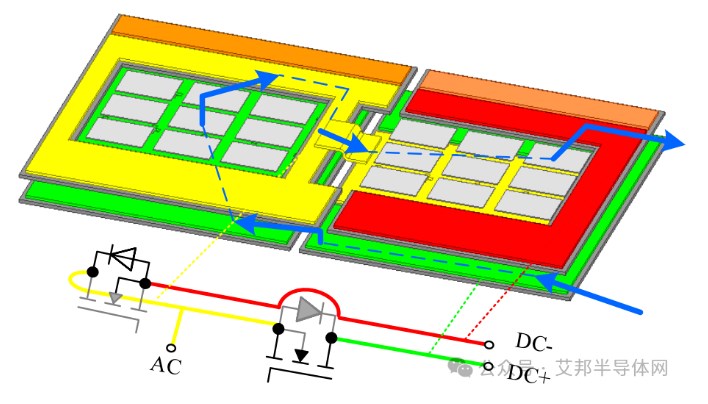

SiC最重要的優勢之一是開關速度快,這也意味著SiC功率模塊封裝需要更低的開關損耗。同時,寄生參數對開關特性有顯著影響,尤其是在高開關速度下。所提出的功率模塊單元的電流環路如圖5所示,電流在兩層中的藍色路徑中流動,可以有效降低寄生電感。通過Ansys Q3D提取寄生電感,結果表明,所提出的電源模塊單元的寄生電感為4.74 nH。相比之下,如圖6所示,類似額定功率的傳統布局模塊的寄生電感為18.84 nH。

圖5 模塊的電氣連接路徑

圖6 傳統布局單元 Q3D 模型

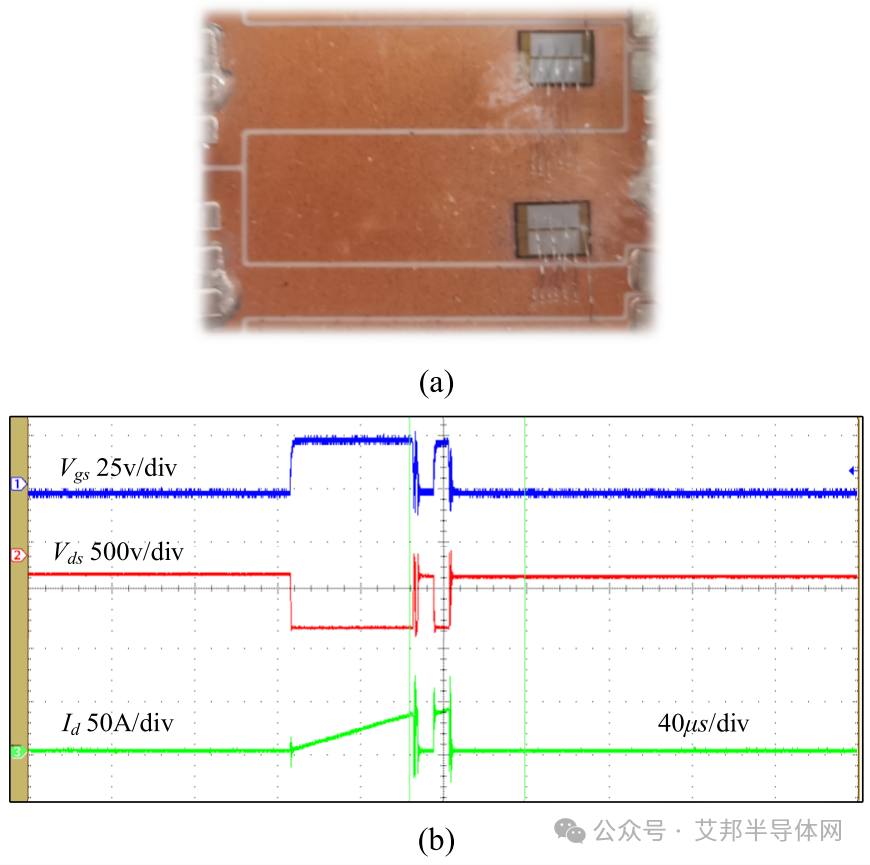

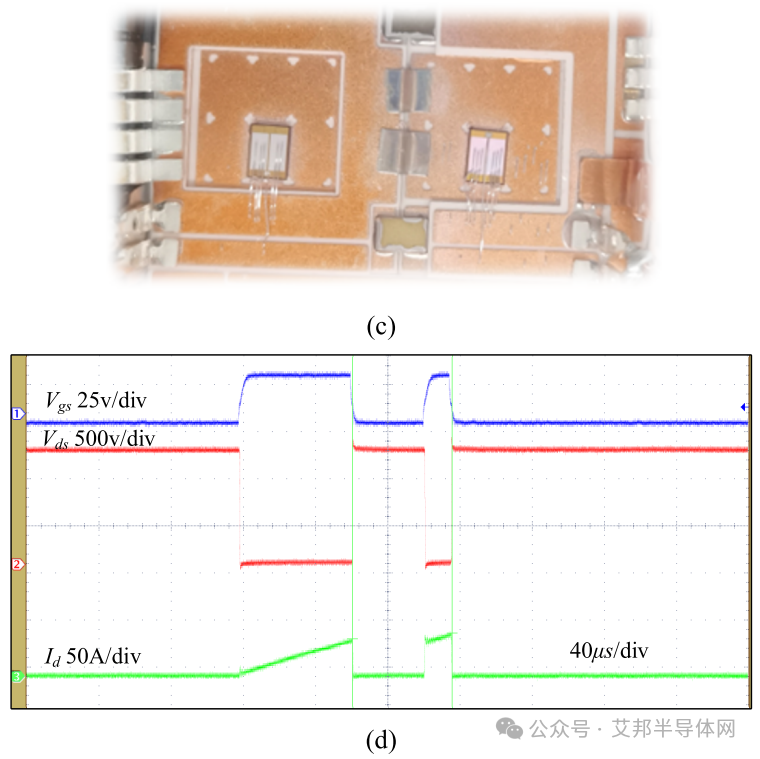

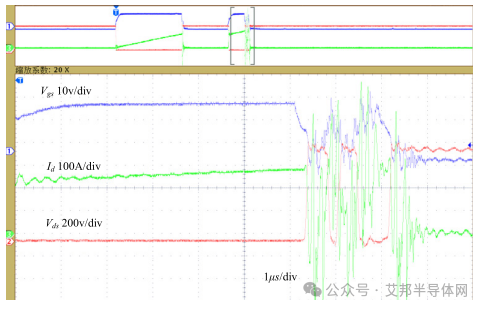

為了驗證所提出的封裝的可行性,如圖7所示,在僅將一個芯片焊接到開關的布局上進行了雙脈沖測試(DPT)實驗。圖7(a)是傳統布局電源模塊,圖7(b)是傳統模塊DPT波形,圖7(c)是建議布局電源模塊,圖7(b)是建議模塊DPT波形。經過對比測試,傳統封裝功率模塊勉強通過了600V DPT。然而,由于寄生電感較大,柵極開始振蕩。相反,所提出的封裝通過了800V雙脈沖測試并且具有良好的波形。

圖7 測試結果對比 (a) 傳統布局功率模塊 (b) 傳統模塊DPT波形 (c) 模擬功率模塊布局 (b) 模擬模塊DPT波形。

三、高密度SiC功率模塊設計制造

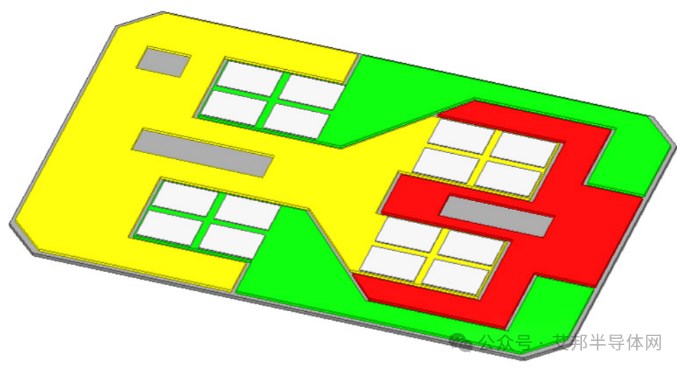

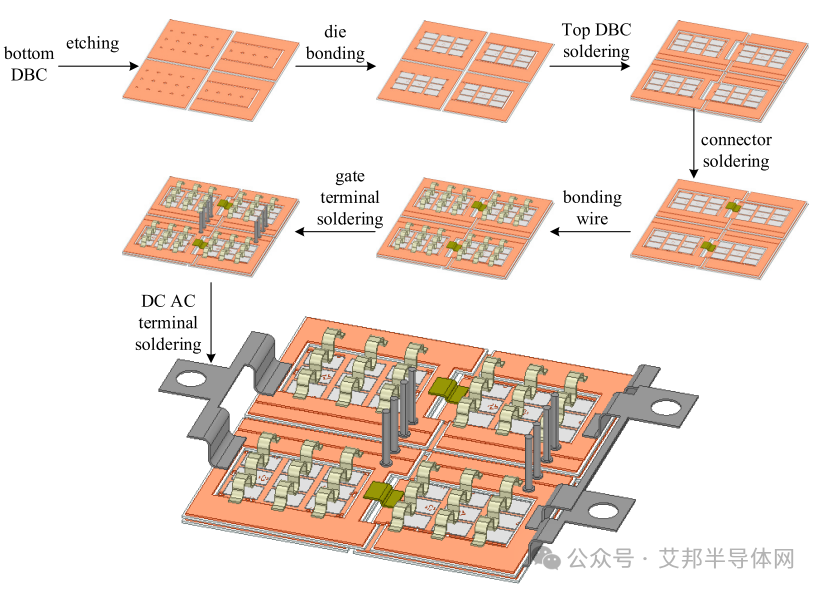

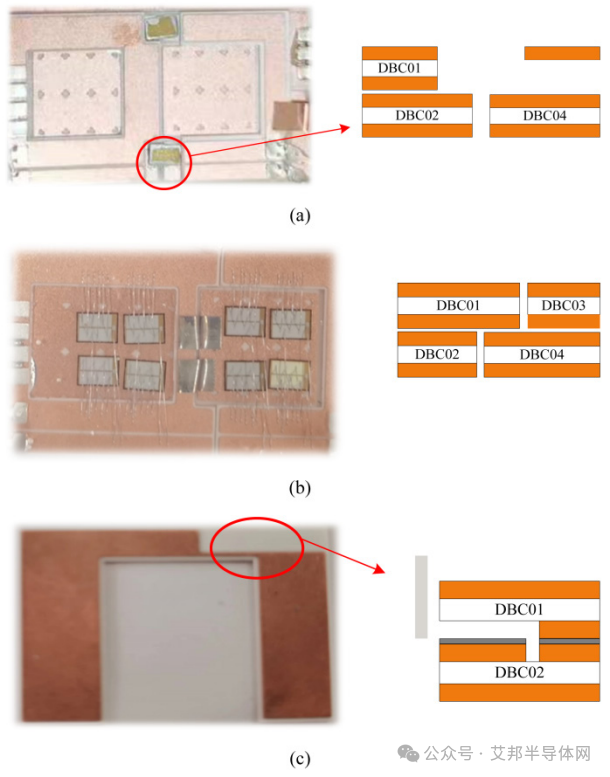

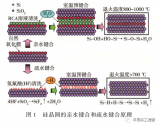

圖8顯示了所提出的電源模塊的制造過程。首先根據電路連接要求和芯片所需的定位,刻蝕4個底部DBC。然后,對芯片進行引線鍵合和真空回流焊接。接下來,將頂層DBC焊接到底層DBC上形成堆疊,并將連接器焊接到需要連接的DBC上。然后,使用超聲波焊接將芯片柵極和源極焊接至頂層DBC引線。最后,將端子一一焊接。

圖8 所提出的電源模塊的制造過程

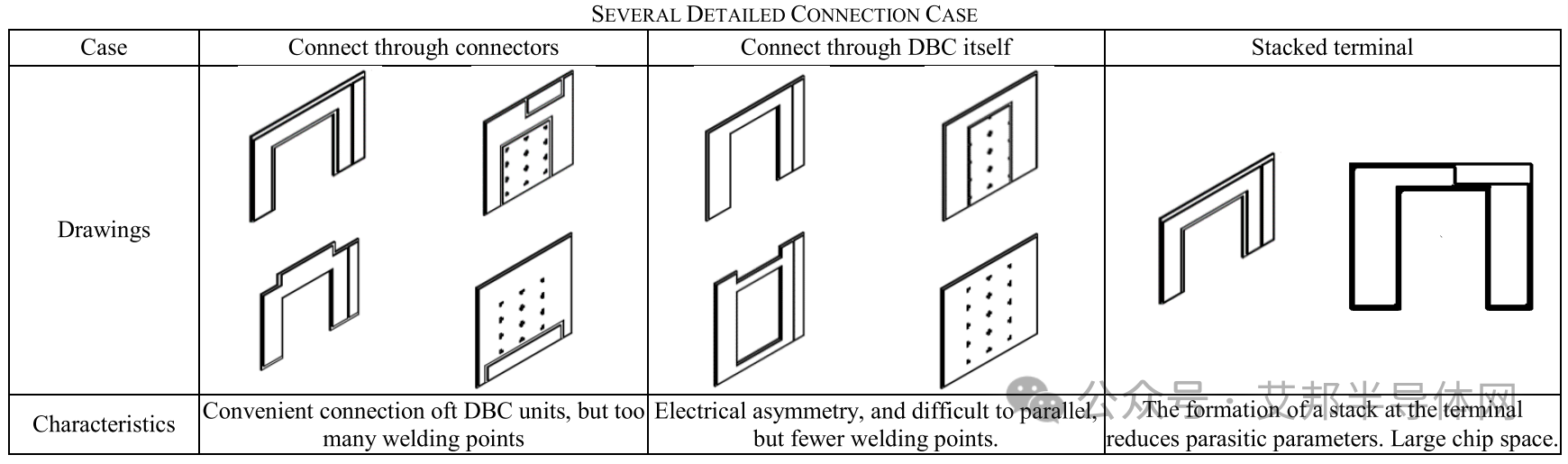

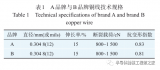

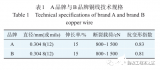

表Ⅰ提供了不同DBC單元之間連接的幾個詳細圖紙和特性,以及終端連接問題。表Ⅰ第一列提供了不同堆疊DBC之間的兩個間隙通過連接器進行焊接的解決方案,如圖9(a)所示,在不同的DBC單元之間實現連接,焊接點過多且端子不匹配。表Ⅰ第二欄提供了利用DBC底部銅片之間連接的低焊點設計,這在之前的設計中也提到過,但沒有考慮對稱性問題,導致不同DBC單元并聯困難,如圖9(b)所示。表Ⅰ中的第三列利用三維空間,將端子設置在DBC下方的間隙處,在端子處形成堆疊,以減少寄生電感,這也可以節省更多的芯片空間并并行多個芯片,如圖9(c)。

表Ⅰ 幾種詳細連接情況

圖9 連接的不同情況 (a) 通過連接器連接 (b) 通過 DBC 本身進行連接 (c) 堆疊式終端

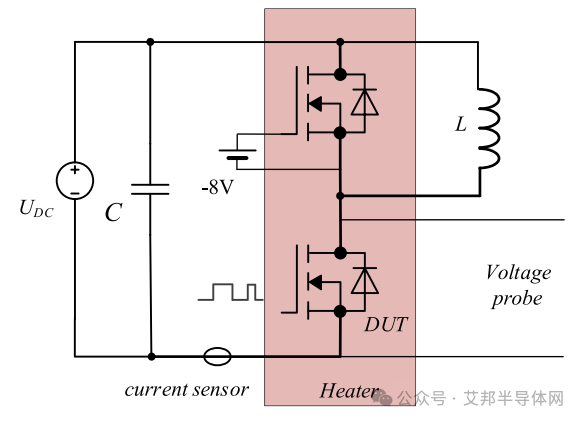

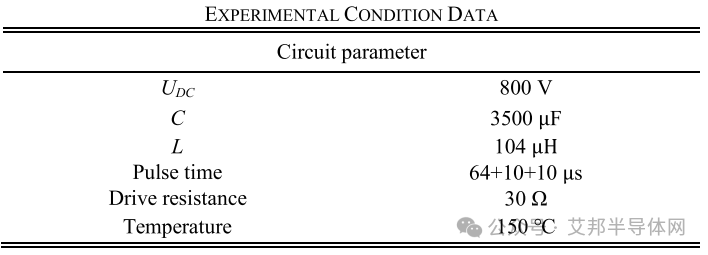

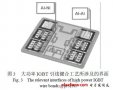

為了驗證所提出的多DBC堆疊單元封裝的可行性,如圖10所示,制作了18個并聯芯片的功率模塊單元。該開關器件的動態性能,如電壓振蕩、電壓過沖和開關損耗等,可以通過圖11所示的DPT電路獲得,實驗電路參數如表Ⅱ所示。該電路基于半橋電路,下部開關作為被測器件。使用高壓隔離差分探頭測量漏源電壓Vds,使用Rogowski線圈電流探頭測量漏極電流Id。使用常規探針測量柵源電壓Vgs。上開關管的柵極受到負電壓,因此上開關管關斷,只有續流工作。

圖10 模擬功率模塊單元

圖11 雙脈沖測試電路

表Ⅱ 實驗參數

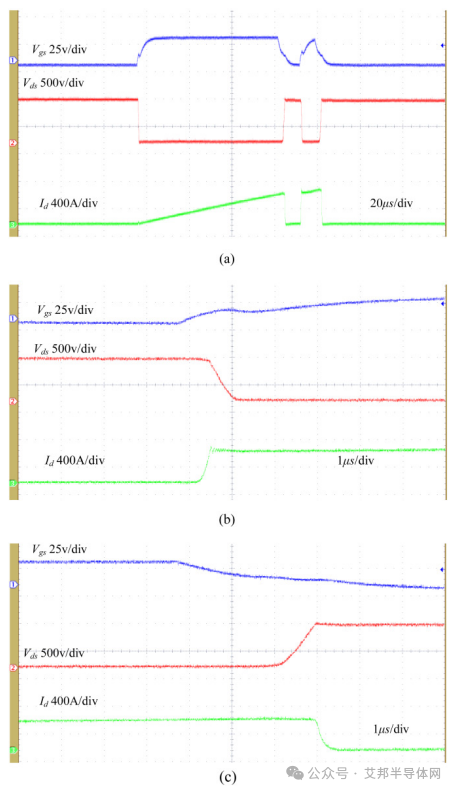

雙脈沖結果波形如圖12(a)所示,第一個脈沖的導通過程如圖12(b)所示,第二個脈沖的關斷過程如圖12(c)所示。藍色波形是柵極驅動信號Vgs,紅色信號是測量的開關漏源電壓Vds ,綠色波形是漏極電流Id。可以看出,模塊已通過800V/500A的DPT。

圖12 波形結果 (a) 雙脈沖測試波形,(b) 第一個脈沖開啟過程,(c) 第二個脈沖關閉過程

圖13 傳統布局模塊波形

針對傳統2D布局功率模塊的缺點,本文提出了一種SiC功率模塊采用多個DBC堆疊單元的封裝方法。詳細介紹了建議的DBC單元和電源模塊,以及提供了不同DBC之間的多種連接情況。實驗和仿真結果表明,所提出的封裝模塊具有以下優點:

1)創新的多DBC單元封裝設計,可有效降低寄生電感,并具有良好的電氣性能。 2)載流能力增加,相同電流下,可減少模塊的平面面積,允許更多芯片并聯。

3)與平面封裝相比,所提出的模塊工藝簡單,成本降低。而且單元設計還可以提高生產率。

轉載:艾邦半導體網

-

封裝

+關注

關注

126文章

7794瀏覽量

142741 -

SiC

+關注

關注

29文章

2771瀏覽量

62466 -

功率模塊

+關注

關注

10文章

457瀏覽量

45052 -

碳化硅

+關注

關注

25文章

2702瀏覽量

48892

原文標題:一種新型的SiC功率模塊多芯片并行封裝方法

文章出處:【微信號:芯長征科技,微信公眾號:芯長征科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

功率模塊引線鍵合界面溫度循環下的壽命預測

?晶圓直接鍵合及室溫鍵合技術研究進展

什么是Cu clip封裝?碳化硅功率模塊鍵合方式

IGBT模塊銀燒結工藝引線鍵合工藝研究

基于多堆疊直接鍵合銅單元的功率模塊封裝方法

基于多堆疊直接鍵合銅單元的功率模塊封裝方法

評論