答案是:Digital Discovery

口袋式高速邏輯分析儀

當(dāng)新入手一款Zynq開發(fā)板后,一般新手在串口輸出一個(gè)hello world,實(shí)現(xiàn)功能就可以了。而對(duì)于一些對(duì)于Zynq有一定了解的老手而言,往往則會(huì)去嘗試了解板上硬件的特性和時(shí)序,探究hello world輸出背后整個(gè)系統(tǒng)是如何運(yùn)作的。

事實(shí)上,對(duì)于一款新的Zynq板卡來說,在啟動(dòng)序列中QSPI傳輸?shù)乃俣炔皇且粋€(gè)明顯的規(guī)范,本文教程就將教你如何使用Digital Discovery口袋式高速邏輯分析儀來快速分析啟動(dòng)序列并確定時(shí)序。

01

硬件清單

-

Digital Discovery口袋式高速邏輯分析儀

-

帶有flash的Zynq開發(fā)板(本文中使用Digilent Zybo作為被測對(duì)象)

-

SOIC測試夾(若有最佳)

-

杜邦線

注:事實(shí)上,除了Digital Discovery之外,當(dāng)然你也可以用經(jīng)典的Digilent Analog Discovery 2來操作,后者同樣帶有邏輯分析儀功能。這里更為推薦使用Digital Discovery,有兩個(gè)原因:一是由于QSPI時(shí)鐘頻率很高,超過100MHz,因此所選的儀器需要具有足夠的采樣率。二是Digital Discovery具有512 MB的DDR,可以完成大規(guī)模數(shù)據(jù)存儲(chǔ)的要求。

02

連接Digital Discovery

連接關(guān)系如下:

|

QSPI 信號(hào) |

QSPI/測試夾引腳 |

DigitalDiscovery引腳 |

|

cs |

7 |

DIO0 |

|

clk |

16 |

DIO1 |

|

d0 |

15 |

DIO2 |

|

d1 |

8 |

DIO3 |

|

d2 |

9 |

DIO4 |

|

d3 |

1 |

DIO5 |

|

gnd |

10 |

Gnd |

在使用如上圖所示的杜邦線進(jìn)行連接時(shí),要注意保證信號(hào)完整性,避免串?dāng)_。在某些時(shí)候,需要將某個(gè)信號(hào)和地線進(jìn)行纏繞,如圖中的藍(lán)色cs信號(hào)就使用了接了地的黑線進(jìn)行了纏繞。

03

QSPI腳本

為了將QSPI的信號(hào)轉(zhuǎn)換成數(shù)據(jù),在邏輯分析儀的WaveForm軟件中增添了一個(gè)“定制”通道,并使用js語言編寫了一個(gè)“解釋器”。代碼如下:

// rgData: input, raw digital sample array// rgValue: output, decoded data array// rgFlag: output, decoded flag arrayvar c = rgData.length // c = number of raw samplesvar pClock = false; // previous cock signal levelvar iStart = 0; // used to keep track on word start indexvar cByte = 0; // byte count per transmissionvar cBits = 0; // bit countervar bValue = 0; // value variablevar fCmd = true;for(var i = 0; i < c; i++){ // for each sample? ? var s = rgData[i]; // current sample? ? var fSelect = 1&(s>>0); // pin0 is the select signal var fClock = 1&(s>>1); // pin1 is the clock signal var fData = 1&(s>>2); // pin2 is the data signal var fData4 = 0xF&(s>>2); // DIN 2-5 DQ 0-3 if(fSelect != 0){ // select active low // while select inactive reset our counters/variables iStart = i+1; // select might become active with next sample cByte = 0; cBits = 0; bValue = 0; pClock = false; fCmd = true; continue; } if(pClock == 0 && fClock != 0){ // sample on clock rising edge bValue <<= 4; // serial data bit, MSBit first? ? ?? ? ? bValue |= fData4;? ? ??? ? ?? ? ? ? ? ?? ? ? cBits++;? ? ?? ? ? if(cBits==2){ // when got the 8th bit of the word store it? ? ?? ? ? ? cByte++;? ? ?? ? ? ? // store rgValue/Flag from word start index to current sample position? ? ?? ? ? ? for(var j = iStart; j < i; j++){? ? ?? ? ? ? ? ? // Flag change will be visible on plot even when data remains constant.? ? ?? ? ? ? ? ? // This is useful in case we get more consecutive equal values.? ? ?? ? ? ? ? ? rgFlag[j] = cByte;? ? ?? ? ? ? ? ? rgValue[j] = bValue;? ? ?? ? ? ? ?}? ? ?? ? ? ? ?iStart = i+1; // next word might start after this sample? ? ?? ? ? ? ?cBits = 0; ?// reset bit count for the next byte? ? ?? ? ? ? ?bValue = 0; // reset value variable? ? ?? ? ? }? ? ??}? ? ??pClock = fClock; // previous clock level}

除了使用定制的“解釋器”外,我們還可以使用標(biāo)準(zhǔn)的SPI來分析那些沒有通過QSPI發(fā)送到指令,例如第一條讀取指令。

04

觸發(fā)與采樣

雖然QSPI的最高時(shí)鐘頻率是100MHz,但在啟動(dòng)過程中的最高頻率僅為25MHz。此外,整個(gè)啟動(dòng)過程大概需要700ms。因此對(duì)于同時(shí)滿足大量樣本和高速采樣率,這也正是選擇Digital Discovery的原因——200MHz的采樣速度可以在1.3s內(nèi)采樣268M的樣本數(shù)據(jù)。

采樣本身是十分浪費(fèi)資源的,這個(gè)過程需要使用16GB的電腦內(nèi)存,并且需要很長的時(shí)間來完成數(shù)據(jù)的處理。

觸發(fā)設(shè)置在CS信號(hào)的下降沿。

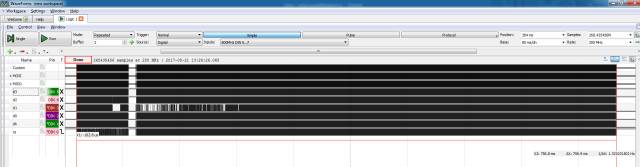

下圖是Waveforms中整個(gè)QSPI的傳輸過程。注意圖中采樣信號(hào)的短暫中斷,從這個(gè)時(shí)候起時(shí)鐘頻率由5.4MHz變?yōu)榱?5MHz。

05

啟動(dòng)傳輸

想要明白所傳輸?shù)臄?shù)據(jù)含義需要閱讀兩個(gè)文檔,一是Zynq技術(shù)參考手冊(www.xilinx.com/support/documentation/user_guides/ug585-Zynq-7000-TRM.pdf),另一個(gè)是flash memory的數(shù)據(jù)手冊(www.cypress.com/file/177966/download)。

Zynq與flash之間使用SPI協(xié)議進(jìn)行通信,Zynq發(fā)送通過D0向flash發(fā)送指令。所發(fā)送的第一條指令是0x03 0x00 0x00 0x20,含義是SPI讀,讀起始地址是0x20。Flash通過D1接收0x66 0x55 0x99 0xaa。Flash讀指令的含義在flash memeory的第85頁做了解釋。

(點(diǎn)擊可查看大圖)

在Zynq技術(shù)參考手冊的第170到179頁解釋了所回復(fù)指令的含義,簡單說這組字節(jié)告訴了Zynq內(nèi)存是支持QSPI的。還需要注意到,此時(shí)的SPI時(shí)鐘是5.405MHz,是一個(gè)比較低的速度。

從這點(diǎn)上看,確定了Zynq的內(nèi)存支持QSPI,并且所有的交互都將在這4條數(shù)據(jù)線上完成。例如,下一條指令是0x6b,跟在一個(gè)3個(gè)字節(jié)的地址的后面。0x6b表示一個(gè)quad讀指令,在8個(gè)時(shí)鐘周期后的QSPI解釋器上看到響應(yīng),這是虛擬字節(jié)。

(點(diǎn)擊可查看大圖)

在本例中,地址是0x1d,讀取7個(gè)字節(jié)。這些字節(jié)來自地址0x1d、0x1e、0x1f,它是中斷表的一部分,然后從地址0x20開始讀取4個(gè)字節(jié),這是在第一個(gè)SPI讀取時(shí)讀取的相同字節(jié)。

Znqy將繼續(xù)讀取字節(jié),地址逐漸增加,直到0x45,這是bootROM Header的結(jié)尾。

但是,由于我們無法訪問BootROM的代碼,其余的引導(dǎo)序列就不那么透明了。在某個(gè)時(shí)候,F(xiàn)SBL(第一階段引導(dǎo)加載程序)將開始運(yùn)行,最有可能的是當(dāng)SPI時(shí)鐘頻率變化到25 MHz的時(shí)候,如下所示,也就是在引導(dǎo)過程開始后的84毫秒。

(點(diǎn)擊可查看大圖)

然后,F(xiàn)SBL將讀取引導(dǎo)映像文件并分析它包含的不同分區(qū),包括配置Zynq PL部分的bit文件,在ARM中運(yùn)行的elf文件。

關(guān)于引導(dǎo)鏡像和啟動(dòng)過程可以閱讀這一用戶手冊(www.xilinx.com/support/documentation/user_guides/ug821-zynq-7000-swdev.pdf)。

-

FPGA

+關(guān)注

關(guān)注

1626文章

21670瀏覽量

601879 -

賽靈思

+關(guān)注

關(guān)注

32文章

1794瀏覽量

131166 -

Zynq板卡

+關(guān)注

關(guān)注

0文章

1瀏覽量

2063

原文標(biāo)題:如何以開掛的方式來查看Zynq啟動(dòng)順序?

文章出處:【微信號(hào):FPGA-EETrend,微信公眾號(hào):FPGA開發(fā)圈】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

冷機(jī)啟動(dòng)板卡時(shí),LMX2572鎖定時(shí)間在2分鐘以上,為什么?

如果設(shè)計(jì)一款桌面款的機(jī)器玩具,最吸引人的外觀與功能要有哪些?

51單片機(jī)(一款國產(chǎn)8位高性能Flash的接近感應(yīng)單片機(jī)XD08M3232體驗(yàn)感)

精準(zhǔn)時(shí)刻,掌控未來:解鎖新一代PCIe時(shí)鐘板卡!

人工智能模型公司Anthropic近日推出了一款Claude移動(dòng)端App

如何挑選一款性價(jià)比高的家用路由器

NVIC_SystemReset()導(dǎo)致系統(tǒng)掛死怎么解決?

基于ZYNQ FPGA構(gòu)建嵌入式的模擬計(jì)算板卡

通過JTAG啟動(dòng)Linux的方法和腳本

使用AD7490開發(fā)一款多通道數(shù)據(jù)采集的項(xiàng)目,在開發(fā)的過程中對(duì)于時(shí)序的疑問求解

介紹一款IDEA插件:Apipost-Helper-2.0

對(duì)于一款新的Zynq板卡來說,如何開掛啟動(dòng)程序

對(duì)于一款新的Zynq板卡來說,如何開掛啟動(dòng)程序

評(píng)論