原則:有硬件I2C、SPI時盡量用硬件操作,省去IO模擬繁瑣的時序調試。但在內部資源不夠時就要用IO模擬總線了。

關于短延時:

模擬時序時是否需要延時要看MCU與device的相對速度。比如I2C如果400K的速率和MCU動輒幾十M的速率不再一個量級,肯定要通過延時調整時序;但對于SPI因為其速度很高,甚至有的比單片機的速度還高,這時就沒必要延時了。

關于IO模擬的收發函數是否要合并成一個:

對于SPI因為是全雙工,所以可以分開,當然也可以合并成一個(發送時不需要返回值,而接收時此時參數是要發送的數據,返回值是要讀的值)

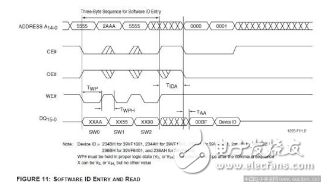

關于在什么跳變沿操作:

比如芯片手冊中說到在上升沿采樣/鎖定(也就是在搞定平之后值必須穩定),那么單個位bit的收發都應該在0->1之間進行操作。

關于時鐘極性和時鐘相位:

CPOL時鐘極性只是說明了空閑時總線的電平狀態:CPOL=1表明空閑時時鐘是搞定平;否則是低電平。

CPOA時鐘相位說明了在第幾個跳變沿進行采樣,CPOA=0表明在第一個沿進行采樣,否則在第二個沿。

-

IO

+關注

關注

0文章

435瀏覽量

39080 -

時鐘

+關注

關注

10文章

1720瀏覽量

131364 -

SPI

+關注

關注

17文章

1701瀏覽量

91327

原文標題:關于IO模擬時序(SPI)的注意事項

文章出處:【微信號:mcugeek,微信公眾號:MCU開發加油站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

FPGA設計中的時序分析及異步設計注意事項

通用IO結構注意事項是什么

低功耗配置IO的注意事項是什么

膽機使用的注意事項

PIC18Fxx單片機IO設置注意事項!

ADS8528、ADS8548和ADS8568時序注意事項

深度解析IO模擬時序(SPI)的注意事項

深度解析IO模擬時序(SPI)的注意事項

評論