時鐘抖動有幾種不同的類型和測量方法,以及相應的規格指標,但大多數硬件設計人員沒有時間去研究這些,因為對于電路板設計師而言,時鐘抖動規格指標的細微差別似乎是微不足道的瑣碎之事。設計師往往更把精力集中在眼前較重大的設計任務,以優先級順序這些是針對FPGA邏輯、微處理器綜合體、數據層面交換結構、控制層面交換架構、RF信號鏈路、電源、互連互通問題、設計仿真、建模等設計任務。

因此,設計人員必須假定來自各個芯片廠商的參考時鐘抖動規格指標與他們預期使用的這些器件相關,并且這些規格指標已經被完全和正確地確定。

但如果沒有一些基本準則可循,設計師可能會指定過高的時鐘抖動要求,導致采用更昂貴的時鐘器件并增大不必要的物料成本(BOM)。或者出現更糟糕的情況,針對某特定應用,把時鐘抖動要求降低,相應的錯誤可能會超出給定應用可接受的誤差率水平。這種情況只能在產品開發周期后期在對最初原型板進行性能指標測試時才可以發現,因此很可能會影響最終產品的發布時間。

最根本的檢查點

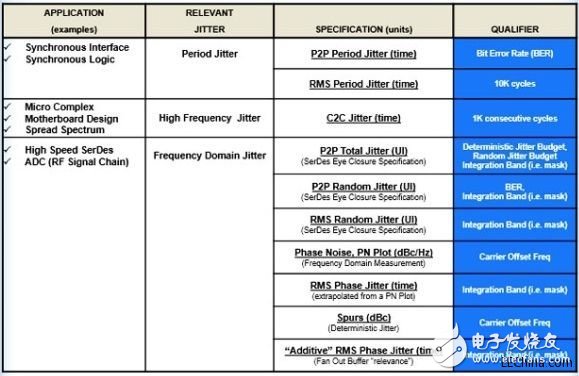

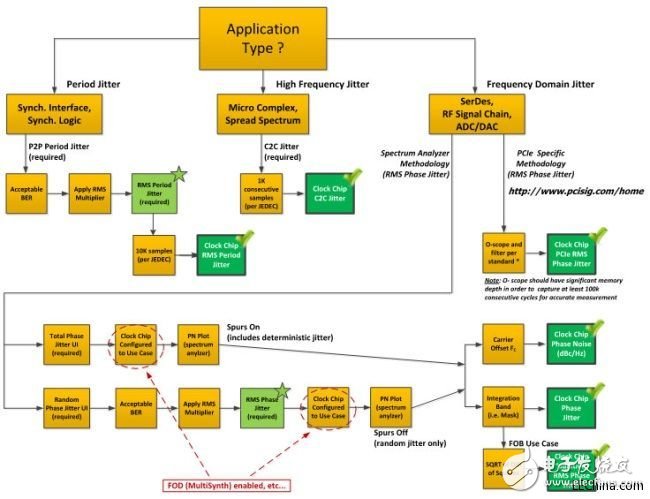

設計師要考慮的第一個也是最根本的檢查點是確定針對特定應用最相關的時鐘抖動類型。表1總結了根據應用類型的一些抖動分類,以及相應的規格指標限定。

表1:與應用相關的抖動。

周期抖動是可以最直觀理解的抖動類型,它簡單地指與周期理想值(或平均值)的偏差,是同步接口和邏輯設計相關的抖動類型,應用案例包括與同步存儲器端接的微處理器接口,或FPGA內部的同步狀態機設計。

隨著時鐘周期縮短或擴大,可以對同步設計的建立時間或者保持時間產生巨大影響,這也是為什么周期抖動與這些類型的應用相關的原因。

高頻抖動,尤其是相鄰周期(C2C)抖動,是與擴頻時鐘相關的抖動類型。擴頻時鐘有意誘發低頻抖動來減輕電磁干擾(EMI),這些都是傳統上消費電子產品所擔心的。但是,由于擴頻是低頻率抖動,它不會影響相鄰周期抖動測量。出于這個原因,相鄰周期抖動規格指標可用于量化擴頻時鐘的抖動性能。

仔細分析頻域抖動

重要的是要特別注意頻域抖動以及它在高速串行通信中的適用性。具體來說,針對高速串行/解串器(SerDes)設計的參考時鐘抖動要求應該詳盡。頻域抖動是最不被理解的抖動類型,因此也最容易導致出現一些常見的電路板設計缺陷。

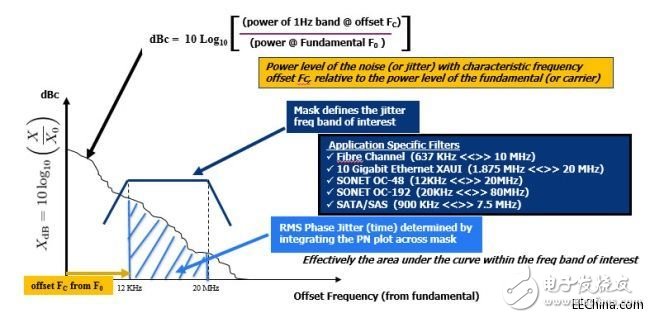

圖1所示為一個通過頻譜分析儀生成的相位噪聲(PN)曲線,頻譜分析儀可捕獲時鐘信號的頻譜內容,因此有助于了解時鐘抖動的頻率特性。這對于說明相位擾動的隨機性也很有幫助,相位擾動的隨機性意味著隨機頻率擾動,并且這反過來又意味著隨機周期擾動。

圖1:相位噪聲(PN)曲線常用來表示頻域中的時鐘抖動。

因此,PN曲線代表的是隨機時鐘周期抖動,但是在頻域。從數學上看,它是時鐘信號的噪聲(即抖動)相對于在特定基頻頻率偏差下的時鐘基頻F0的強度。

在特定頻率偏差下的抖動強度可以表明該抖動值多長時間發生一次,因此一個PN曲線表明一個特定的隨機頻率偏差多長時間發生一次。抖動強度與載波的比值以dBc/Hz表示,dBc/Hz值越低越好,意味著更小的抖動強度。

均方根(RMS)相位抖動是由PN曲線外推得到的抖動量化值,它不能與時域抖動規格指標的RMS周期抖動混淆。轉換的RMS相位抖動值在很大程度上是一個積分函數,其值取決于根據該PN曲線下的區域面積。

但是這個面積需要由一個積分區間來界定,或者被通常稱為“遮罩(Mask)”。Mask是與特定應用的傳遞函數而相關聯,其目的是限制或阻止抖動量化值在一個頻率范圍內,該應用的傳遞函數不再進行過濾。這意味著,任何RMS相位抖動要求必須由所關注的積分范圍限定。

一個PN曲線,以及相應的RMS相位抖動量化值,是串行/解串器(SerDes)應用相關的時鐘抖動類型。同步數字體系(SDH)、同步光纖網絡(SONET)、以太網、PCI Express(PCIe)、串行RapidIO(SRIO)和SMPTE(美國電影電視工程師協會)等工業串行標準都利用這種時鐘抖動類型用于界定必要的參考時鐘抖動。

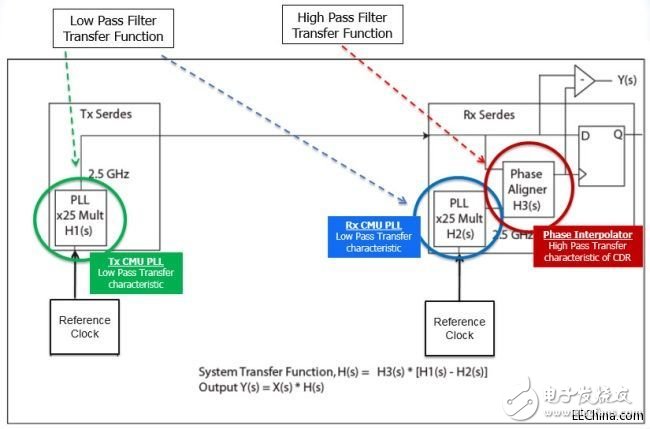

作為參考,一個具有代表性的SerDes通信信道如圖2所示。鎖相環(PLL)是輸入時鐘抖動固有的低通濾波器,這樣, 發射器(Tx)的SerDes時鐘倍增單元(CMU)PLL用作參考時鐘抖動的低通濾波器。

圖2:一個具有代表性的高速串行通信信道。

此時鐘的高頻抖動不被轉移到該PLL的輸出,因此,不會對SerDes的輸出抖動產生任何影響。這個Tx CMU鎖相環的低通濾波器特征確定了所感興趣積分頻帶的上限轉角頻率(corner frequency)。

以類似的方式,用于接收器SerDes參考時鐘由內部接收器SerDes CMU鎖相環倍乘。該時鐘然后用于基于相位內插器的時鐘和數據恢復(CDR)電路,其可作為參考時鐘抖動的高通濾波器。

因此,這個時鐘的低頻抖動不會傳遞到用于CDR的相位對準器輸出。接收器相位內插器的高通濾波器特征確定了感興趣積分頻帶的下限轉角頻率。

所有這些效應會界定具體串行標準的SerDes傳遞函數,以及那些確定感興趣的頻帶或者Mask,例如用于10G以太網的1.875MHz到20MHz的頻帶。

芯片廠商的規格指標并不一致

除了許多不同的抖動類型和細微差別,芯片制造商如何為他們的器件確定所需的時鐘抖動也有很多的不確定性。 SerDes芯片廠商為他們的元件確定所需的參考時鐘抖動,但是物理層、FPGA和處理器等器件規格指標則不一定與行業串行接口標準的方法學和測量細節等保持一致。

例如,大部分網絡通信標準(如千兆以太網,10千兆以太網等)指定峰-峰(P2P)值總抖動作為一個單位間隔(UI)的百分比,其中一個UI在給定串行標準中相當于時間域1比特間隔。但是峰-峰值總抖動UI實際上是一個SerDes眼圖關閉(eye closure)規格指標,以符合可接受的比特誤碼率(BER),根據工業串行標準其通常是10-12。

這些標準并沒有界定總抖動UI預算有多少被分配給互連、光學、串行解串器,或驅動SerDes的參考時鐘。其結果是,電路板設計人員只能聽命于芯片供應商以及在他們的數據表中規定的參考時鐘抖動。通常,這些規格指標都過于保守,把大多數抖動預算給予了集成的SerDes,為需要驅動SerDes的參考時鐘只留下少許。

使問題更加復雜的是,來自時鐘芯片廠商的抖動規格指標可能是模糊的,也不一定完整。一些供應商對于時鐘產品的描述(specmanship)建立在不適當規格指標和測量結果基礎上,通常不適合于目標應用,對于給定的規格指標會產生不一致并缺失關鍵的限定。

常見的抖動陷阱

對于電路板設計人員來說,有許多容易導致錯誤的陷阱。本節會擴展來討論一些下面列出的常見陷阱的更多詳細信息:

P2P隨機抖動規格指標沒有針對目標應用BER限定

把針對通信應用而設計的時鐘抖動規格指標和方法學應用于PCIe端口

PN曲線生成時關斷雜散波以便滿足總相位抖動要求( 通過使用隨機RMS相位抖動測量忽略了確定性抖動)

抖動的測量/確定僅僅是針對器件,而不是針對給定應用(如整數模式下的w/內置 MultiSynth分頻器)的案例配置

添加RMS相位抖動(Additive RMS phase jitter)的測量作為輸入和輸出抖動之間的簡單差值,而不是輸入和輸出抖動平方差的平方根值

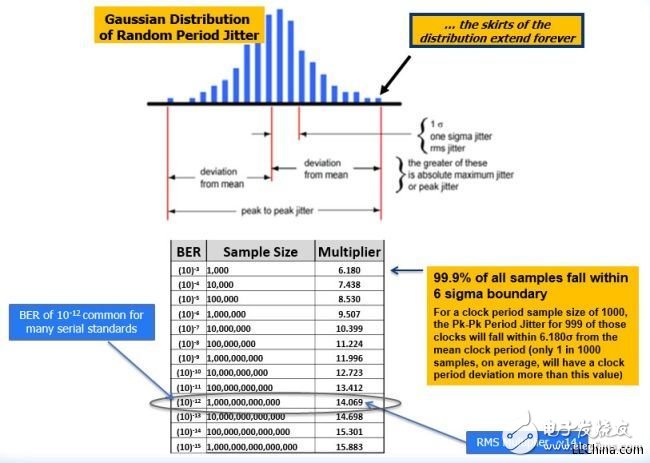

例如,圖3所示隨機周期抖動的高斯分布裙邊會無限延伸下去,這是因為隨機抖動沒有邊界,因此,實際測量P2P周期抖動絕對最大值并不現實。然而,在高斯分布上超過一個點的抖動可以給定一個概率。 BER依特定應用而定,并且通常用于此目的。

圖3:隨機周期抖動的高斯分布裙邊無限延伸。

沒有芯片供應商提供的可接受的BER,P2P周期抖動規格指標毫無意義。然而,這個限定往往難以從器件的數據表中看到。對于給定的應用,如果已知道可接受的BER,該給定應用的RMS周期抖動之后可以計算出來。所以,重要的是設計者必須要知道他們應用的正確BER。此外,請注意這種方法不是針對于周期抖動,因為它可用于計算各種類型的RMS抖動。作為例子,一個RMS相位抖動的計算如下所示:

考慮到10GE PHY需要的隨機相位抖動UI=0.18 UI

。。。 因為比特率是10.3125Gbps,1 UI=96.9pS

。。。假定給定應用可接受的BER是10-12

那么,所需的相應RMS相位抖動的計算公式為:

[(0.18)*(96.9pS)]÷(14.069) = 1.24pS

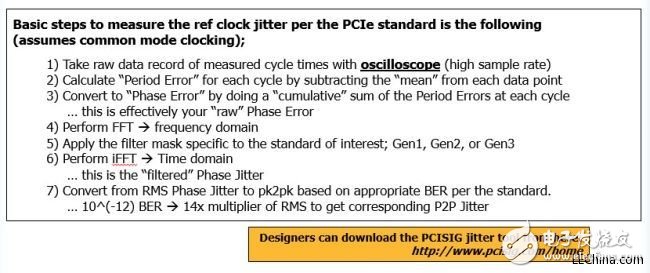

PCIe已經成為通信應用普遍的控制層面接口,以太網物理層等器件集成PCIe端口用于連接帶外的控制層面微處理器(micro)。至少一個著名的以太網PHY廠商已經為他們的PCIe參考時鐘確定RMS相位抖動,其方式類似于在同樣器件中他們為以太網端口確定RMS相位抖動,通過由頻譜分析儀所產生的相位噪聲曲線進行有效地外延。但是,這種方式不符合PCIe標準抖動方法,如圖4中可詳細說明。

圖4: 針對PCIe標準測量參考時鐘抖動的7個步驟。

按照PCIe標準測量參考時鐘抖動的基本步驟如下:

(假定為常見模式時鐘)

1) 用示波器(高取樣率)得到所測周期時間的初始數據記錄

2) 通過每個數據點減去平均值來計算針對每個周期的‘周期誤差’

3) 通過對每個周期的周期誤差進行累積求和,從而轉化為‘相位誤差’

……得到您的有效‘初始’相位誤差

4) 通過快速傅里葉變換(FFT)轉變到頻域

5) 把特定的遮罩(mask)應用于感興趣的標準,Gen1,Gen2,或者Gen3

6) 進行快速傅里葉逆變換(iFFT)操作再變換到時域

……得到‘過濾的’相位誤差

7) 根據適當的標準誤碼率(BER)要求把RMS相位抖動轉換為峰值到峰值抖動

……10-12誤碼率,通過RMS的14X乘法器得到相應的峰值到峰值抖動

相反,PCIe方法是采用示波器測量得到的原始周期樣本,然后應用FFT、濾波器和iFFT步驟來得出適當的RMS相位抖動測量。重要的是要注意到這兩種不同的方法可以產生完全不同的結果。

因此,設計人員可能會誤認為設計的時鐘器件達到或超過了PCIe參考時鐘抖動規格指標或者標準,但是這些器件卻不足以驅動PCIe端口,原因是這些PHY廠家采用了不同的方法和/或過濾器來確定所需的參考時鐘抖動。

如先前所討論的,P2P總抖動(UI)是特定于SerDes的數據信號。這包括確定性和隨機抖動對于數據信號眼圖的貢獻。人們普遍認為,在SerDes鏈路的確定性抖動很大程度上與鏈路本身和其他系統障礙有關。

隨機抖動主要可歸因于SerDes外部參考時鐘和SerDes內部的PLL。但我們知道,參考時鐘也具有一定量的確定性抖動。此外,許多PHY供應商的數據表并沒有區分列出驅動他們SerDes參考時鐘的隨機與確定性抖動要求。由于這些原因,另一種常見的設計陷阱是使用PN曲線來量化時鐘器件的總相位抖動,其中包括確定性抖動,但雜散被關斷 (雜散是“周期性雜散噪聲”的簡寫,代表了時鐘的確定性抖動)。此確定性抖動可來源于電路板設計本身和/或時鐘芯片,串擾、電磁干擾(EMI)、開關電源噪聲、和PLL小數反饋分頻器都可以是這種確定性抖動的來源。

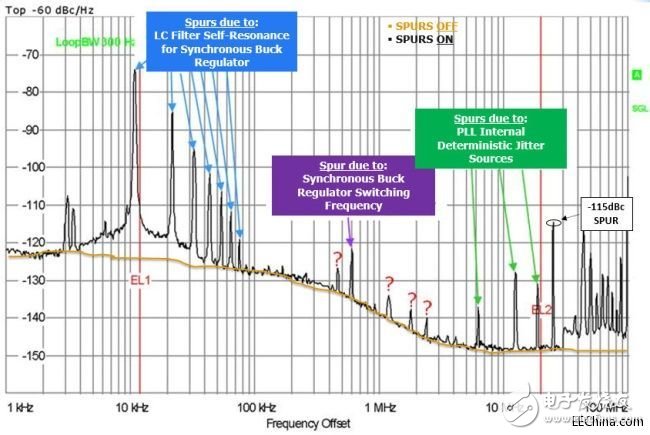

對于圖5中所示的PN曲線例子,其特殊的電路板設計使在PLL輸出端測得顯著的雜散內容。不幸的是,這些雜散噪聲處在該應用感興趣的12kHz至20MHz積分范圍內。因此,參考時鐘的總相位抖動已經超出了SerDes芯片供應商的規格指標,結果是較高的BER。采用EMI嗅探器(sniffer)分析這些問題的根本原因,發現這種雜散的內容可追溯到用于給PLL供電的同步降壓開關穩壓器,通過電路板布局修改和無源元件的變化可以減輕這一問題。

圖5:具有雜散噪聲的 PN曲線示例。

然而,某些雜散內容來自PLL時鐘器件本身。重要的是要記住,任何時鐘合成器可以產生許多不需要的和與差頻率,它們的強度可能很大足以顯著出現在PN曲線上。

當今優秀的PLL設計都采用先進的硅設計技術。這些進展有助于減少內在產生的隨機和確定性(雜散)抖動。但對于抖動關鍵的板載時鐘,設計師需要義不容辭地與定時器件廠商驗證給定的時鐘器件其相應的相位抖動規格指標是基于雜散導通時得到的PN曲線。

一個流程圖讓你步入正軌

圖6中所示的流程圖旨在針對具體應用把電路板設計人員引導到正確的抖動規格指標,從而正確地選擇時鐘芯片。

圖6:流程圖有助于針對您的應用來確定正確的抖動。

首先要確定應用類型。它是一個同步接口或同步邏輯設計、一個微處理器參考時鐘規格指標或擴頻時鐘、一個高速串行通信或串行/解串器設計?在許多電路板設計中,往往所有這些應用類型都需要進行處理,而且它們都有不同的抖動要求。

對于同步接口或同步邏輯設計,所涉及的應該是周期抖動。你是從P2P周期抖動規格指標開始工作嗎?如果是這樣,那么你需要確定兩個關鍵限定:首先,按照JEDEC(電子器件工程聯合委員會),你在使用的芯片P2P周期抖動是基于10K樣本大小。其次,芯片供應商為您提供針對他們規格指標的假定BER。有了這兩個限定,就可以得出一個相應的RMS周期抖動規格指標以便選擇適當的時鐘器件。

如果它是一個消費類電子產品的應用來實現擴頻,那么你可能需要使用相鄰周期抖動規格指標。按照JEDEC標準,假定相鄰周期抖動是在跨越連續1000個周期進行測定。你需要確認是不是這種情況,之后你會有一個有效的相鄰周期抖動規格指標來確定相應的時鐘芯片。

如果它是一個高速串行通信設計,那么你應該首先詢問是否串行標準采用了傳統的擴展頻譜分析儀方法來量化相位噪聲。此外,重要的是要注意PHY廠商針對規格指標到底提供了什么,是P2P總抖動UI,還是P2P隨機抖動UI?

需要記住的是RMS只針對于隨機抖動,需要將隨機抖動要求被BER乘數相除以便得到相應的RMS隨機抖動UI。對于隨機抖動,你可以使用一個關斷雜散的PN曲線,通過積分得到RMS相位抖動值。但是,如果采用一個接通雜散的PN曲線來得到確定性抖動,然后在Mask積分,那么得到的相應值不再是RMS,而是總的相位抖動。

該流程圖的目的是針對您的應用引導您通過一個系統化的途徑來確定正確的抖動,流程的設計是專門用來避免在本文中詳細介紹的常見電路板設計陷阱。

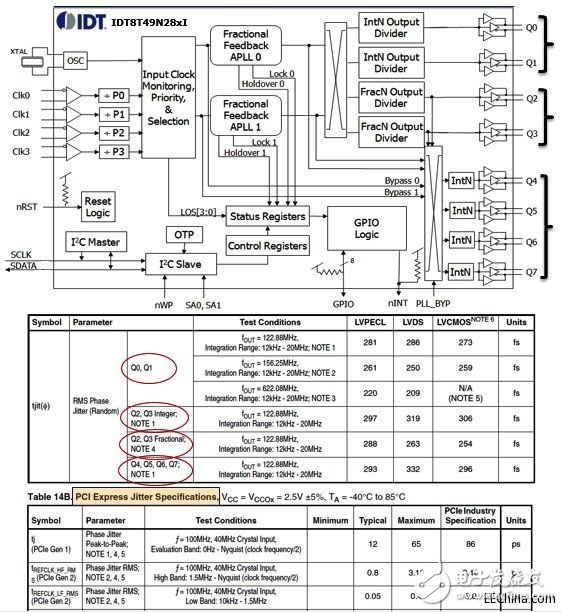

一個有用的時鐘器件規格指標應該能夠描繪出不同的輸出結構和每個結構的相應抖動能力,它還可以針對本文中介紹的不同抖動類型提供規格指標,使設計人員可以為他們的特定應用做好限定。作為一個例子,可以考慮圖7中所示的通用頻率轉換器(UFT)。

圖7:IDT8T49N28X通用頻率轉換器。

這種可配置的時鐘器件有幾個先進的功能,非常適合于通信線路卡(line-card)應用。它能夠以單一器件提供令人印象深刻的高性能(例如低相位噪聲)和靈活性。為了實現這種靈活性,該器件采用了一種混合有基于整數和分數的輸出分頻器,具有為每個輸出類型對應的RMS相位抖動差值,詳見本器件規格指標。此外,該器件的數據表按照之前提到的PCISIG方法學,以一個單獨的表格突出了PCIe相位抖動性能,從而注意到了該串行接口標準中方法學的差異。

重要的是要認識到,一個可配置時鐘數據表并不能夠覆蓋所有的應用案例情況。因此,鼓勵設計人員針對特定的應用案例去尋求相應的抖動性能,因為其結果可能略有不同。

-

電路板設計

+關注

關注

1文章

127瀏覽量

16478 -

微處理器

+關注

關注

11文章

2247瀏覽量

82319 -

時鐘抖動

+關注

關注

1文章

62瀏覽量

15917

發布評論請先 登錄

相關推薦

嵌入式系統智鍵盤軟件設計問題解決方案

嵌入式系統高級C語言編程

嵌入式系統與嵌入式PLC

【嵌入式】基于ARM的嵌入式Linux開發總結

C和嵌入式

嵌入式學習之路:初識嵌入式

如何避開嵌入式設計的抖動陷阱

如何避開嵌入式設計的抖動陷阱

評論