一、微封裝技術(shù)的發(fā)展

隨著航空航天系統(tǒng)對(duì)于小型化、低功耗、高性能、高可靠性的要求,傳統(tǒng)PCB板上系統(tǒng)(SOB)的設(shè)計(jì)方案的缺點(diǎn)越來越明顯。由于芯片、模塊的體積和功耗的限制,PCB板尺寸和功耗不能無限制減小。單個(gè)芯片的封裝尺寸通常在mm到cm量級(jí),但PCB板上的走線長度通常在1cm~50cm量級(jí),過大的封裝和走線造成損耗大、寄生參數(shù)多,限制了系統(tǒng)性能的提升。同時(shí)由于系統(tǒng)功能復(fù)雜,使用大量分立器件造成系統(tǒng)故障點(diǎn)多,整機(jī)可靠性降低。

為了解決傳統(tǒng)板上系統(tǒng)設(shè)計(jì)的弊端,航空航天領(lǐng)域也逐漸開始采用在通信、計(jì)算機(jī)及消費(fèi)類電子廣泛使用的微封裝、微組裝技術(shù),來提高系統(tǒng)的集成度和可靠性。

典型的微封裝、微組裝技術(shù)有SoC、MCM、SiP、SoP等。

SoC技術(shù)最早出現(xiàn)于上世紀(jì)80年代,用于把多個(gè)功能模塊集成到一個(gè)晶片上,主要用于通信、計(jì)算機(jī)、網(wǎng)絡(luò)等高性能領(lǐng)域,典型的如NVIDIA的Tegra, Freescale的Vybrid以及下圖所示Intel的Core系列多核處理器等。SOC的特點(diǎn)是把相同工藝的多個(gè)功能模塊集成到1個(gè)單一晶片上,系統(tǒng)性能高、功耗低,是商用一體化芯片解決方案的首選. 其基本要求是要在同種半導(dǎo)體材料上實(shí)現(xiàn), 而對(duì)于綜合了GaAs、GaN及鍺硅工藝的航空航天領(lǐng)域,則較難以實(shí)現(xiàn)。

MCM也是上世紀(jì)80年代出現(xiàn)的一種封裝技術(shù),其特點(diǎn)是把多個(gè)芯片甚至裸Die通過金絲鍵合線以及基底材料集成到一個(gè)封裝里。MCM封裝后的模塊尺寸和成本可以降低很多,同時(shí)由于模塊內(nèi)的各個(gè)芯片不需要單獨(dú)封裝,且芯片間走線更短,所以可以提供更好的傳輸性能。另外由于集成度高,容易進(jìn)行集中的屏蔽和保護(hù),所以比起采用分立器件系統(tǒng)可靠性更高。 MCM技術(shù)可以把不同工藝的晶片集成在一個(gè)封裝里,因此使用非常靈活,可以構(gòu)建模擬、數(shù)字、射頻以及電阻、電容等無源器件的混合系統(tǒng)。下圖分別是IBM和波音公司開發(fā)的兩款MCM芯片。

圖1:IBM Power5處理器和Boeing公司的MCM控制芯片

SiP是上世紀(jì)90年代出現(xiàn)的封裝技術(shù),可以認(rèn)為是MCM技術(shù)的升級(jí)版。SiP封裝技術(shù)除了像MCM一樣可以進(jìn)行多個(gè)不同工藝晶片的平面封裝以外,還可以進(jìn)行裸Die或者封裝的立體3D堆疊,進(jìn)一步提高了封裝密度。目前廣泛應(yīng)用于手機(jī)、PAD等便攜式消費(fèi)電子設(shè)備里,典型的如Apple公司在iWatch里的核心模塊以及相控陣?yán)走_(dá)里使用的T/R模塊等。

圖2:iWatch里使用的SiP模塊及射頻T/R SiP模塊

SoP是本世紀(jì)初出現(xiàn)的一種封裝技術(shù),可以認(rèn)為是SiP技術(shù)的進(jìn)一步升級(jí)。除了像SiP一樣可以完成多種晶片、無源器件的3D堆疊和封裝以外,還采用了薄膜技術(shù)和納米材料把一些常用的無源器件如電阻、電容、濾波器、波導(dǎo)、耦合器、天線甚至生物傳感器等直接集成到封裝基底上。這使得基底上的走線長度從mm量級(jí)減小到了um甚至nm量級(jí),進(jìn)一步提高了系統(tǒng)性能和集成度。下圖是一個(gè)SoP芯片應(yīng)用的例子。

圖3:典型的SoP系統(tǒng)

由此可見,SoC、MCM、SiP、SoP等技術(shù)各有自己的特點(diǎn)和應(yīng)用領(lǐng)域。為了實(shí)現(xiàn)航天電子系統(tǒng)的小型化并提高可靠性,MCM和SIP是特別適合系統(tǒng)級(jí)小型化設(shè)計(jì)可以采用的微封裝、微組裝技術(shù),同時(shí)可以重點(diǎn)關(guān)注SOP技術(shù)的發(fā)展并做相應(yīng)的技術(shù)儲(chǔ)備。

二、微封裝技術(shù)的挑戰(zhàn)

微封裝、微組裝技術(shù)可以帶來顯著的集成度和系統(tǒng)性能的提高,但是由于采用和傳統(tǒng)的板級(jí)系統(tǒng)設(shè)計(jì)完全不同的技術(shù)和工藝,其設(shè)計(jì)和測試難度很大。尤其對(duì)于空間等高輻射、高可靠性應(yīng)用的場合來說,如何進(jìn)行可靠性設(shè)計(jì)以及全面有效的功能、性能驗(yàn)證尤其重要。在空間應(yīng)用中采用微封裝技術(shù)的主要難點(diǎn)和挑戰(zhàn)體現(xiàn)在以下幾個(gè)方面。

1. 微封裝材料、互連技術(shù)的設(shè)計(jì)和仿真:在空間應(yīng)用中,輻射、溫度、振動(dòng)等工作環(huán)境惡劣,一顆衛(wèi)星的工作周期可能要20年以上并幾乎不可維修,使得其對(duì)于可靠性的要求很高,因此封裝材料和互連工藝的選擇至關(guān)重要。以基底材料來說,可能有塑料、樹脂、鋁、陶瓷等多種選擇;以電介質(zhì)材料來說,適合空間等惡劣環(huán)境應(yīng)用BCB(苯并環(huán)丁烯)材料、Riston和Kapton材料等;以互連技術(shù)來說,可能有球狀焊接、金絲鍵合、硅穿孔(TSV)等方式,而以主流的金絲鍵合方式來說又存在著多種的鍵合線結(jié)構(gòu)。因此,對(duì)各種材料特性、加工工藝、走線拓?fù)溥M(jìn)行仿真并確定設(shè)計(jì)方案,同時(shí)確保滿足空間環(huán)境的電、熱和機(jī)械性能要求,就成為系統(tǒng)設(shè)計(jì)的難點(diǎn)和關(guān)鍵技術(shù)。

2. 關(guān)鍵芯片的功能和性能驗(yàn)證:微封裝模塊是把不同功能的芯片甚至裸Die封裝在一起并通過金絲鍵合在一起,整個(gè)模塊內(nèi)部可能會(huì)有幾個(gè)甚至幾十個(gè)子功能模塊的芯片。由于航天級(jí)芯片的成本都非常高,如果封裝完后才發(fā)現(xiàn)其中某個(gè)芯片有問題,會(huì)造成整個(gè)模塊的報(bào)廢,因此封裝前芯片功能和性能的檢測對(duì)于提高最終的成品率和降低成本至關(guān)重要。

3. 微封裝模塊的系統(tǒng)功能和性能測試:大部分微封裝模塊是把兩個(gè)或多個(gè)功能模塊如模擬、射頻、數(shù)字、電源等用金屬或陶瓷材料封裝在一起。當(dāng)各個(gè)功能模塊被封裝在一起以后,需要對(duì)微封裝模塊的功能和性能進(jìn)行全面的測試,以確保封裝后的模塊功能和性能滿足設(shè)計(jì)要求。對(duì)高可靠性應(yīng)用場合,還需要按照實(shí)際工作要求進(jìn)行環(huán)境老化試驗(yàn)和篩選,以確保在未來幾年甚至幾十年內(nèi)能夠可靠有效地工作,這就使得微封裝模塊的系統(tǒng)功能和性能測試至關(guān)重要。

三、關(guān)鍵功能模塊表征

1. 高速并串轉(zhuǎn)換芯片的功能和性能測試

并行總線是數(shù)字電路里最早也是最普遍采用的總線結(jié)構(gòu)。為了解決并行總線占用尺寸過大且對(duì)布線等長要求過于苛刻的問題,隨著芯片技術(shù)的發(fā)展和速度的提升,越來越多的數(shù)字接口開始采用串行總線。

為了便于把多路并行的數(shù)字信號(hào)用盡可能少的電纜傳輸出去,并提供更好的噪聲抑制能力及傳輸距離,一般會(huì)通過高速TRANSCEIVER芯片把多路并行數(shù)據(jù)復(fù)用在一起并通過高速低壓差分信號(hào)進(jìn)行傳輸。

數(shù)據(jù)速率提高以后,對(duì)于阻抗匹配、線路損耗和抖動(dòng)的要求就更高,稍不注意就很容易產(chǎn)生信號(hào)質(zhì)量的問題。對(duì)于高速串行收發(fā)芯片的測試,主要涉及以下幾個(gè)方面:

* 高速串行芯片發(fā)送端信號(hào)質(zhì)量測試: 包括輸出幅度、眼圖、抖動(dòng)、上升時(shí)間、下降時(shí)間等;

* 高速串行芯片接收端抖動(dòng)容限、噪聲容限、靈敏度、系統(tǒng)誤碼率測試,用于驗(yàn)證系統(tǒng)實(shí)際傳輸?shù)恼`碼率、接收容限等。

* 芯片工作電壓、電流、功耗等

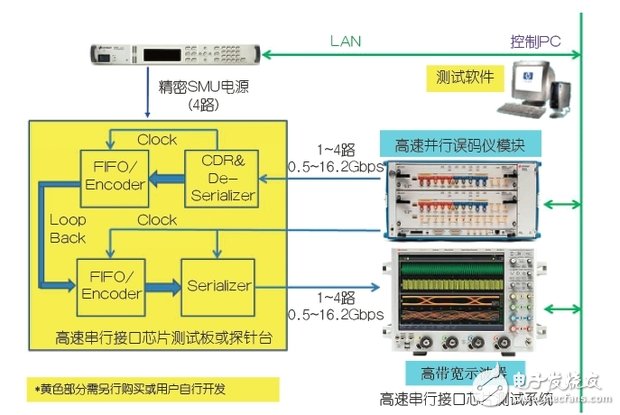

以下是整個(gè)高速收發(fā)芯片傳輸系統(tǒng)的測試平臺(tái)構(gòu)成。

圖4

測試中使用高性能的多通道誤碼儀產(chǎn)生多路串行激勵(lì)信號(hào)和時(shí)鐘送給被測芯片,數(shù)據(jù)經(jīng)環(huán)回后回送誤碼儀進(jìn)行誤碼率統(tǒng)計(jì)或者接高帶寬示波器進(jìn)行信號(hào)質(zhì)量分析。誤碼率測試過程中可以在信號(hào)上加入隨機(jī)抖動(dòng)、確定性抖動(dòng)、共模噪聲、差模噪聲、ISI碼間干擾能影響以驗(yàn)證接收端對(duì)于惡劣信號(hào)的容忍能力。

2. 衛(wèi)星相機(jī)成像的電子系統(tǒng)微封裝模塊整體測試方案

其測試系統(tǒng)應(yīng)包含以下功能。

* CCD信號(hào)的模擬:應(yīng)能模擬CCD器件輸出的模擬信號(hào),并能靈活增加噪聲以驗(yàn)證被測模塊提取和恢復(fù)圖像數(shù)據(jù)的能力。

* 高速輸出數(shù)據(jù)的采集和分析:應(yīng)能采集捕獲被測模塊處理后的高速數(shù)據(jù)輸出,并能夠根據(jù)數(shù)據(jù)結(jié)構(gòu)提取數(shù)據(jù)里的圖像信息,以驗(yàn)證模塊在不同工作狀態(tài)下的功能和性能。

* 模擬輸出信號(hào)的分析:對(duì)CCD驅(qū)動(dòng)時(shí)鐘、電機(jī)/快門等驅(qū)動(dòng)信號(hào)的幅度、頻率、占空比、脈沖寬度等進(jìn)行測量和分析。

* 接口控制電路:應(yīng)能控制模塊進(jìn)入正常工作狀態(tài)。

* 模塊功耗和電源抗擾度測試:應(yīng)能對(duì)模塊在不同工作狀態(tài)下的電壓、電流、功耗做記錄,并能夠模擬電壓跌落、電源紋波、上下電時(shí)序變化等異常情況,驗(yàn)證模塊在極端情況下的工作狀態(tài)

圖5:CCD相機(jī)SiP模塊測試系統(tǒng)

測試中用高性能的AWG任意波形發(fā)生模塊模擬產(chǎn)生CCD輸出的視頻模擬信號(hào),經(jīng)被測模塊采集和處理后以高速數(shù)字形式輸出。如果是并行數(shù)據(jù)捕獲高速并行數(shù)據(jù),可以用高速邏輯分析儀模塊捕獲分析;如果是多路高速串行數(shù)據(jù),可以用并行誤碼儀的輸入端進(jìn)行時(shí)鐘恢復(fù)并捕獲數(shù)據(jù)。測試中要求AWG模塊的信噪比、動(dòng)態(tài)范圍、帶寬等指標(biāo)能滿足系統(tǒng)信噪比測試要求,可以靈活添加噪聲等干擾因素,并有足夠深的內(nèi)存以產(chǎn)生整視頻幀的信號(hào)。邏輯分析儀應(yīng)有足夠高的狀態(tài)采樣速率和內(nèi)存深度,誤碼儀應(yīng)有多路串行數(shù)據(jù)輸入能力、時(shí)鐘恢復(fù)能力、高速信號(hào)均衡能力以及足夠的內(nèi)存深度。

-

SiP

+關(guān)注

關(guān)注

5文章

499瀏覽量

105264 -

衛(wèi)星

+關(guān)注

關(guān)注

18文章

1702瀏覽量

66907

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

微封裝技術(shù)對(duì)減輕衛(wèi)星載荷的重要性

微封裝技術(shù)對(duì)減輕衛(wèi)星載荷的重要性

評(píng)論