Mentor Graphics宣布其新的Mentor EZ-VIP PCI Express驗(yàn)證IP的即時(shí)可用性。這一新的驗(yàn)證IP (VIP)可將ASIC(應(yīng)用程序特定集成電路)和FPGA(現(xiàn)場可編程門陣列)設(shè)計(jì)驗(yàn)證的測試平臺構(gòu)建時(shí)間減少多達(dá)10倍。

驗(yàn)證IP旨在通過為常見協(xié)議和架構(gòu)提供可復(fù)用構(gòu)建模塊來幫助工程師減少構(gòu)建測試平臺所花費(fèi)的時(shí)間。然而,即使是標(biāo)準(zhǔn)協(xié)議和常見架構(gòu),其配置和實(shí)施也可能會因設(shè)計(jì)而異。因此,傳統(tǒng)的VIP元件可能需要數(shù)天甚至數(shù)周來準(zhǔn)備模擬或仿真測試平臺。

“在移動(dòng)、網(wǎng)絡(luò)及服務(wù)器SoC中使用ARMv8-A架構(gòu)和ARM CoreLink高速緩存一致性互連進(jìn)行設(shè)計(jì)時(shí),我們的合作伙伴可以選擇使用PCIe根聯(lián)合體解決方案,”ARM系統(tǒng)和軟件組總監(jiān)Jim Wallace說,“ARM一直使用在Questa和Veloce上運(yùn)行的Mentor PCIe VIP庫來幫助驗(yàn)證PCIe與ARM AMBA接口域之間的關(guān)鍵交互,以實(shí)現(xiàn)快速部署和準(zhǔn)確的協(xié)議檢查。”

與傳統(tǒng)的驗(yàn)證IP不同,Mentor的新PCIe EZ-VIP是“設(shè)計(jì)感知型”產(chǎn)品,可消除測試平臺裝配過程中的多個(gè)耗時(shí)步驟。這使驗(yàn)證工程師能夠更快地配置和實(shí)施過去繁瑣的設(shè)置任務(wù),以直接產(chǎn)生高價(jià)值場景,從而將曾經(jīng)需要數(shù)天或數(shù)周的過程減少到幾個(gè)小時(shí)。

“我們很高興與Mentor合作,為驗(yàn)證PCIe EZ-VIP提供支持,”PLDA的CTO Stephane Hauradou說,“成為第一批快速為ASIC和驗(yàn)證工程師開發(fā)并引進(jìn)PCIe 3.0和PCIe 4.0控制器的提供商之一后,PLDA很高興將通過硅驗(yàn)證的XpressRICH3和XpressRICH4 IP與PCIe EZ-VIP相結(jié)合,為ASIC項(xiàng)目團(tuán)隊(duì)提供一種可靠、可高度配置且易用的完整解決方案。”

“擁有易用且通過預(yù)先驗(yàn)證的PCIe驗(yàn)證IP對于我們的客戶來說非常重要。我們一直與Mentor合作,幫助客戶通過我們的Expresso 3.0核心驗(yàn)證其PCIe EZ-VIP,”Northwest Logic的董事長Brian Daellenbach說,“因此,客戶可以將Mentor PCIe VIP與我們通過硅驗(yàn)證的PCI Express核心結(jié)合使用,來創(chuàng)建并驗(yàn)證其具有高可信度的設(shè)計(jì)。”

Mentor的PCIe EZ-VIP包含適用于PCIe 1.0、2.0、3.0、4.0和mPCIe的串行和并行接口的預(yù)封裝且易用的驗(yàn)證環(huán)境,可用于驗(yàn)證PHY、Root Complex和Endpoint設(shè)計(jì)。測試計(jì)劃、符合性測試、測試序列和協(xié)議覆蓋范圍都作為SV和XML源代碼包含在內(nèi),從而允許簡單復(fù)用、擴(kuò)展和調(diào)試。Mentor VIP元件還包含一整套協(xié)議檢查、錯(cuò)誤注入和調(diào)試功能。

-

FPGA

+關(guān)注

關(guān)注

1620文章

21510瀏覽量

598874 -

asic

+關(guān)注

關(guān)注

34文章

1175瀏覽量

119981 -

Mentor

+關(guān)注

關(guān)注

5文章

109瀏覽量

113764

發(fā)布評論請先 登錄

相關(guān)推薦

DS320PR810的PCI Express合規(guī)性測試

LMK3H0102 PCI Express合規(guī)性報(bào)告

LMK6H和LMKDB1xxx PCI Express合規(guī)性報(bào)告

LMK6H PCI Express合規(guī)性報(bào)告

LMKDB1xxx PCI Express合規(guī)性報(bào)告

新思科技PCIe 7.0驗(yàn)證IP(VIP)的特性

DS50PCI401 2.5 Gbps/5.0 Gbps 4通道PCI Express中繼器數(shù)據(jù)表

DS50PCI402 2.5 Gbps/5.0 Gbps 4通道PCI Express中繼器數(shù)據(jù)表

XIO2001 PCI Express至PCI總線轉(zhuǎn)換橋接器數(shù)據(jù)表

Teledyne LeCroy擴(kuò)展CrossSync PHY技術(shù)到PCI Express 6.0

原型平臺是做什么的?proFPGA驗(yàn)證環(huán)境介紹

PCI EXPRESS卡機(jī)電規(guī)范

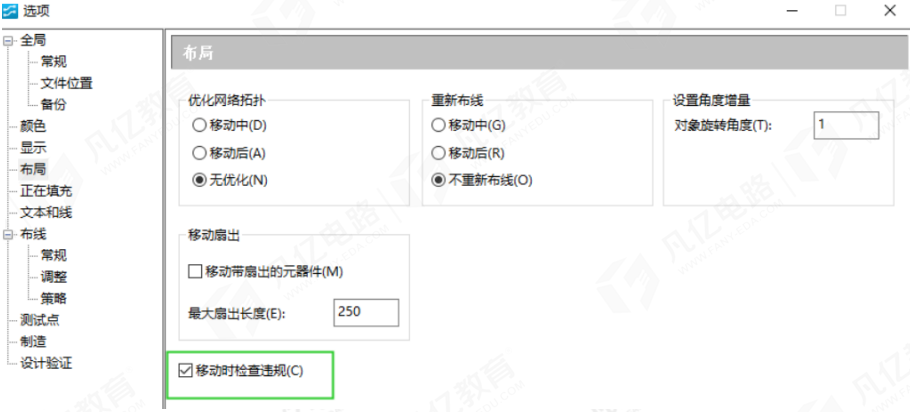

【原創(chuàng)分享】Mentor PADS Router元件布局設(shè)置及操作

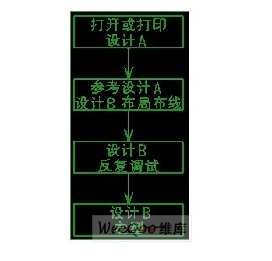

Mentor Graphics應(yīng)用之PCB設(shè)計(jì)復(fù)用

Mentor Graphics推出新的Mentor EZ-VIP PCI Express驗(yàn)證IP

Mentor Graphics推出新的Mentor EZ-VIP PCI Express驗(yàn)證IP

評論