全球蜂窩網絡上對數據的需求不斷增長,迫使運營商想方設法在2030年前將容量提升5000倍。要實現這一目標,需要將通道性能提升5倍、分配頻譜提高20倍、蜂窩基站數量增加50倍。

許多此類新型蜂窩將布置在室內,因為這里是大部分流量的來源,而光纖則是將流量回傳到網絡的首選。

但是,還有許多室外場所無法連接光纖或光纖連接成本過高,對于這種情況而言,無線回程是最可行的替代方案。

現可使用免執照的頻譜5 GHz,而且無需提供視線(LOS)路徑。但是其帶寬有限,而且由于大流量和寬帶天線,無疑會受到該頻譜其他用戶的干擾。

對于滿足容量需求所需的數以千計的室外蜂窩,60 GHz通信鏈路正在成為提供此類回程鏈路的有力競爭者。該頻譜也屬于免執照頻段,但與6 GHz以下的頻率不同,它包含高達9 GHz的可用帶寬。此外,高頻允許窄而集中的天線場型,可在一定程度上提高抗干擾性,但它需要LOS路徑。

基于FPGA和基于SoC的調制解調器越來越多地用于各種無線回程解決方案,這是因為使用這種調制解調器的平臺模塊化且可定制,從而能夠降低OEM的總成本。對于這些鏈接的無線電部分,收發器已集成在基于硅的IC中,并且封裝為低成本的表貼器件。

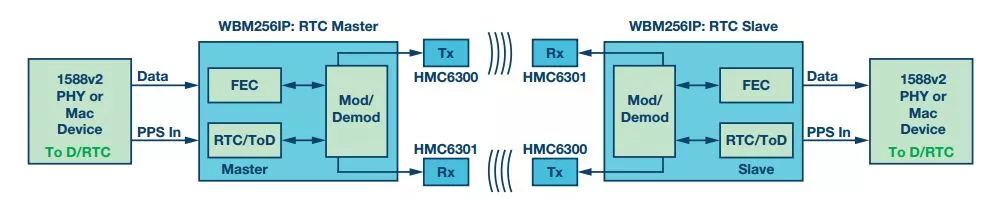

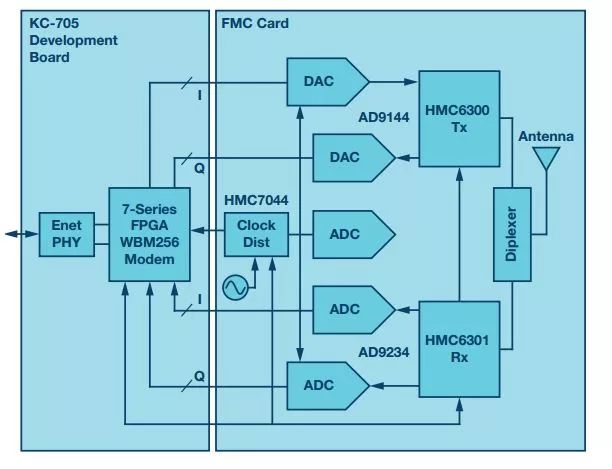

可使用商用器件構建完整的60 GHz雙向數據通信鏈路,如圖1中的解決方案所示。該設計由Xilinx和Hittite微波公司(現為ADI公司的下屬公司)研發,包括Xilinx調制解調器和ADI毫米波無線電。該鏈路滿足小型蜂窩回程市場的性能和靈活性要求。

圖1. 完整雙向數據通信鏈路的高級框圖

如圖1所示,創建鏈路需要兩個節點。每個節點都包含一個發送器(帶調制器)及其關聯的模擬發送器鏈、一個接收器(帶解調器)及其關聯的模擬接收器鏈。

調制解調卡與模擬和分立式器件集成。它包含以數字方式實施的振蕩器,能夠確保頻率合成的精度,并且所有數字功能均在FPGA或片上系統(SoC)上執行。這種單載波調制解調器內核可支持從QPSK到256 QAM的調制,通道帶寬高達500 MHz,能夠實現高達3.5 Gbps的數據速率。該調制解調器還可同時支持頻分雙工(FDD)和時分雙工(TDD)傳輸方式。穩健可靠的調制解調器設計方法能降低本振的相位噪聲影響。為改善性能和鏈路預算,內置 強大的低密度奇偶校驗(LDPC)編碼。

毫米波調制解調器

毫米波調制解調器可幫助基礎設施供應商為其無線回程網絡開發靈活且成本優化的可定制鏈路。它具有完全自適應、低功耗、小尺寸特性,可用于部署室內和全室外點對點鏈路以及點對多點微波鏈路。借助該解決方案,運營商能夠構建可擴展、現場可升級的系統。

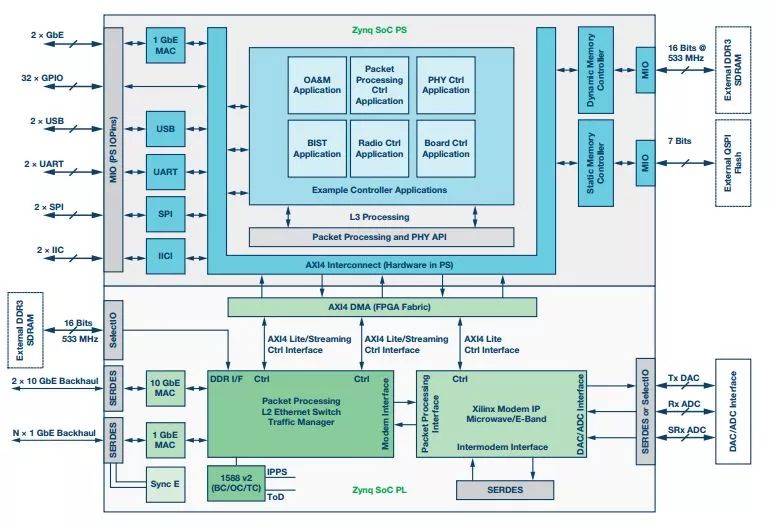

圖2詳細說明在基于SoC的解決方案中實施的數字調制解調器。平臺的可擴展處理系統(PS)位于可編程邏輯(PL)旁,包含雙ARM?Cortex?-A9內核,后者帶有集成式存儲器控制器和供外設使用的多標準I/O。

圖2. 用于無線調制解調器應用的所有可編程SoC

圖2. 用于無線調制解調器應用的所有可編程SoC

該SoC平臺用于執行各項數據和控制功能并實現硬件加速。圖2所示的是集成式毫米波調制解調器以及配套的PHY、控制器、系統接口和包處理器。但是,用戶可以根據所需的架構插入、更新或移除不同的模塊。例如,用戶可以選擇實施XPIC組合器,這樣可以將該調制解調器與另一個調制解調器以交叉極化模式配合使用。解決方案在PL中實施,使用SERDES和I/O作為各個數據路徑的接口,比如調制解調器與包處理器之間的接口、包處理器和存儲器之間的接口、調制解調器彼此之間的接口或DAC/ADC的接口。

該調制解調器IP的一些其他重要特性包括:通過自適應編碼和調制(ACM)功能保持鏈路連續工作的自動無損和無誤狀態切換、可改善RF功率放大器效率和線性的自適應數字閉環預校正(DPD)、能夠保持時鐘同步的同步以太網(SyncE)以及里德-所羅門或LDPC前向糾錯(FEC)。FEC根據電路要求選擇。LDPC FEC是無線回程應用的默認選擇,而對于去程等低延時應用而言,ReedSolomon FEC則更加適合。

LDPC實施方案經高度優化,并利用FPGA并行性幫助編碼器和解碼器完成計算。這可顯著改善SNR。您可通過改變LDPC內核的迭代數量來應用不同級別的并行性,進而優化解碼器的尺寸和功耗。此外,您還可根據通道帶寬和吞吐量約束條件為設計建模。

該調制解調器解決方案還配備用于顯示和調試的圖形用戶界面(GUI),并可提供通道帶寬選擇、調制方式選擇等高級功能以及硬件寄存器設置等低級功能。為讓圖1所示的解決方案實現3.5 Gbps的吞吐量,該調制解調器IP需要以440 MHz的時鐘速率運行。它將五個千兆位收發器(GT)用于連接接口,以支持ADC和DAC,并把另外一些GT用于10 GbE有效載荷或CPRI接口。

毫米波收發器芯片組

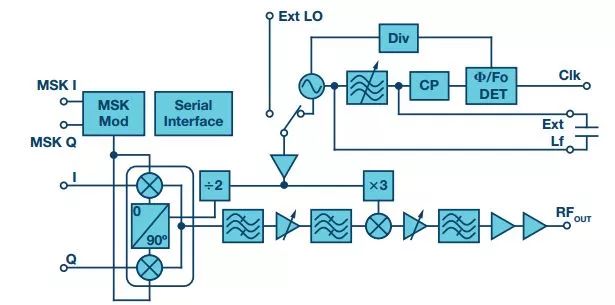

ADI針對小型蜂窩回程應用,優化了其在該設計中使用的第二代硅鍺(SiGe) 60 GHz芯片組。發送器芯片是一款完整的模擬基帶轉毫米波上變頻器。采用以250 MHz步進覆蓋57 GHz到66 GHz的改進型低相位噪聲頻率合成器,可支持至少64 QAM的調制。輸出功率已經提升到大約16 dBm線性功率,而集成式功率檢測器則可監測輸出功率,使其不超過法定限值。

該發送器芯片可提供對IF和RF增益的模擬或數字控制。在使用更高階調制的情況下,有時需要模擬增益控制,因為對幅度調制而言,離散增益改變可能會出錯,導致出現誤碼。內置SPI接口可為數字增益控制提供支持。

對于在窄通道中需要更高階調制的應用而言,可以向發送器中加入擁有更低相位噪聲的外部PLL/VCO,并使內部頻率合成器旁路。

圖3顯示了最高支持1.8 GHz帶寬的發送器芯片的框圖。MSK調制器選項可實現速率高達1.8 Gbps的低成本數據傳送,而無需使用高成本、高功耗的DAC。

圖3. HMC6300 60 GHz發送器IC框圖

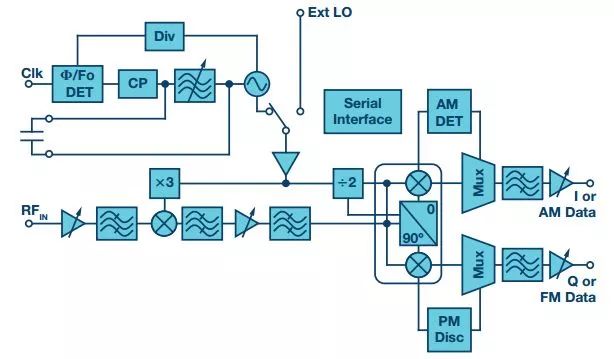

接收器芯片是該器件的輔助器件,同樣經過優化,能夠滿足小型蜂窩回程的嚴苛要求。該接收器的特點是能夠將輸入P1dB大幅提升到?20 dBm,并將IIP3提升到?9 dBm,從而處理短程鏈路,短程鏈路中碟形天線具有高增益,會在接收器輸入端產生高信號電平。

其他主要特性包括:噪聲系數在最大增益設置下低至6 dB;可調低通和高通基帶濾波器;合成器與發送器芯片中的新型合成器相同,能夠在57 GHz到66 GHz頻段支持64 QAM調制;對IF和RF增益的模擬或數字控制。

圖4顯示了接收器芯片的框圖。請注意,該接收器還包含一個AM檢測器,用以解調開關鍵控(OOK)等幅度調制。此外,還可使用FM鑒頻器解調簡單的FM或MSK調制。這就是用于為QPSK恢復正交基帶輸出和解調更復雜的QAM調制的IQ解調器之外的附加功能。

圖4. HMC6301 60 GHz接收器IC框圖

圖4. HMC6301 60 GHz接收器IC框圖

發送器和接收器均采用4 mm × 6 mm BGA型晶圓級封裝。借助這些表貼器件,可實現回程應用無線電板的低成本制造。

圖5所示的是示例毫米波調制解調器和無線電系統的框圖。除FPGA、調制解調器軟件和毫米波芯片組外,該設計還包含一些其他組件。其中包括雙通道12位1 GSPS ADC;最高2.8 GSPS的四通道16位TxDAC;以及超低抖動時鐘合成器(支持ADC和DAC IC上使用的JESD204B串行數據接口)。

圖5. 使用Xilinx和ADI IC的示例參考設計演示平臺

圖5. 使用Xilinx和ADI IC的示例參考設計演示平臺

圖6所示的平臺由Xilinx和ADI公司共同創建,用于演示目的。該實施方案包括Xilinx開發板上的FPGA調制解調器、工業標準FMC板(包含ADC、DAC和時鐘芯片),以及兩塊無線電模塊評估板。

圖6. 工作中的演示平臺

該演示平臺包括用于調制解調器控制和視覺顯示功能的筆記本電腦,以及用于復制典型毫米波鏈路路徑損耗的可變RF衰減器。開發板上的FPGA可執行WBM256調制解調器固件IP。開發板上的工業標準FMC夾層接插件可用于連接基帶板和毫米波無線電板。

毫米波模塊可卡合在基帶板上。模塊具備用于60 GHz接口的MMPX連接器以及用于可選用外部本振的SMA連接器。

該平臺包含在頻分雙工連接的每個方向對應的250 MHz通道中演示高達1.1 Gbps點對點回程連接所需的全部硬件和軟件。

模塊化和可定制

由于FPGA高度模塊化且可定制,因而能夠降低為無線回程應用構建平臺的成本。為小型蜂窩回程市場的毫米波調制解調器解決方案選擇商用器件時,請選擇高能效的FPGA/SoC和高性能的寬帶IP內核。高速也是為寬帶通信和開關功能選擇GT時應考慮的一個因素。此解決方案擴展能力出色,支持多種產品種類,包括以每秒數百兆位運行的低端小型蜂窩回程產品,以及同一硬件平臺上的3.5 Gpbs回程產品。

至于無線電部分,收發器IC封裝在表貼器件中,降低了制造成本。市場上的器件可滿足小型蜂窩部署無線回程需求的功耗、尺寸、靈活性和功能要求。您還可采購專為完善無線回程鏈路配備的高性能數據轉換器和時鐘管理IC。

原文轉自亞德諾半導體

-

ADI

+關注

關注

144文章

45812瀏覽量

248749 -

蜂窩

+關注

關注

0文章

121瀏覽量

25147 -

通信鏈路

+關注

關注

0文章

10瀏覽量

11159

原文標題:【世說設計】60 GHz回程鏈路,給你一個5000倍提升蜂窩容量的好方法

文章出處:【微信號:Excelpoint_CN,微信公眾號:Excelpoint_CN】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

OSI七層模型與數據通信的關系

華為發布數據通信未來技術趨勢報告

Ci24R1與Si24R1:2.4GHz數據通信芯片對比數據資料分析

華為成功舉辦數據通信創新峰會北非站,助力非洲網絡智能化發展

數據通信網關是什么?數據通信網關的功能作用

速銳得深入解析吉利幾何CAN總線數據通信網絡的拓撲層級框架技術

如何通過工業智能網關實現Modbus設備與PLC之間數據通信

STM32L451VET6串口波特率紊亂引起的數據通信問題求解

STM32F407與LTC4151-1之間通過GPIO模擬的IIC進行數據通信,LTC4151-1沒有回應答怎么解決?

數據通信系統的組成 數據通信系統的主要技術指標

工業智能網關如何保障數據通信安全

60 GHz雙向數據通信鏈路解決方案,助力蜂窩容量大提升

60 GHz雙向數據通信鏈路解決方案,助力蜂窩容量大提升

評論