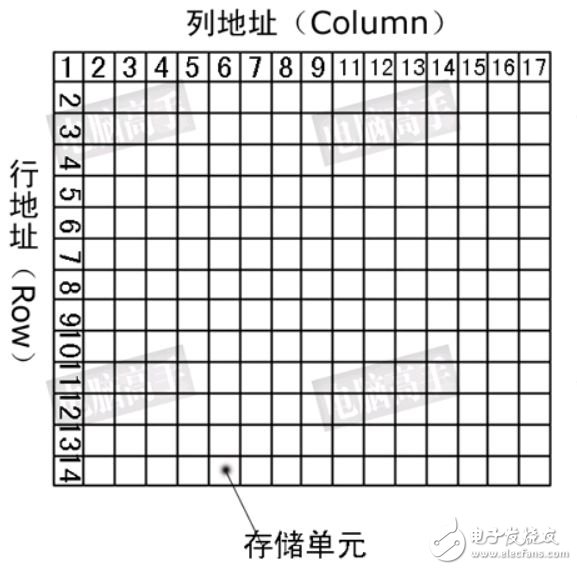

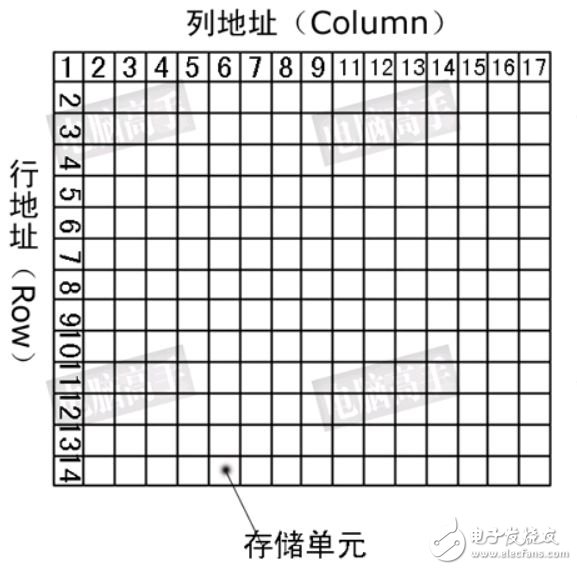

介紹SDRAM電路設(shè)計(jì)之前先了解下SDRAM的尋址原理。SDRAM內(nèi)部是一個(gè)存儲(chǔ)陣列,可以把它想象成一個(gè)表格,和表格的檢索原理一樣,先指定行,再指定列,就可以準(zhǔn)確找到所需要的存儲(chǔ)單元,這是內(nèi)存芯片尋址的基本原理,這個(gè)表格稱為邏輯Bank。由于技術(shù)、成本等原因,不可能只做一個(gè)全容量的Bank,而且由于SDRAM工作原理限制,單一的Bank會(huì)造成非常嚴(yán)重的尋址沖突,大幅降低內(nèi)存效率,所以在SDRAM內(nèi)部分割成多個(gè)Bank,目前的SDRAM基本都是4個(gè)Bank。存儲(chǔ)陣列示意如圖1所示:

圖1SDRAM存儲(chǔ)陣列示意圖

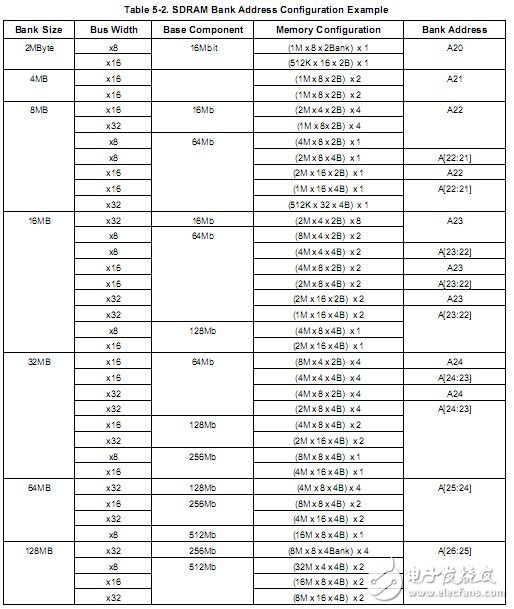

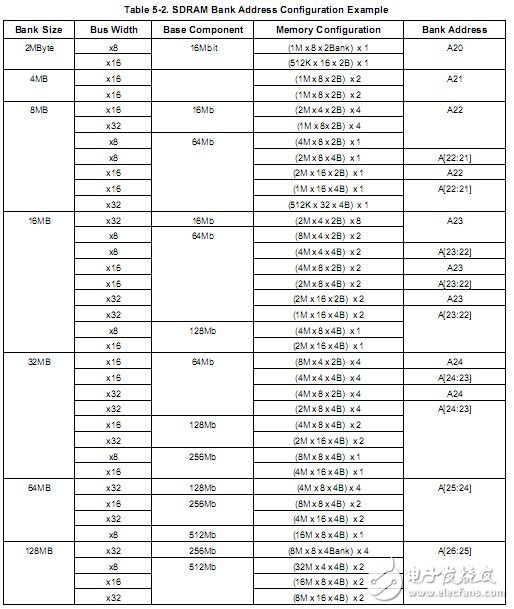

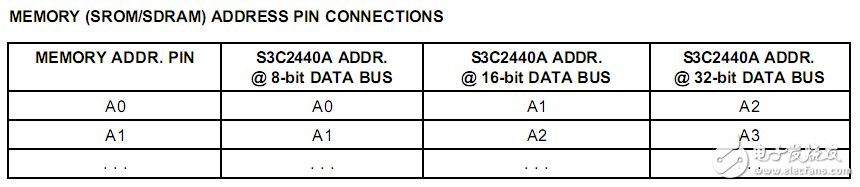

圖2SDRAM引腳配置方案

圖2是S3C2440A手冊(cè)提供的SDRAMbank地址的配置方案,維護(hù)系統(tǒng)使用的SDRAM是HY57V561620FTP-H,它的規(guī)格是4*4M*16bit(使用兩片是為了配置成32位的總線寬度),BANK大小是4M*16=64MB,總線寬度是32位,器件大小是4*BANK大小=256Mb,寄存器配置就是(4M*16*4B)*2,根據(jù)圖2可知,SDRAM上的BANK地址引腳(BA[1:0])與S3C2440的A[25:24]相連。

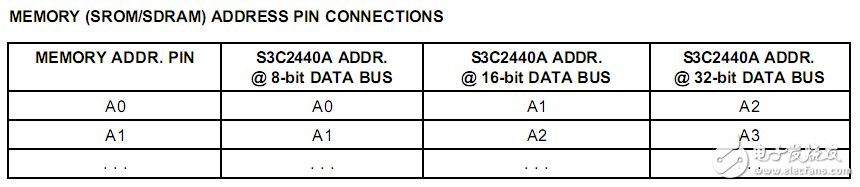

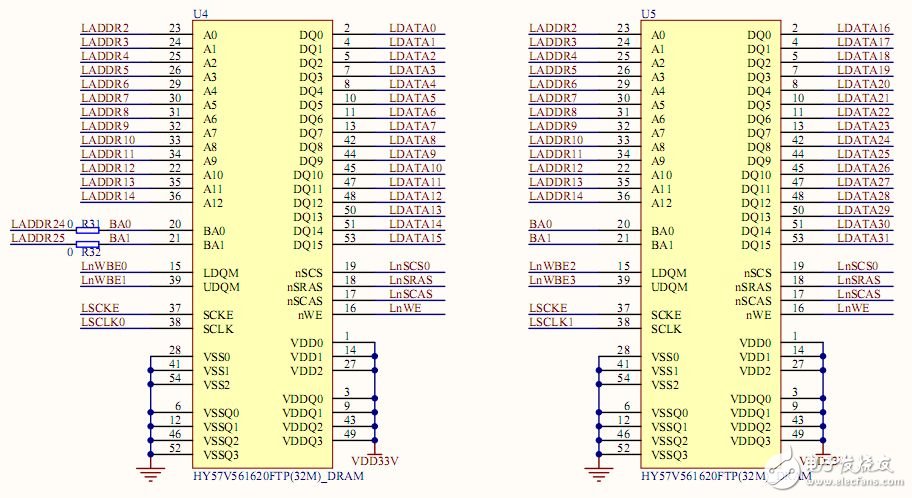

圖3 S3C2440A控制地址總線連接

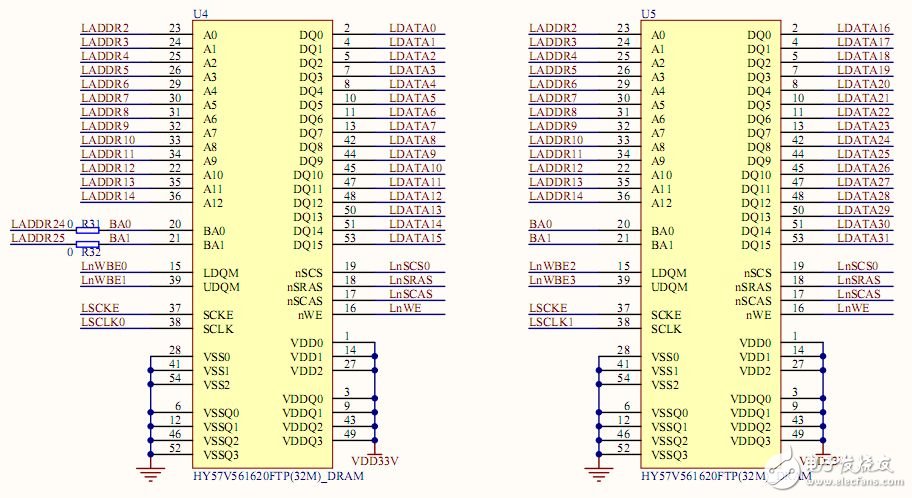

圖3是寄存器控制地址總線連接方式,我們使用2片SDRAM配置成32位的總線寬度,所以SDRAM上的A[12:0]接到S3C2440的A[14:2]引腳。具體的SDRAM電路連接如圖4所示:

圖4SDRAM電路連接圖

SDRAM的地址引腳是復(fù)用的,在讀寫SDRAM存儲(chǔ)單元時(shí),操作過(guò)程是將讀寫地址分兩次輸入到芯片中,每一次由同一組地址線送入,兩次送入到芯片上去的地址分別稱為行地址和列地址,它們被鎖存到芯片內(nèi)部的行地址鎖存器和列地址鎖存器。下面是該芯片的部分信號(hào)

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問(wèn)題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

相關(guān)推薦

介紹SDRAM電路設(shè)計(jì)之前先了解下SDRAM的尋址原理。SDRAM內(nèi)部是一個(gè)存儲(chǔ)陣列,可以把它想象成一個(gè)表格,和表格的檢索原理一樣,先指定行,再指定列,就可以準(zhǔn)確找到所需要的存儲(chǔ)單元。

發(fā)表于 01-26 09:49

?4896次閱讀

XILINX 關(guān)于FPGA 對(duì)DDR SDRAM 的設(shè)計(jì)文檔

發(fā)表于 08-17 09:20

我的設(shè)計(jì)中,ADC采集的數(shù)據(jù)(adc采集的速率20M)經(jīng)過(guò)fpga內(nèi)部構(gòu)建的ADCFIFO,SDRAM讀ADCFIFO的數(shù)據(jù)寫進(jìn)SDRAM中,數(shù)據(jù)再由SDRAM讀出送給FPGA內(nèi)部構(gòu)建

發(fā)表于 09-10 19:49

如何實(shí)現(xiàn)Reg istered SDRAM接口電路的設(shè)計(jì)?Reg istered SDRAM的工作原理是什么?Registered SDRAM接口電

發(fā)表于 04-12 07:10

關(guān)于STM32F429控制SDRAM(FMC—擴(kuò)展外部SDRAM )(1)原理介紹:》為什么是FMC 不是 FSMC ?區(qū)別在那里!STM32F429使用FMC外設(shè)來(lái)管理擴(kuò)展的存儲(chǔ)器,F(xiàn)MC是Flexible Memory Co

發(fā)表于 08-04 09:09

SDRAM設(shè)計(jì)詳細(xì)說(shuō)明

完成SDRAM的上層驅(qū)動(dòng)設(shè)計(jì),對(duì)SDRAM讀寫、管理無(wú)誤,與其他模塊的接口正確。

口令:MMCTEAM

SDRAM的工作原理

發(fā)表于 04-22 14:02

?0次下載

SDRAM幀存儲(chǔ)器部分電路

發(fā)表于 05-07 18:41

?21次下載

在高速數(shù)字視頻系統(tǒng)應(yīng)用中,使用大容量存儲(chǔ)器實(shí)現(xiàn)數(shù)據(jù)緩存是一個(gè)必不可少的環(huán)節(jié)。SDRAM就是經(jīng)常用到的一種存儲(chǔ)器。 但是,在主芯片與SDRAM之間產(chǎn)生的時(shí)序抖動(dòng)問(wèn)題阻礙了產(chǎn)品的大規(guī)模生產(chǎn)。在數(shù)

發(fā)表于 10-16 15:58

?2次下載

DRAM (動(dòng)態(tài)隨機(jī)訪問(wèn)存儲(chǔ)器)對(duì)設(shè)計(jì)人員特別具有吸引力,因?yàn)樗峁┝藦V泛的性能,用于各種計(jì)算機(jī)和嵌入式系統(tǒng)的存儲(chǔ)系統(tǒng)設(shè)計(jì)中。本文概括闡述了DRAM 的概念,及介紹了SDRAM、DDR SDRAM、DDR2 SDRAM、DDR

發(fā)表于 06-07 22:10

?9.3w次閱讀

所以SDRAM需要在電容的電量放完之前進(jìn)行刷新;隨機(jī)是指數(shù)據(jù)不是線性依次存儲(chǔ),而是自由指定地址進(jìn)行數(shù)據(jù)的讀寫。” 這只是對(duì)SDRAM的概念介紹,下面再簡(jiǎn)單的看一下SDRAM的內(nèi)部結(jié)構(gòu)。

![的頭像]() 發(fā)表于

發(fā)表于 03-29 09:30

?7903次閱讀

本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA讀寫SDRAM的實(shí)例和SDRAM的相關(guān)文章及一些SDRAM控制器設(shè)計(jì)論文主要包括了:FPGA讀寫SDRAM的實(shí)例,

發(fā)表于 12-25 08:00

?56次下載

MCU怎么在擴(kuò)展的SDRAM上運(yùn)行程序?

![的頭像]() 發(fā)表于

發(fā)表于 03-01 13:17

?2179次閱讀

本文檔的主要內(nèi)容詳細(xì)介紹的是數(shù)碼相框的SDRAM存儲(chǔ)電路電路圖免費(fèi)下載。

發(fā)表于 07-02 08:00

?4次下載

是直接焊接在電路板上,而且引腳較多、一旦遇上SDRAM存儲(chǔ)器工作故障,更換芯片比較麻煩,并且當(dāng)需要擴(kuò)充容量時(shí)修改電路也不方便。計(jì)算機(jī)上廣泛應(yīng)用的內(nèi)存條具有速度高、容量大、接口標(biāo)準(zhǔn)、擴(kuò)展方便等優(yōu)點(diǎn)。在大容量,高速數(shù)據(jù)存儲(chǔ)的領(lǐng)域,應(yīng)

發(fā)表于 10-30 16:30

?1069次閱讀

(網(wǎng)盤)關(guān)于SDRAM和錄音機(jī)等FPGA視頻(android嵌入式開發(fā)教程)-關(guān)于SDRAM和錄音機(jī)等FPGA視頻,一步一步的講解,真的很詳細(xì),適合大家自學(xué)研究。

發(fā)表于 08-04 12:21

?15次下載

關(guān)于SDRAM電路的設(shè)計(jì)

關(guān)于SDRAM電路的設(shè)計(jì)

評(píng)論