隨著通信和數據中心應用升級至更高的數據傳輸率以支持迅速增長的互聯網流量需求,SerDes 參考時鐘的性能正變得日益重要。如果參考時鐘抖動太高,會導致比特誤碼率 (BER) 過高、流量丟失或系統通信丟失。此外,56G PAM4 PHY、100G/200G/400G 以太網和 100G/400G OTN 需要多種頻率組合,進一步增加了時序的復雜性。

為此,Silicon Labs提供了全新有源時鐘振蕩器,其采用第四代 DSPLL 技術驅動,有效解決了 25/40/50/100/400Gbps 時序問題。本篇技術文章-“使用高性能有源時鐘振蕩器降低通信應用開發風險”將詳細分析高速通信和數據中心的時序要求,并介紹Silicon Labs經市場驗證的時鐘振蕩器解決方案,幫助工程人員克服日益艱鉅的高速網絡定時設計挑戰。

高速通信和數據中心的時序要求

Silicon Labs 的最新 Si54x Ultra Series 有源時鐘振蕩器產品專為這些要求高的高速通信和數據中心應用而打造。這些高性能有源時鐘振蕩器具有任意頻率合成和 80 fs RMS 超低抖動的特點,有標準尺寸和小封裝尺寸有源時鐘振蕩器供選擇。Ultra Series 具有領先的抖動容限和頻率靈活性,可為硬件設計者帶來設計自信,同時降低產品開發風險。

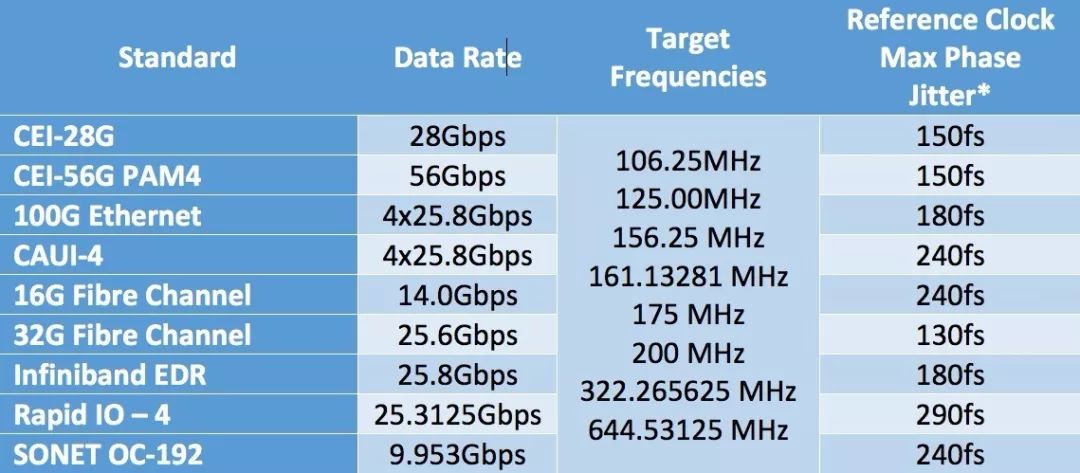

圖 1. 高速通信和數據中心的時序要求

*注意:直接根據參考時鐘或傳輸器眼閉規格計算,符合原始(未經 FEC)的 BER 要求,眼閉預算為 50/50 的確定性抖動/rms 抖動和 33%/67% 的時鐘/傳輸器。

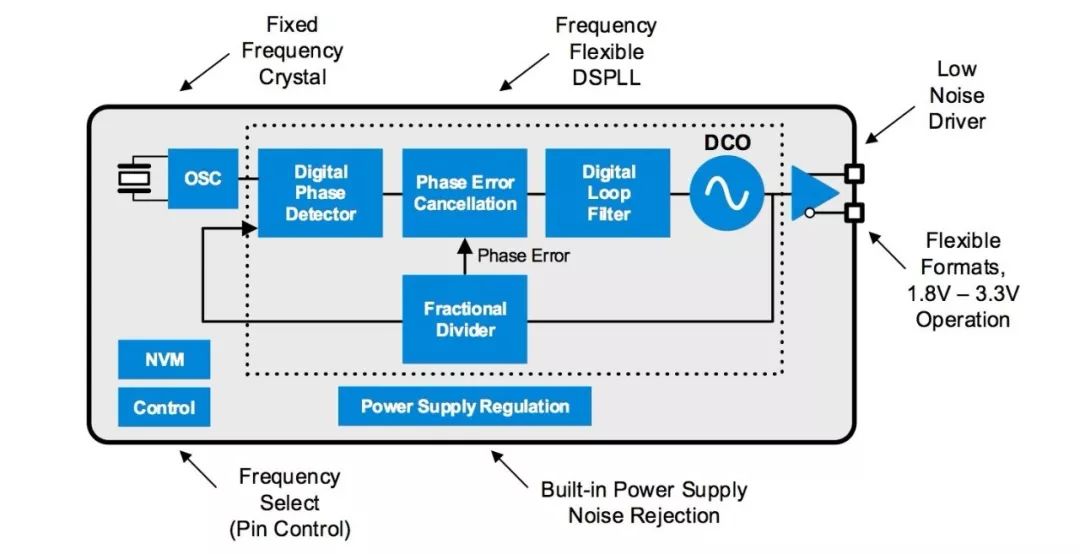

圖 2 Ultra Series DSPLL 體系結構

圖 2 為 Silicon Labs 全新 Ultra Series 第四代 DSPLL 的體系結構。不同于需要復雜批次制造過程、不同頻率使用不同晶體的傳統有源時鐘振蕩器技術,Si54x 體系結構結合了簡單的高質量固定頻率晶體和 Silicon Labs 最新一代的 DSPLL,可產生任意頻率。輸出測試期間,設備可設為自定義的目標頻率。采用這種創新方法,可輕松對 Si54x 進行批量自定義,以滿足不同客戶的不同需求。Si54x Ultra Series 支持 200 kHz 至 1.5 GHz 之間的任意頻率,僅通過一個產品系列便可輕松同時支持標準頻率和自定義頻率應用。

采用行業領先的 55 nm CMOS 技術設計,第四代 DSPLL 利用高度數字化的體系結構來實現最優的頻率靈活性和抖動性能。DSPLL 相位探測器的輸入會從模擬輸入轉換為數字輸入,使 DSPLL 完全在數字域內運行。這種全面數字化方法有諸多優點。首先,可用低于 1 ppb 的步長來精確控制數字控制有源時鐘振蕩器 (DCO),以追蹤參考時鐘與反饋時鐘之間的相位延遲。DCO 增益較小,因此電路出現噪聲的可能性較傳統模擬 PLL 更低。其次,DSPLL 支持創新型相位誤差消除電路,利用高級數字信號處理器來消除延遲、非線性和溫度影響導致的 PLL 噪聲。這些體系結構特點確保設備在不同過程、電壓和溫度下有一致的性能。因此,Silicon Labs 的第四代 DSPLL 體系結構在整個運行范圍都可實現超低抖動。

兼具頻率靈活性和超低抖動

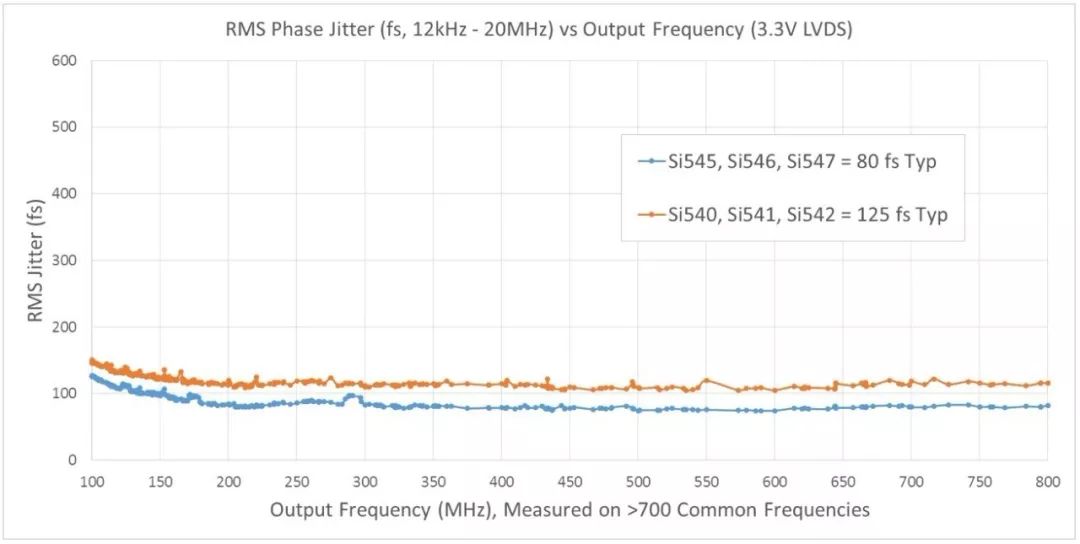

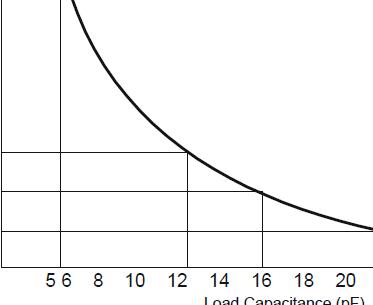

下圖為 Ultra Series 抖動性能與運行頻率和溫度對比圖。有兩個可用性能等級。Si545/6/7 設備的典型相位抖動性能為 80 fs RMS(12kHz - 20MHz),而 Si540/1/2 設備的典型相位抖動性能為 125 fs RMS (12kHz - 20MHz)。由于其抖動性能,Si54x 可將抖動容限最大化,為硬件客戶帶來設計自信。

圖 3 Si54x Ultra Series XO 抖動性能與頻率

為了進一步簡化設備評估,Silicon Labs 提供了 XO 相位噪聲查找實用工具,可用于檢索超過 1000 個常見頻率范圍下的 Silicon Labs 有源時鐘振蕩器相位噪聲圖。若想使用此免費實用工具,請訪問:

http://www.silabs.com/tools/pages/oscillator-phase-noise-lookup-tool.aspx。

集成電源噪聲控制

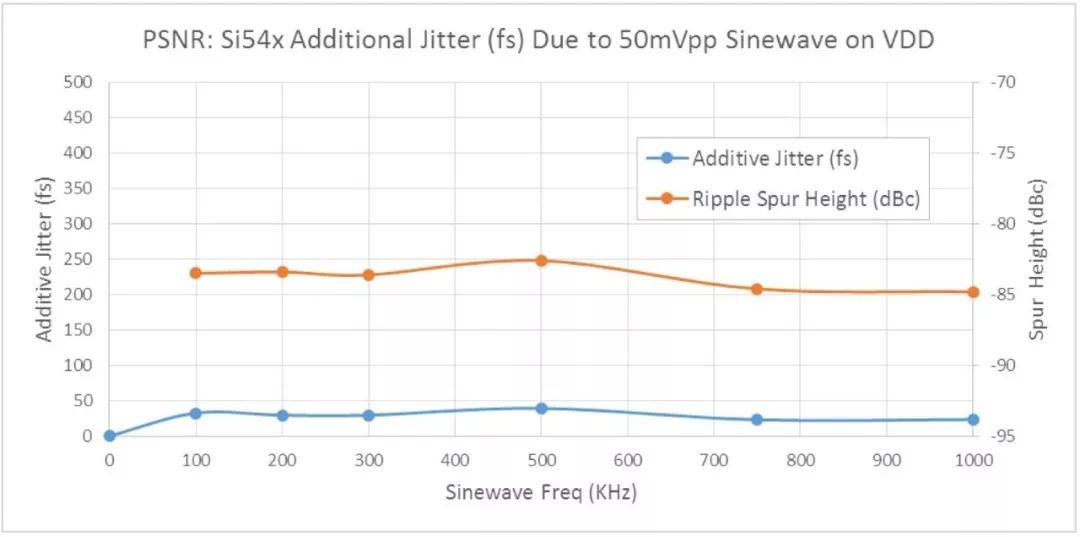

第四代 DSPLL 有廣泛的集成低壓差穩壓器網絡,具備電源噪聲抑制特性功能,確保即使在有噪聲的系統環境下也始終可實現低抖動運行。集成電源噪聲抑制的另一個優點是可簡化電源濾波、PCB設計和布局。

圖 4 最小化附加抖動的集成 PSNR

多頻支持

除標準單頻有源時鐘振蕩器外,也有使用 Silicon Labs 第四代 DSPLL 體系結構的雙頻或四頻有源時鐘振蕩器。這些設備可用一個 IC 替代兩個或更多離散有源時鐘振蕩器,將 BOM 成本和復雜性降至最低。多頻有源時鐘振蕩器有多個優點:

采用單個設備即可支持多協議SerDes

簡化設置/保持時間測試

頻率容限(例如:156.25 MHz + 50 ppm,156.25 MHz,156.25 MHz -50ppm)

簡化原型設計。使用一個多頻有源時鐘振蕩器用多種參考時鐘測試新的 SerDes 和 ASIC。選定最終頻率后,轉換為固定單一頻率有源時鐘振蕩器

單一電源

Silicon Labs 的 Ultra Series 有源時鐘振蕩器有一個高度靈活的輸出驅動器,可以在工廠自定義,以支持任何常用信號格式:LVDS、LVPECL、HCSL、CML、CMOS 和雙 CMOS。此外,輸出驅動器支持的電源電壓范圍較寬。一個 Si54x 設備即可支持 1.8V-3.3V 的運行電壓范圍,僅使用單一部件編號的有源時鐘振蕩器即可替代 1.8V、2.5V 和 3.3V 等固定電壓的多個有源時鐘振蕩器。

快速獲得樣品

Silicon Labs 提供基于網絡的實用工具,可在 1 分鐘內創建定制有源時鐘振蕩器。創建部件編號后,可通過 Silicon Labs 的授權分銷商或 Silicon Labs 網站下訂單。樣品通常在下單后 1-2 周內發貨。該過程可大大簡化有源時鐘振蕩器采購,是為原型和 NPI 試產快速獲取設備的完美選擇。

-

數據中心

+關注

關注

16文章

4700瀏覽量

71970 -

時序

+關注

關注

5文章

386瀏覽量

37288 -

時鐘振蕩器

+關注

關注

3文章

42瀏覽量

56289 -

高速通信

+關注

關注

0文章

23瀏覽量

10854

原文標題:【技術干貨】使用高性能有源時鐘振蕩器降低通信應用開發風險

文章出處:【微信號:SiliconLabs,微信公眾號:Silicon Labs】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

DVI接口詳細分析

時鐘產品系統解決方案及MEMS振蕩器問題答疑

數據中心布線方案:數據中心怎樣選擇光纖布線?

基于ispClock 5406D的高速串行接口時鐘解決方案

數據中心光互聯解決方案

詳細分析stm32f10x.h

AIoT之數據中心芯片的詳細分析

詳細分析高速通信和數據中心的時序要求以及時鐘振蕩器解決方案

詳細分析高速通信和數據中心的時序要求以及時鐘振蕩器解決方案

評論