介紹一種2.4 GHz的低噪聲亞采樣鎖相環。環路鎖定是利用亞采樣鑒相器對壓控振蕩器的輸出進行采樣。不同于傳統電荷泵鎖相環,由于在鎖定狀態下沒有分頻器的作用,由鑒相器和電荷泵所產生的帶內噪聲不會被放大N2 倍,從而會使鎖相環的帶內噪聲極大程度地減小。在輸出電壓擺幅相同的情況下,壓控振蕩器采用NMOSPMOS互補結構降低了鎖相環的功耗。鎖相環的設計在TSMC 180 nm CMOS工藝下完成,在1.8 V的供電電壓下,鎖相環功耗為7.2 mW。在偏移載波頻率200 kHz處,環路的帶內噪聲為-124 dBc/Hz。

引言

在無線通信系統中,一個低抖動、低噪聲的時鐘信號是必不可少的。鎖相環目前被廣泛應用于產生高精度的時鐘信號,例如為無線射頻收發機系統提供穩定的本振時鐘信號。低噪聲的本振信號對于無線收發機系統的整體性能起著至關重要的作用。

在傳統電荷泵鎖相環中,由于分頻器的作用,帶內噪聲性能會被很大程度惡化。通常情況下,會選取較小的環路帶寬來抑制由鑒頻鑒相器和電荷泵所帶來的帶內噪聲。然而,減小環路帶寬會增加鎖相環的鎖定時間以及芯片面積。

由于亞采樣鎖相環在鎖定狀態下沒有分頻器的作用[1],所以能很好地解決環路帶寬與噪聲之間的折中問題,既能獲得大的環路帶寬,又能減小鎖相環的相位噪聲。

本文分析了傳統電荷泵鎖相環的帶內噪聲,提出了低噪聲亞采樣鎖相環,給出了電路各模塊的具體實現和電路仿真結果。

1傳統電荷泵鎖相環的帶內噪聲

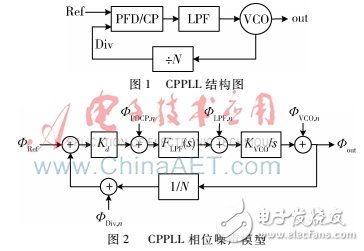

圖1為傳統電荷泵鎖相環(CPPLL)的基本結構[2],主要由鑒頻鑒相器(Phase and Frequency Detector, PFD)、電荷泵(CP)、環路濾波器(Low Pass Filter, LPF)和壓控振蕩器(VCO)組成。圖2所示為CPPLL的相位噪聲模型[3],Kd為PFD/CP線性增益,FLPF(s)為環路濾波器的傳輸函數,KVCO/s為VCO的增益。

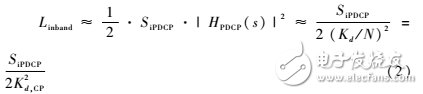

CPPLL帶內噪聲主要由PFD/CP的噪聲貢獻,利用圖2的相位域模型,可以得到閉環PD/CP的噪聲傳輸函數為:

HPDCP(s)=φout,nφPDCP,n=1Kd·G(s)1+G(s)/N(1)

其中,G(s)= Kd·FLPF·KVCO/s是PLL開環傳遞函數。所以由PFD/CP貢獻的帶內噪聲為:

其中,Kd=ICP/2π,相位噪聲Linband通常表示為單邊帶噪聲功率,SiPDCP是PFD/CP噪聲頻率譜密度。從式(2)可以看出,由于分頻器的存在,PLL的帶內噪聲會被放大N2倍。從而較大的Kd,CP即較大的 PFD/CP線性增益Kd及較小的分頻比N會得到更優的噪聲性能。

2SSPLL工作原理及噪聲分析

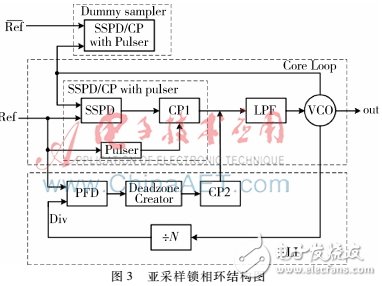

本文提出的亞采樣鎖相環基本結構框圖如圖3所示,主要由核心的亞采樣環路(Core Loop)及鎖頻環(FLL)構成。如果僅使用核心電路,由于SSPD的捕獲范圍有限,在采樣的過程中,采樣器無法區分被采樣的頻率是所需的N·fRef 還是fRef 的其他諧波,故加入FLL可以得到所需的鎖定頻率。SSPD采用參考信號Ref對VCO的輸出進行采樣。使用相同的SSPD/CP作為Dummy采樣器,可以消除從采樣開關到VCO的電荷注入和補償BFSK效應[4],從而使采樣PLL的參考雜散性能得到優化。

當環路未鎖定時,核心采樣電路與FLL一起工作,當Ref與FLL中分頻器輸出Div相位差小于π,PFD的輸出會掉入死區(Deadzone),使得CP2無法開啟,FLL停止工作,只有核心采樣電路單獨工作,直至鎖定。當環路鎖定時,Ref的上升沿與VCO差分輸出波形的交叉點對齊。SSPD采樣后,可以通過CP將采樣的電壓轉化為上下電流IUP和IDN。因為Ref采樣得到的電壓相等,所以CP的上下電流相等,從而VCO控制電壓VCTRL保持恒定不變,環路鎖定。

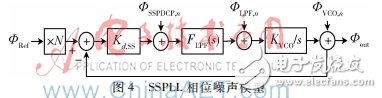

由于環路鎖定時,FLL不工作,所以SSPLL的噪聲模型可以簡化成如圖4所示的模型。與圖2比較,很明顯地看到少了分頻器模塊對系統的影響,使得鎖相環的帶內噪聲大幅度減小。從而SSPD/CP對整個環路貢獻的噪聲為:

但是,參考信號源的噪聲依然會被放大N2倍,所以在SSPLL中,帶內噪聲主要由參考信號源的噪聲貢獻。

3電路各模塊設計與實現

3.1壓控振蕩器

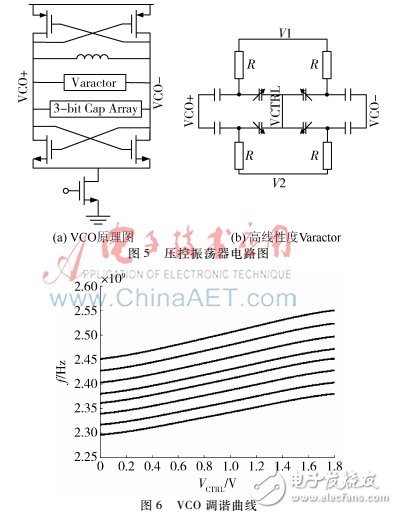

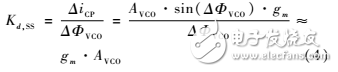

圖5為壓控振蕩電路圖,(a)為VCO的原理圖,本文設計采用NMOSPMOS互補的結構。相對于全NMOS、全PMOS結構,這種結構不僅可以節省功耗,而且當偏置電流相等時,互補型結構的VCO能夠獲得更好的相位噪聲[5]。此外,在偏置電流一定時,互補性結構提供更大的負阻值,交叉耦合管的轉換速度更快,使得1/f噪聲的拐角頻率大大降低。在1 mA的偏置電流下,相位噪聲可以達到-120 dBc/Hz @ 1 MHz。(b)為高線性度Varactor對于VCO的變容管Varactor采用對稱式結構,可以有效提高頻率調諧增益KVCO的線性度,從而優化噪聲性能。本文設計KVCO為55 MHz/V,調諧范圍為2.3 GHz~2.55 GHz,調諧曲線如圖6所示。

3.2亞采樣鑒相器/電荷泵

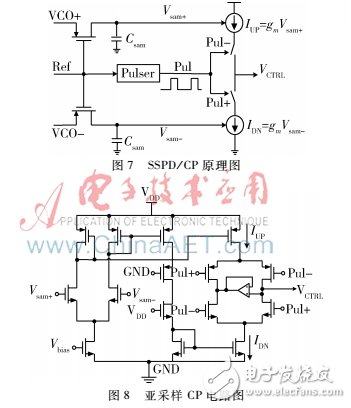

圖7所示為SSPD/CP的原理圖,圖8為本文提出的亞采樣CP的電路圖,在采樣過程中,鎖定時理想的采樣點為正弦信號的過零點,從而可以得到:

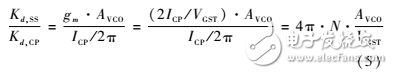

將亞采樣鎖相環CP與傳統電荷泵鎖相環CP的噪聲性能進行對比,可以得到:

通常情況下,N 1,AVCO/VGST》1,所以Kd,SS-Kd,CP。比較式(2)和式(3),可以得到亞采樣鎖相環的帶內噪聲被大幅度抑制。但是在環路帶寬一定的情況下,CP增益過大會導致環路濾波器的電容過大,使得芯片的面積增大。加入脈沖產生器Pulser電路,控制CP導通時間,有效控制CP增益的大小,減小芯片面積。

另外,在亞采樣CP中加入單位增益緩沖器,當輸出端充放電開關關閉時電流源管的漏端電壓和控制電壓相同,有效減小了由電荷分享而引起的電流紋波,提高了亞采樣鎖相環的雜散性能。

4電路仿真結果

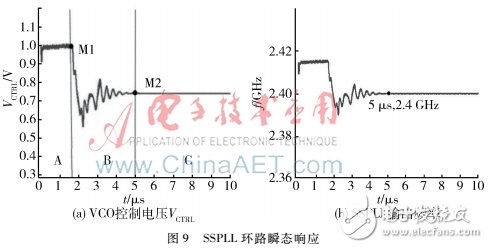

圖9是SSPLL環路瞬態響應,可以看出SSPLL的輸出頻率隨著VCO控制電壓的變化而變化。圖(a)中A區域表示系統檢測Ref與Div相位差小于π,但頻率在Ref的其他諧波處,未鎖定。此時,FLL不工作,CP2輸出為0,只有SSPD/CP有電流輸出,SSPLL輸出頻率大于所需鎖定頻率,Ref與Div相位差逐漸累積增大;B區域表示M1處,Ref與Div相位差積累至大于π,CP2開啟,環路濾波器放電使得VCTRL電壓降低,從而SSPLL輸出頻率降低,使其接近鎖定頻率N·fRef;在C區域中的M2處,環路開始鎖定,VCO控制電壓和SSPLL輸出頻率保持不變。

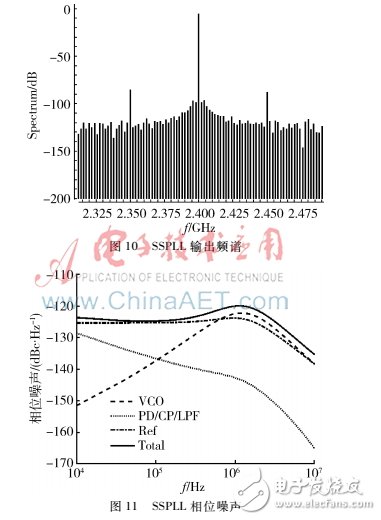

圖10和圖11所示分別為SSPLL的輸出頻譜(Spectrum)和相位噪聲性能。從圖中可以看出,SSPLL的參考雜散為-79.81 dBc,在偏移載波頻率200 kHz處,帶內噪聲為-124 dBc/Hz。SSPLL的版圖如圖12所示,核心電路面積為750 μm×560 μm。

5結論

本文介紹了亞采樣鎖相環電路的工作原理,重點對比分析了亞采樣鎖相環與傳統電荷泵鎖相環的噪聲性能。基于TSMC 180 nm的工藝,在1.8 V供電電壓下,SSPLL的功耗為7.2 mW;在偏移載波頻率200 kHz處,帶內噪聲為 -124 dBc/Hz;參考雜散為-79.81 dBc。

-

分頻器

+關注

關注

43文章

445瀏覽量

49586 -

無線射頻

+關注

關注

4文章

203瀏覽量

26933 -

低噪聲

+關注

關注

0文章

193瀏覽量

22748

發布評論請先 登錄

相關推薦

鎖相環LTC6946電子資料

LabVIEW鎖相環(PLL)

數字鎖相環(DPLL),數字鎖相環(DPLL)是什么?

鎖相環相位噪聲與環路帶寬的關系分析

詳解FPGA數字鎖相環平臺

基于單片集成鎖相環路芯片CX72300實現寬頻帶低噪聲頻率合成器的設計

關于2.4 GHz的低噪聲亞采樣鎖相環設計

關于2.4 GHz的低噪聲亞采樣鎖相環設計

評論