晶體管是現(xiàn)代電子電路中至關(guān)重要的半導(dǎo)體器件。它們可以執(zhí)行兩種主要功能。首先,作為其真空管前身三極管,晶體管可以放大電信號(hào)。其次,晶體管可以作為計(jì)算機(jī)的信息處理和存儲(chǔ)的開(kāi)關(guān)設(shè)備。場(chǎng)效應(yīng)晶體管是控制電流通過(guò)電場(chǎng)的半導(dǎo)體器件。

晶體管不僅可以放大電信號(hào),還可以作為開(kāi)關(guān)設(shè)備。計(jì)算機(jī)利用晶體管的開(kāi)關(guān)能力進(jìn)行算術(shù)和邏輯運(yùn)算以及信息存儲(chǔ)。它們使用二進(jìn)制代碼——以基數(shù)2書(shū)寫(xiě)的數(shù)字——來(lái)表示數(shù)字和功能。一系列的兩個(gè)狀態(tài)——0和1——表示數(shù)字。數(shù)字電路中的晶體管也以兩個(gè)狀態(tài)工作:“開(kāi)”和“關(guān)”——或?qū)ê筒粚?dǎo)通。“開(kāi)”對(duì)應(yīng)一個(gè)二進(jìn)制數(shù)字狀態(tài),而“關(guān)”對(duì)應(yīng)另一個(gè)。因此,包含適當(dāng)切換晶體管的電路元素集合可以表征一個(gè)數(shù)字。

由FET的p-n結(jié)擴(kuò)散過(guò)程形成的偶極層建立電場(chǎng)。這些電場(chǎng)控制輸出的電路導(dǎo)通路徑。這一機(jī)制是“場(chǎng)效應(yīng)”一詞的基礎(chǔ)。對(duì)這些器件的興趣主要源于其輸入電路具有單個(gè)反向偏置二極管的特性。FET需要極小的直流輸入電流,具有非常高的輸入阻抗。

場(chǎng)效應(yīng)晶體管的類型

場(chǎng)效應(yīng)晶體管主要有三種類型:結(jié)型場(chǎng)效應(yīng)晶體管(縮寫(xiě)為JFET,或簡(jiǎn)稱為FET)、金屬氧化物半導(dǎo)體場(chǎng)效應(yīng)晶體管(MOSFET)和金屬半導(dǎo)體場(chǎng)效應(yīng)晶體管(MESFET)。

金屬氧化物半導(dǎo)體的其他縮寫(xiě)有MOST(MOS晶體管)和IGFET(絕緣柵場(chǎng)效應(yīng)晶體管)。MESFET是一種現(xiàn)代發(fā)展,采用高速度特性為基礎(chǔ)半導(dǎo)體材料的砷化鎵(GaAs)。數(shù)字應(yīng)用中,MOSFET常用于集成電路,而JFET在模擬應(yīng)用中更為常見(jiàn)。

本文介紹了結(jié)型場(chǎng)效應(yīng)晶體管(JFET),并探討了這些設(shè)備運(yùn)行的原理。

結(jié)型場(chǎng)效應(yīng)晶體管

結(jié)型場(chǎng)效應(yīng)晶體管是一種三端器件,其中施加在一個(gè)端子的電壓控制著另兩個(gè)端子之間的電流——輸出電路電流。

JFET有兩種類型:n通道和p通道。由于電子的移動(dòng)速度快于孔,n通道JFET比p通道JFET更為常見(jiàn)。

在雙極結(jié)晶體管(BJT)中,導(dǎo)通水平依賴于兩種載流子——電子和孔。然而,JFET是一種單極器件,因?yàn)槠鋵?dǎo)通僅依賴于一種類型的載流子——電子(n通道)或孔(p通道)。

JFET的其他重要特性包括:

· 制造簡(jiǎn)單。

· 尺寸小,適合于LSI和VLSI數(shù)字陣列。

· 高輸入阻抗——通常為幾兆歐姆。

· 噪聲比BJT小。

· 在零漏電流下沒(méi)有偏置電壓。

n通道結(jié)型場(chǎng)效應(yīng)晶體管

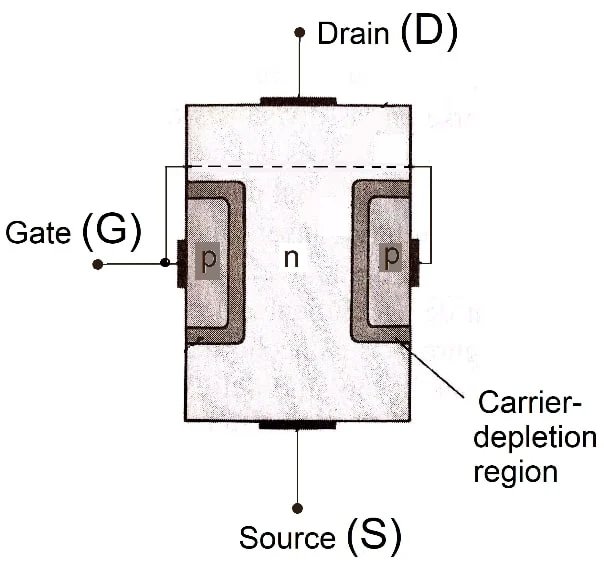

圖1展示了n通道JFET的示意圖。該圖所示的幾何形狀簡(jiǎn)化了對(duì)JFET原理的分析。

圖1

器件的兩側(cè)有重?fù)诫s的p型受體雜質(zhì)區(qū)域,形成柵極G。注意兩個(gè)p型區(qū)域與柵極端子的連接。

兩個(gè)柵區(qū)之間的區(qū)域是通道,構(gòu)成了n型材料的結(jié)構(gòu)。這個(gè)狹窄的半導(dǎo)體通道為源極和漏極之間提供了導(dǎo)通路徑。大多數(shù)載流子通過(guò)源極S進(jìn)入設(shè)備,并通過(guò)漏極D離開(kāi)。源側(cè)可以是通道的任一端。

該結(jié)構(gòu)的操作基礎(chǔ)是通過(guò)調(diào)整柵極G上的電壓來(lái)改變S和D端子之間的電阻。

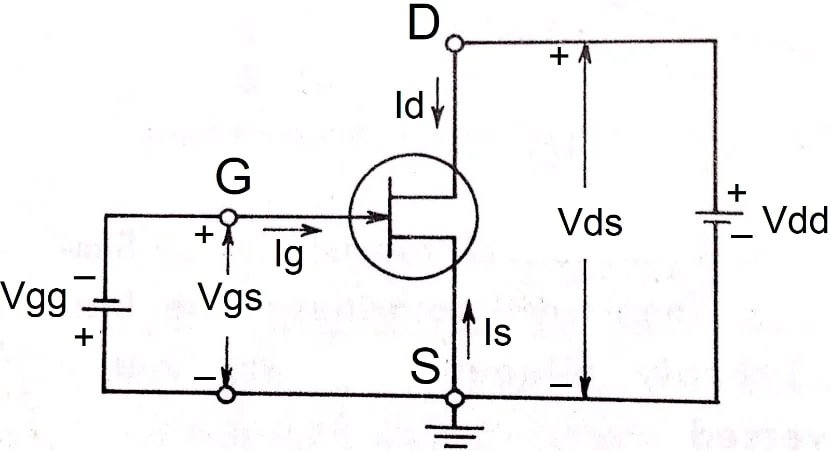

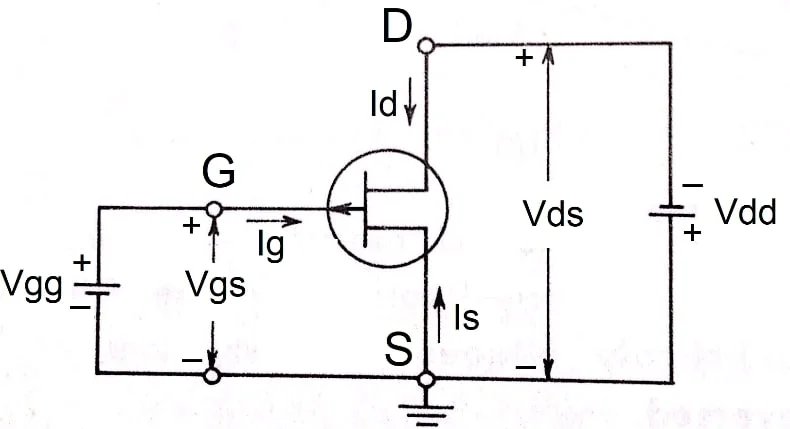

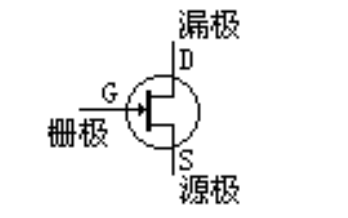

圖2顯示了n通道JFET的電路符號(hào)以及電流方向和電壓極性的約定。

圖2

柵極上的箭頭指示從p型到n型JFET的結(jié)的方向。

Is = 從S流入的常規(guī)電流。

Id = 從D流入的常規(guī)電流。

Ig = 從G流入的常規(guī)電流。柵電流的流向是柵結(jié)前向偏置。

Vds = 漏源施加電壓——如果d比s更正,則為正值。

Vdd = 漏極供電電壓(外部電壓源)。

Vgg = 柵極供電電壓(外部電壓源)。

Vgs = 柵源施加電壓——如果g比s更正,則為正值。Vgs用于反向偏置p-n結(jié)(Vgs = - Vgg)。

對(duì)于n通道JFET,Id和Vds為正,Is和Vgs為負(fù)。

n通道JFET的工作原理

在對(duì)JFET端子施加任何外部電壓之前,兩個(gè)p-n結(jié)處于無(wú)偏置狀態(tài),形成載流子耗盡區(qū)或空間電荷區(qū)。多余的載流子(電子)被移除或“耗盡”了載流子耗盡區(qū)。因此,載流子耗盡區(qū)幾乎沒(méi)有自由載流子,無(wú)法支持導(dǎo)通(如圖1所示)。

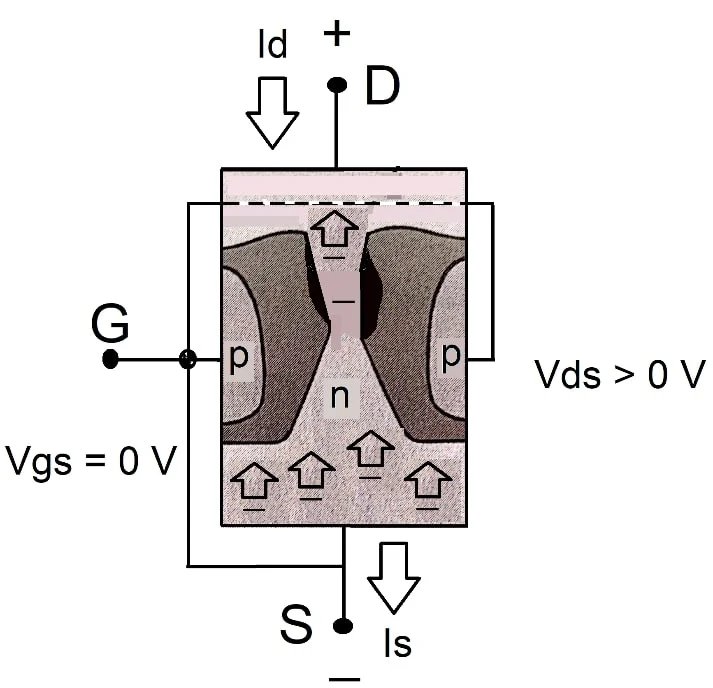

圖3顯示了Vgs = 0 V的條件——柵極與源極短路——并且Vds具有較低的正值。

圖3

圖3正的漏極端子吸引通道中的電子,產(chǎn)生電流Id。

根據(jù)約定,電流流動(dòng)方向與電子流動(dòng)方向相反,因此電流Id流入D。

電流Is的大小和方向與Id相同。Is的正方向被定義為流入S。因此,在這種情況下,Is是負(fù)值。電流Ig非常小,這是JFET的一個(gè)重要特性。

通道的阻抗限制了圖3中的電荷流動(dòng)的大小。

注意,載流子耗盡區(qū)在靠近D側(cè)時(shí)變得更寬。假設(shè)電阻均勻分布,通道中的電壓降將從S的0 V增加到D的Vds。然后,從S到D的p-n結(jié)將越來(lái)越多地反向偏置。隨著結(jié)上的反向偏置增加,靜止的未覆蓋電荷區(qū)域的厚度也增加。

未覆蓋電荷是載流子耗盡區(qū)中的束縛電荷——在p型側(cè)是負(fù)離子,在n型側(cè)是正離子。它們?cè)诮Y(jié)處形成一個(gè)偶極層。源自正離子并終止于負(fù)離子的電場(chǎng)線是結(jié)上電壓降的來(lái)源。術(shù)語(yǔ)“場(chǎng)效應(yīng)”描述了這一機(jī)制,因?yàn)殡娏骺刂剖怯捎谂c未覆蓋電荷區(qū)域相關(guān)的場(chǎng)的擴(kuò)展和反向偏置的增加。

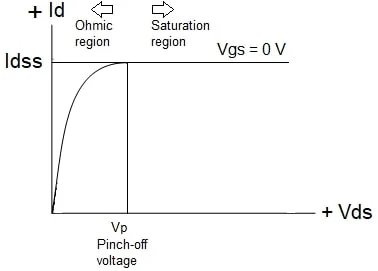

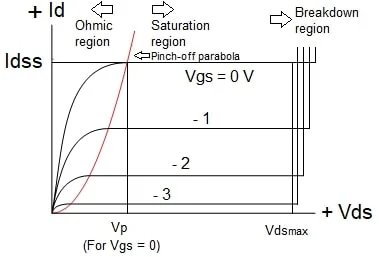

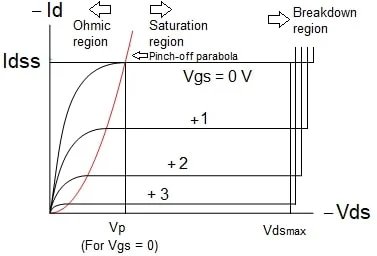

圖4顯示了n通道JFET的源漏特性,給出了Id與Vds的關(guān)系,且Vgs = 0。

圖4

圖4當(dāng)Id = 0時(shí),通道是開(kāi)放的。當(dāng)Vds的值增加到幾伏時(shí),電流按歐姆定律線性上升;這就是為什么圖形幾乎呈直線增長(zhǎng)——電阻是恒定的,n型JFET表現(xiàn)為簡(jiǎn)單的半導(dǎo)體電阻。

Vds的增量使耗盡區(qū)域變寬,通道的導(dǎo)電部分開(kāi)始縮小——逐漸降低通道的有效寬度并增加其電阻。

由于通道中的歐姆降,縮小并不是均勻的,而是在距離源極更遠(yuǎn)的地方更為明顯。

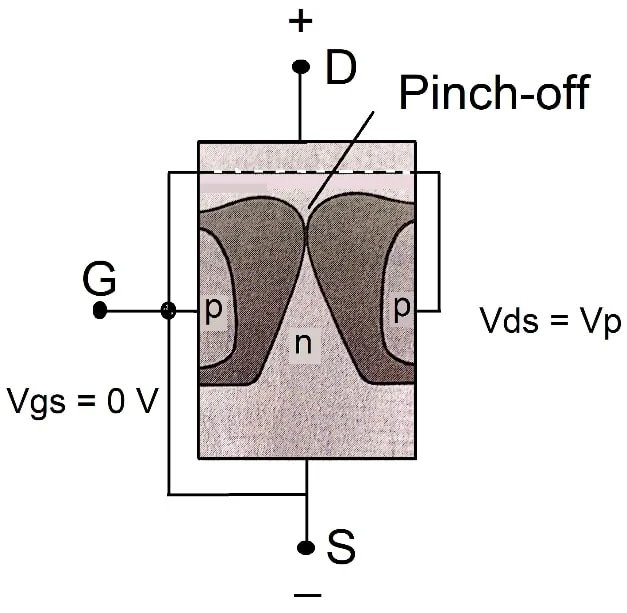

將Vds增加到看似兩個(gè)耗盡區(qū)會(huì)接觸的水平,如圖5所示,導(dǎo)致一種被稱為“擠壓”的狀態(tài)。在這種情況下,Vds = Vp——擠壓電壓。

圖5

圖5當(dāng)Vds達(dá)到Vp后,圖4中的曲線開(kāi)始平坦化。電流Id接近一個(gè)恒定值——飽和水平——表示為Idss(飽和短路漏電流)。曲線的水平區(qū)域中通道的電阻趨向于無(wú)窮大。在擠壓狀態(tài)下,存在一個(gè)小通道,電流密度很高。

在圖5中,通道正好處于漏端的擠壓閾值。將Vds增加到超過(guò)Vp會(huì)延長(zhǎng)沿通道的兩個(gè)耗盡區(qū)的接觸,但I(xiàn)dss保持不變。在這種情況下,JFET充當(dāng)電流源。

在擠壓值時(shí),通道不能完全關(guān)閉,使Id降至零——相反,Id保持在圖4所示的飽和水平。如果是那樣的話,提供p-n結(jié)反向偏置的歐姆降將會(huì)消失——失去導(dǎo)致擠壓的耗盡區(qū)域。

Vgs提供額外的反向偏置

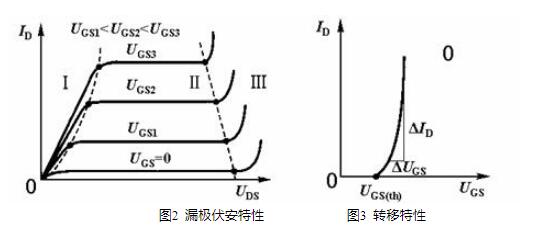

柵源電壓(Vgs)控制JFET。設(shè)置柵極端子在低于源極的潛在電平時(shí),會(huì)產(chǎn)生一系列Id與Vds的曲線,以Vgs為參數(shù)。圖6展示了n通道JFET的典型曲線。

施加?xùn)烹妷篤gs以提供額外的反向偏置,建立類似于Vgs = 0時(shí)的耗盡區(qū)域,但在較低的Vds值下,導(dǎo)致擠壓——和飽和水平——在更小的Vds值下發(fā)生。然后,Vgs幫助Vds產(chǎn)生擠壓。由于通道中Vds的降低,擠壓在較小的漏電流下發(fā)生。

對(duì)柵極施加一些正電壓——朝向前向偏置——使得產(chǎn)生擠壓所需的Vds值增加,同時(shí)導(dǎo)致擠壓出現(xiàn)的漏電流也相應(yīng)增加。為了避免在柵極端子上產(chǎn)生不必要的電流,不宜施加高正電壓。

如前所述,每個(gè)特性曲線在小的Vds值下都有一個(gè)歐姆區(qū)域——Id與Vds成正比——以及在大的Vds值下的恒定電流區(qū)域——在該區(qū)域內(nèi)Id對(duì)Vds的響應(yīng)很小。當(dāng)Vds超過(guò)擠壓水平時(shí),被擠壓的通道將電流限制在擠壓發(fā)生時(shí)的大小。

圖6還顯示,擠壓電壓呈拋物線下降,而在大Vds值下,飽和電流的大小隨著Vgs的負(fù)值增大而減少。

圖6

圖6當(dāng)Vgs = -Vp時(shí),產(chǎn)生的飽和水平對(duì)應(yīng)于最小的Id電流,我們可以得出結(jié)論,晶體管處于“關(guān)閉”狀態(tài)。

注意,當(dāng)Vds達(dá)到較高的幅度時(shí),曲線突然上升到看似無(wú)窮大的水平。這種上升標(biāo)志著p-n結(jié)的雪崩擊穿;在這種情況下,只有輸出電路元件限制了通過(guò)通道的電流。

施加在任何兩個(gè)JFET端子之間的最大電壓是導(dǎo)致p-n結(jié)雪崩擊穿的最低電壓。圖6表明,當(dāng)柵極反向偏置更強(qiáng)時(shí),雪崩在較低的Vds值下發(fā)生。這是因?yàn)榉聪蚱脰烹妷?Vgs)疊加在漏電壓(Vds)上,增加了p-n結(jié)上的實(shí)際電壓。

P通道結(jié)型場(chǎng)效應(yīng)晶體管

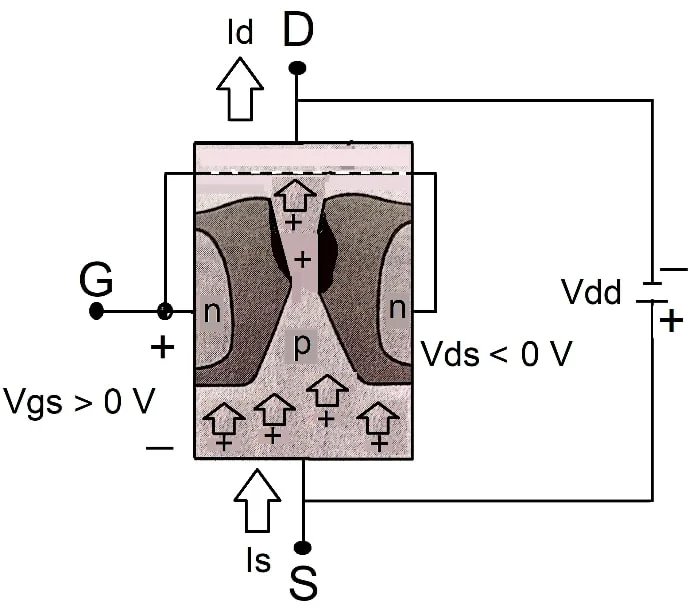

p通道JFET是n通道的反轉(zhuǎn),p型和n型材料的結(jié)構(gòu)如圖7所示。

圖7

圖7圖8顯示了p通道JFET的電路符號(hào)和極性約定。

p通道JFET的電流方向和電壓極性與n通道JFET相反;Id和Vds為負(fù),Is和Vgs為正。因此,從柵極到源極的正電壓增加會(huì)限制通道。

圖8

圖8圖8保留了圖2中用于n通道JFET的參考,適用于電流的Id、Is和Ig的方向,以及電壓Vds和Vgs的極性。柵極結(jié)的箭頭指向相反的方向(顯示從p型到n型的路徑)。

圖9顯示了p通道JFET的典型曲線。

圖9顯示Vgs為正值,Vds為負(fù)值——源極電位高于漏極。

圖9

圖9同樣,在Vds為高負(fù)值時(shí),曲線會(huì)突然上升到極端水平,暗示雪崩擊穿。

注意:

這兩種類型的晶體管——n通道和p通道——被稱為互補(bǔ)的。電路中的n通道JFET可以由類似額定值的p通道晶體管替換,反轉(zhuǎn)電源(Vdd)極性以及所有對(duì)極性敏感的器件,如電解電容器和二極管。

關(guān)于場(chǎng)效應(yīng)晶體管

JFET的三個(gè)電氣端子是漏極(D)、源極(S)和柵極(G)。

大多數(shù)載流子從源極通過(guò)通道流向漏極。通道可以是n型或p型晶體。柵源電壓控制電場(chǎng)——以及通道中的漏電流(Id)。柵接點(diǎn)通常在其上施加反向偏置電壓,導(dǎo)致柵極端子上幾乎沒(méi)有流動(dòng)電流。

考慮n通道設(shè)備,如果柵源電壓Vgs = 0 V而漏源電壓Vds為正,電子會(huì)由于電場(chǎng)在通道中漂移。漏電流Id與通道的電阻成正比,前提是Vds較小。

在p-n結(jié)處,載流子耗盡區(qū)域的寬度取決于電壓Vgs。Vgs的變化會(huì)改變通道的尺寸。載流子耗盡區(qū)域充當(dāng)閥門,以控制通道中的電流量,從而影響電流Id的大小。

正的漏電壓使p-n結(jié)反向偏置,主要在通道的漏端附近。當(dāng)Vds達(dá)到擠壓電壓(Vp)時(shí),通道的厚度在靠近漏端的地方幾乎減小到零。當(dāng)Vds = Vp時(shí),Id并不為零,因?yàn)樵跀D壓點(diǎn)和源端之間仍存在該電壓,產(chǎn)生的電場(chǎng)使載流子通過(guò)通道加速到漏端。

對(duì)于Vds > Vp的值,柵極與漏極之間的耗盡區(qū)域厚度增加,而擠壓點(diǎn)與源之間幾乎沒(méi)有變化。因此,額外的電壓出現(xiàn)在耗盡區(qū)域,通道沿線的電場(chǎng)變化很小。其結(jié)果是Id值保持恒定。

在Vds = Vp和Vgs = 0 V下測(cè)得的電流稱為飽和短路漏電流(Idss)。JFET通常在Vds > Vp和柵極施加反向偏置的情況下運(yùn)行。當(dāng)Vds + Vgs > Vp時(shí),Id幾乎獨(dú)立于Vds。

在高Vds值下,p-n結(jié)會(huì)產(chǎn)生雪崩擊穿。JFET的輸入阻抗非常高,但在發(fā)生雪崩擊穿時(shí)會(huì)急劇下降。

p通道JFET具有p型通道和n型柵極。它的工作方式類似于n通道晶體管,但電壓和電流極性相反。

浮思特科技深耕功率器件領(lǐng)域,為客戶提供IGBT、IPM模塊等功率器件以及單片機(jī)(MCU)、觸摸芯片,是一家擁有核心技術(shù)的電子元器件供應(yīng)商和解決方案商。

-

場(chǎng)效應(yīng)管

+關(guān)注

關(guān)注

46文章

1147瀏覽量

63829 -

晶體管

+關(guān)注

關(guān)注

77文章

9641瀏覽量

137876 -

FET

+關(guān)注

關(guān)注

3文章

630瀏覽量

62895 -

p通道

+關(guān)注

關(guān)注

0文章

2瀏覽量

5415

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

揭秘場(chǎng)效應(yīng)晶體管的使用訣竅,看完這里你就了然于胸

如何判斷場(chǎng)效應(yīng)晶體管方向,學(xué)會(huì)這幾步輕松搞定

選擇合適的場(chǎng)效應(yīng)晶體管,知道這六大訣竅就不用發(fā)愁了

MOS管與場(chǎng)效應(yīng)晶體管背后的聯(lián)系,看完后就全明白了

場(chǎng)效應(yīng)晶體管的分類及作用

場(chǎng)效應(yīng)晶體管的選用經(jīng)驗(yàn)分享

MOSFET和鰭式場(chǎng)效應(yīng)晶體管的不同器件配置及其演變

什么是鰭式場(chǎng)效應(yīng)晶體管?鰭式場(chǎng)效應(yīng)晶體管有哪些優(yōu)缺點(diǎn)?

場(chǎng)效應(yīng)晶體管的分類及使用

什么是場(chǎng)效應(yīng)晶體管

結(jié)型場(chǎng)效應(yīng)晶體管是什么?

場(chǎng)效應(yīng)晶體管開(kāi)關(guān)電路

功率場(chǎng)效應(yīng)晶體管的工作特性

如何進(jìn)行場(chǎng)效應(yīng)晶體管的分類和使用

N通道和P通道場(chǎng)效應(yīng)晶體管(FET)之間的區(qū)別是什么?

N通道和P通道場(chǎng)效應(yīng)晶體管(FET)之間的區(qū)別是什么?

評(píng)論