通過簡單地降低電壓或頻率來實現低功耗不可取——試問有誰會去買性能打過折的產品呢?那么,低功耗CPU到底又是怎么實現的?

隨著智能手機等移動應用的興起,目前的處理器設計不僅要提供高性能,還必須要符合另一個重要指標,那就是低功耗。通過簡單地降低電壓或頻率來實現低功耗不可取——試問有誰會去買性能打過折的產品呢?那么,低功耗CPU到底又是怎么實現的?EDN小編今天來和大家理一理,簡單來說,我們可以從微架構設計和制造工藝這兩個方面來看。

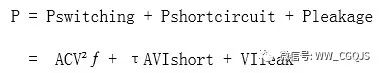

低功耗設計的基礎:處理器功耗分析的經典公式

要想實現低功耗,就必須了解電路中功耗的來源[1]。對于CMOS電路功耗主要分為三部分,分別是:電路在對負載電容充電放電引起的跳變功耗;由CMOS晶體管在跳變過程中,短暫的電源和地導通帶來的短路功耗;以及由漏電流引起的漏電功耗。其中跳變功耗和短路功耗為動態功耗,漏電功耗為靜態功耗。以下是SoC(即CPU)功耗分析的經典公式:

其中:?是系統的頻率;A是跳變因子,即整個電路的平均反轉比例;C是門電路的總電容;V是供電電壓;τ是電平信號從開始變化到穩定的時間。

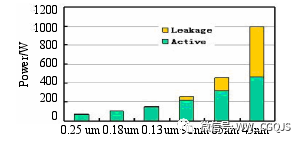

在深亞微米工藝下,電路的功耗主要是跳變功耗,短路功耗和漏電功耗可以忽略不計。但隨著工藝發展到納米級,漏電功耗在整個功耗中的比例將顯著提高(如下圖所示)。

圖:不同工藝下動態功耗和靜態功耗對比圖

低功耗的微架構設計

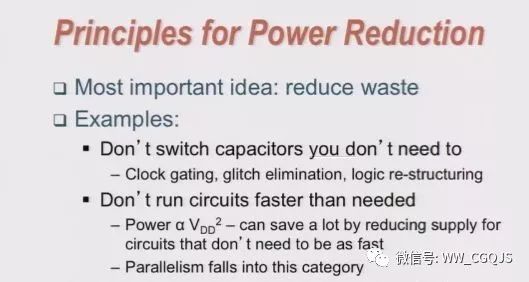

基于上面這個功耗分析的公式,我們要設法降低的主要就是其中的第一項和第三項功耗,即跳變功耗和漏電功耗。我們首先來看微架構設計,基本思路如下圖:

因此,我們可以衍生出很多的低功耗微架構設計方法。里面比較重要的一些如下:

?時鐘門控:給每個模塊的時鐘加上門控,不需要時將它關閉,從而盡可能降低功耗。

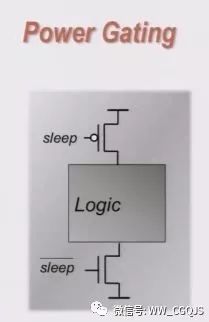

?電源門控:原理同上,盡可能降低動態功耗和漏電功耗。

?降低電壓:電壓受頻率影響,可以通過降低頻率來降低所需電壓。當頻率降低,電路開關速度降低,就能有更多時間去進行充電,因此所需充電電壓就能降低(電壓越大充電速度越快)。同時,可通過流水線分割組合邏輯。若同時保持頻率不變,電路能有更多時間去進行充電,從而降低所需充電電壓。

?系統設計時考慮優化,如減少電路開關,用RAM代替寄存器文件,減少存儲器讀寫。

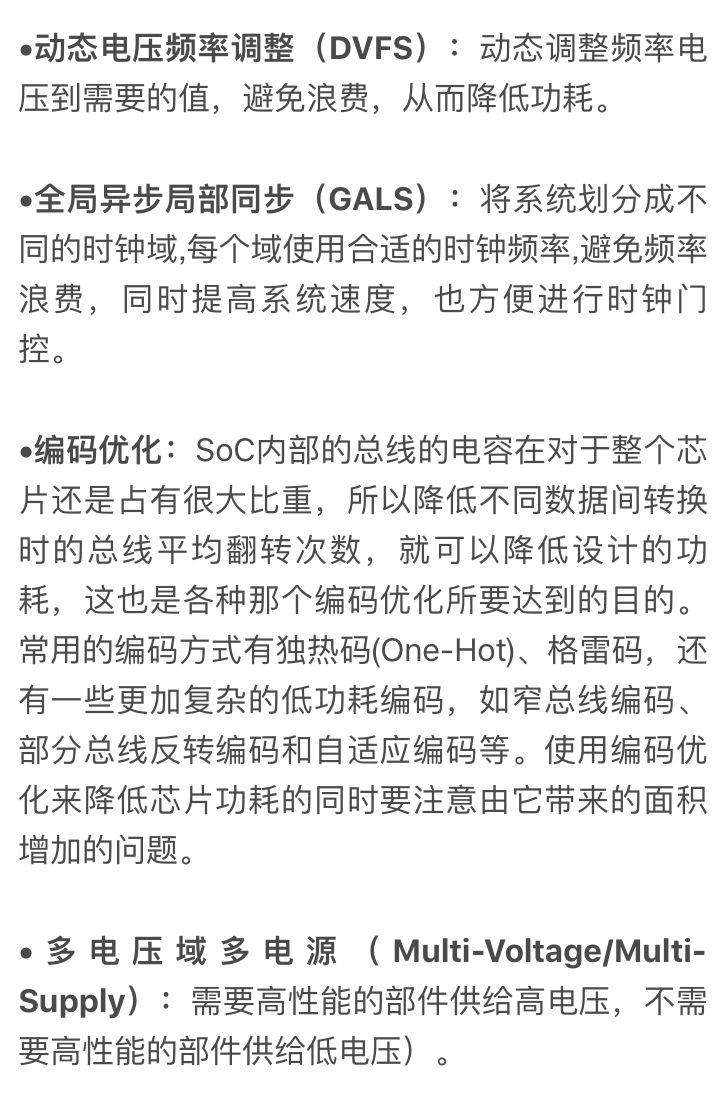

除了上述這些方法,高效的低功耗技術還有許多,比如襯底反偏(加反向電壓降低襯底漏電),多閾值單元(Multi-Vth cell)等等設計方法。下圖是一些比較熱門的RTL級低功耗技術。

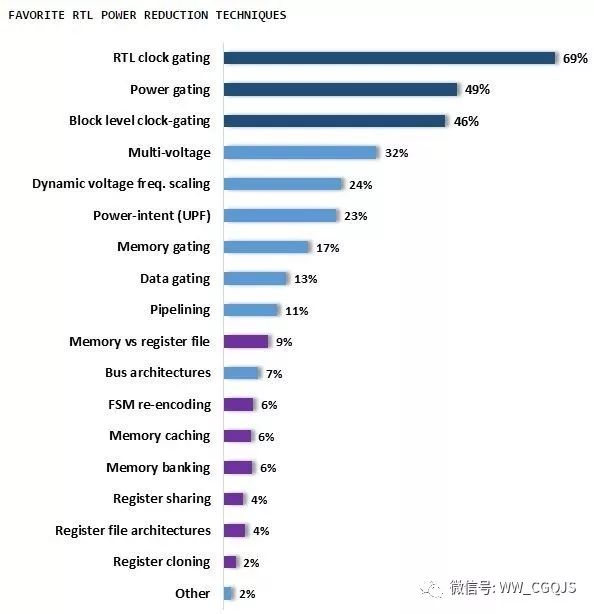

此外,對于CPU而言,PPA(性能、功耗和面積)也總是在互相權衡的。通過增加CPU內核數和采用ARM的big.LITTLE架構等,也是近年來常用的低功耗設計方法。

先進的低功耗制造工藝

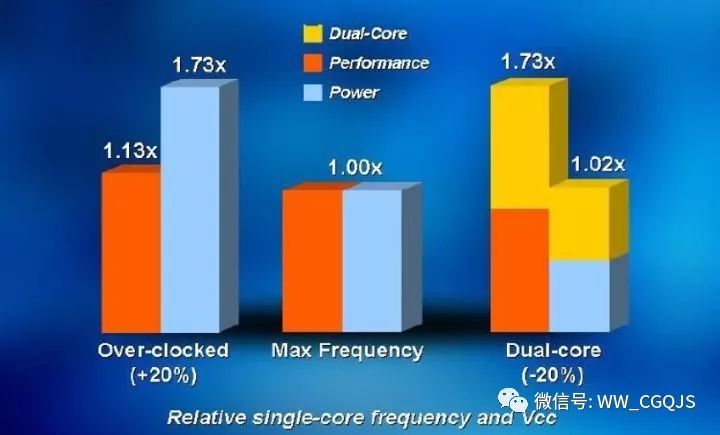

芯片的制造工藝在不斷向前發展。一個常識是,工藝越先進(納米數越低),功耗和性能都會提升。但是其原因又是為何?此外,FinFET工藝又是什么,為什么會更進一步實現二者的提升?這要從晶體管說起了:

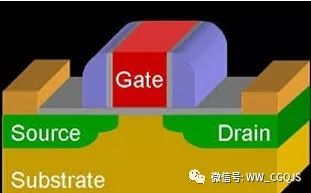

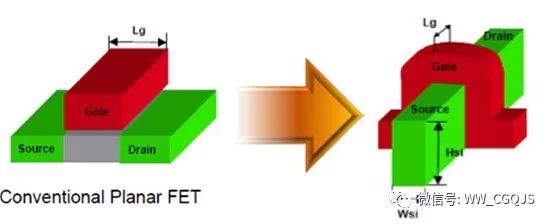

這里,我們盡量把事情說簡單。上面這副示意圖中就是一個典型的半導體晶體管。其中兩個綠色的部分(源極Source和漏極Drain)分別是晶體管的兩級,類似電池的兩級。紅色的部分就是用來控制這兩個電極的通斷的,而通斷分別對應數字化時間的1和0。所謂數字化世界其實也就是非常非常多的晶體管的通斷變化組合出來的。紅色柵極(Gate)的寬度就是我們通常所說的溝槽寬度或者線寬——我們通常說的多少多少nm就是指的這個寬度。

這個柵極的寬窄決定了性能和功耗。晶體管的開關速度(每次0/1變化)對應處理器的運算速度。紅色的柵極越寬,兩個綠色電極就越遠,導致它們直接連通一次的時間就越長。所以柵極越小,晶體管一次狀態變化所需的時間就越短,單位時間的工作次數就越多。這樣一堆晶體管單位時間可做的運算自然就更多,所以性能更好。

再來看功耗。柵極是通過加電壓幫助兩個綠色電極通電的。而柵極越寬,就需要更高的電壓才能導通兩極;柵極越窄,導通就更容易,所需的電壓也就越低。功耗的大小與電壓的平方成正比,所以導通電壓的下降是新工藝能夠降低功耗的主要因素。還有一個因素,即便是電壓相同,通過導體的面積和長度越小,電流也會越小。更小的柵極等于是縮小的導體,因此也會減少功耗。

那么,FinFET又是什么?

-

cpu

+關注

關注

68文章

10829瀏覽量

211194 -

制造工藝

+關注

關注

2文章

176瀏覽量

19734 -

低功耗

+關注

關注

10文章

2362瀏覽量

103607 -

COMS

+關注

關注

1文章

91瀏覽量

33062

原文標題:低功耗CPU是怎樣煉成的?

文章出處:【微信號:WW_CGQJS,微信公眾號:傳感器技術】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

低功耗藍牙上層架構淺析

汽車電子電氣架構設計及優化措施

基于超低功耗架構設計的智能手表平臺W307

介紹STM32低功耗睡眠模式事件喚醒的實現

微捷碼32/28納米低功耗工藝層次化參考流程

使用Simulink實現軟件架構設計

從微架構設計和制造工藝低功耗CPU的實現

從微架構設計和制造工藝低功耗CPU的實現

評論