文章來源:半導體與物理

原文作者:jjfly686

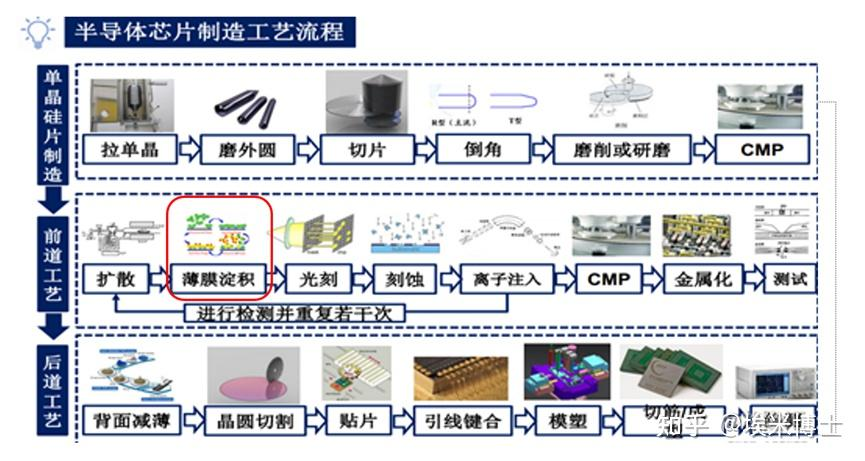

半導體薄膜沉積工藝是現代微電子技術的重要組成部分。這些薄膜可以是金屬、絕緣體或半導體材料,它們在芯片的各個層次中發揮著不同的作用,如導電、絕緣、保護等。薄膜的質量直接影響到芯片的性能、可靠性和成本。

薄膜工藝基本介紹

半導體薄膜沉積工藝是現代微電子技術的重要組成部分,通過在半導體襯底上沉積一層或多層薄薄的材料來構建復雜的集成電路。這些薄膜可以是金屬、絕緣體或半導體材料,它們在芯片的各個層次中發揮著不同的作用,如導電、絕緣、保護等。薄膜的質量直接影響到芯片的性能、可靠性和成本。因此,薄膜沉積技術的發展對半導體行業具有重要意義。

薄膜工藝的分類

目前,主流的薄膜沉積設備和技術包括物理氣相沉積(PVD)、化學氣相沉積(CVD)和原子層沉積(ALD)。這三種技術在沉積原理、沉積材料、適用膜層及工藝等方面存在明顯差異。

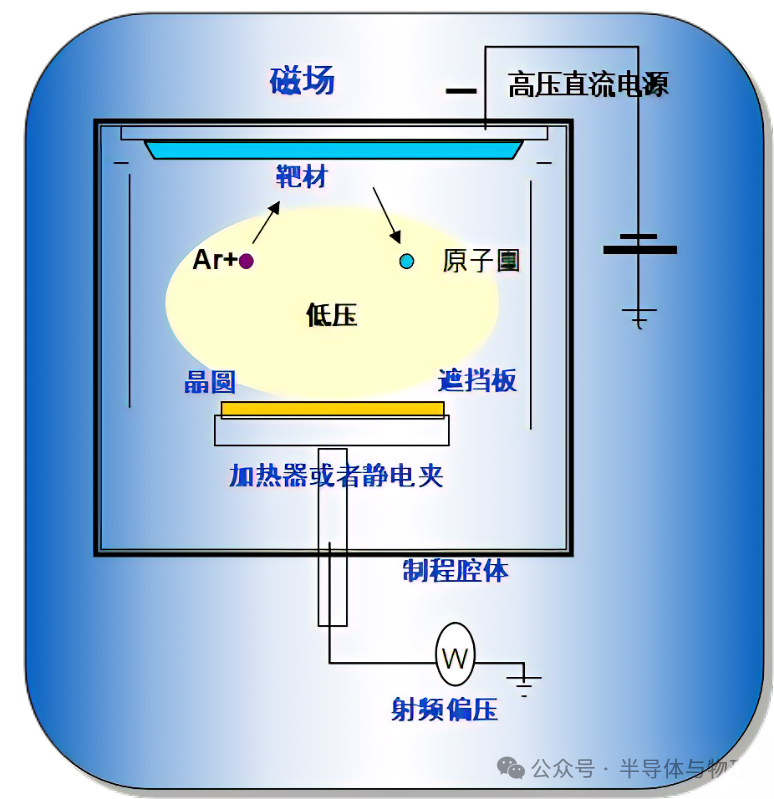

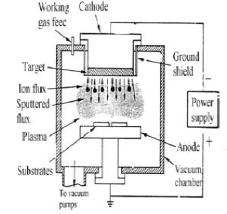

物理氣相沉積(PVD)PVD是一種完全基于物理過程的薄膜沉積技術,通過蒸發或濺射等方式使材料氣化,然后在基板上冷凝形成薄膜。

真空蒸鍍:在高真空條件下加熱待鍍材料至氣化,并在基板上沉積薄膜。

濺射鍍膜:通過氣體放電產生的氣體離子高速轟擊靶材表面,使靶材原子被擊出并在基板表面成膜。

離子鍍:結合真空蒸鍍和濺射鍍膜的優點,待鍍材料氣化后在放電空間部分電離,隨后被電極吸引至基板沉積成膜。

特點:PVD過程中僅材料形態發生改變,不涉及化學反應,屬于純粹的物理變化。

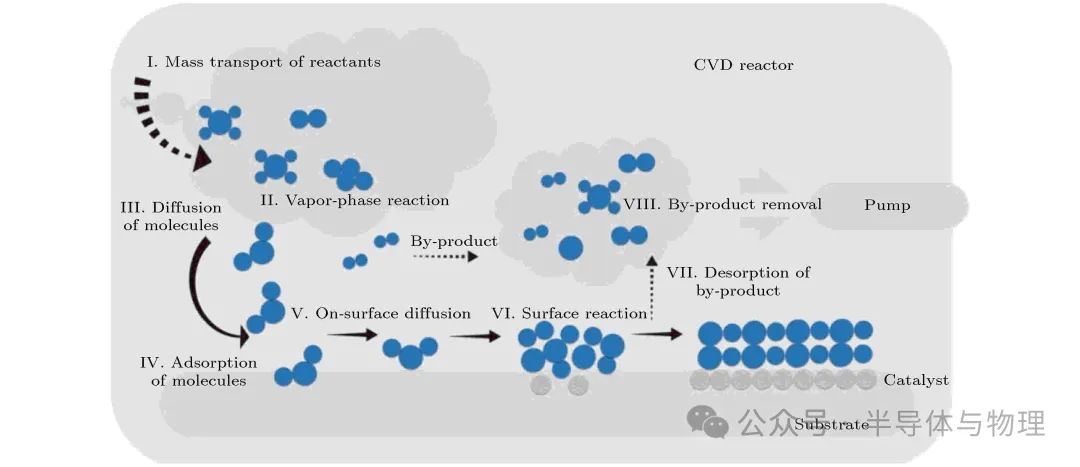

化學氣相沉積(CVD)CVD是一種涉及氣相化學反應的薄膜沉積技術,通過將氣體前驅體引入反應腔中,在基板表面發生化學反應形成固態薄膜。

普通CVD:適用于多種介質膜層和半導體膜層的沉積。

等離子體增強CVD(PECVD):利用等離子體增強反應活性,適用于低溫沉積。

高密度等離子體CVD(HDPCVD):能同時進行沉積和刻蝕,具備優秀的高深寬比間隙填充能力。

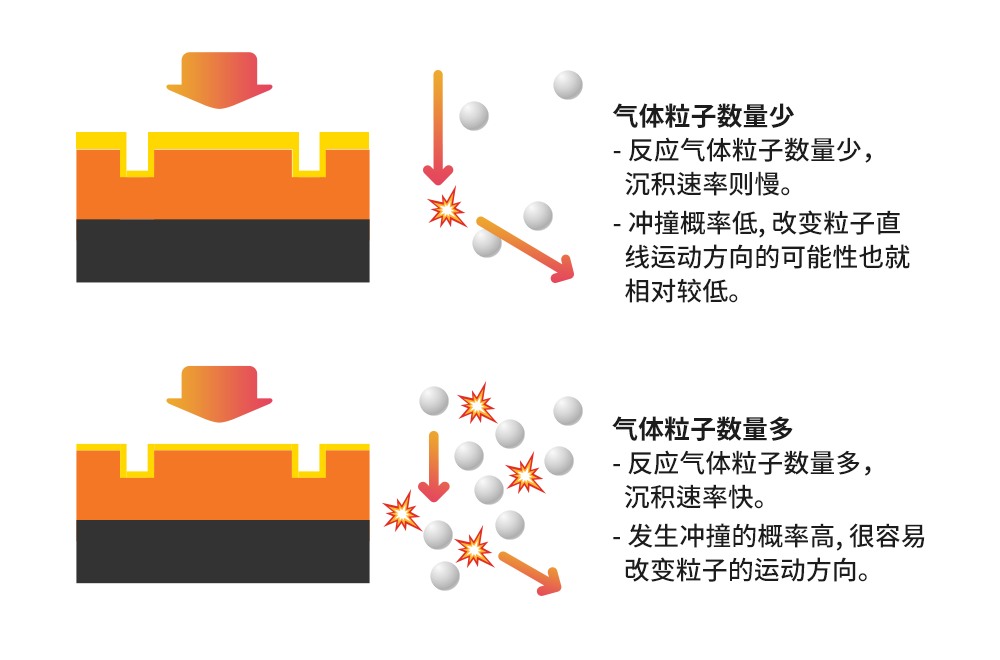

次常壓CVD(SACVD):在高壓環境下通過臭氧在高溫下形成的高活性氧自由基增加分子間的碰撞,實現優秀的填孔能力。

金屬有機化學氣相沉積(MOCVD):適用于制備半導體材料,如GaN。

特點:CVD反應前體一般為硅烷、磷烷、硼烷、氨氣、氧氣等氣體原料,生成物一般為氮化物、氧化物、氮氧化物、碳化物、多晶硅等固體薄膜,反應條件一般為高溫、高壓、等離子體等。

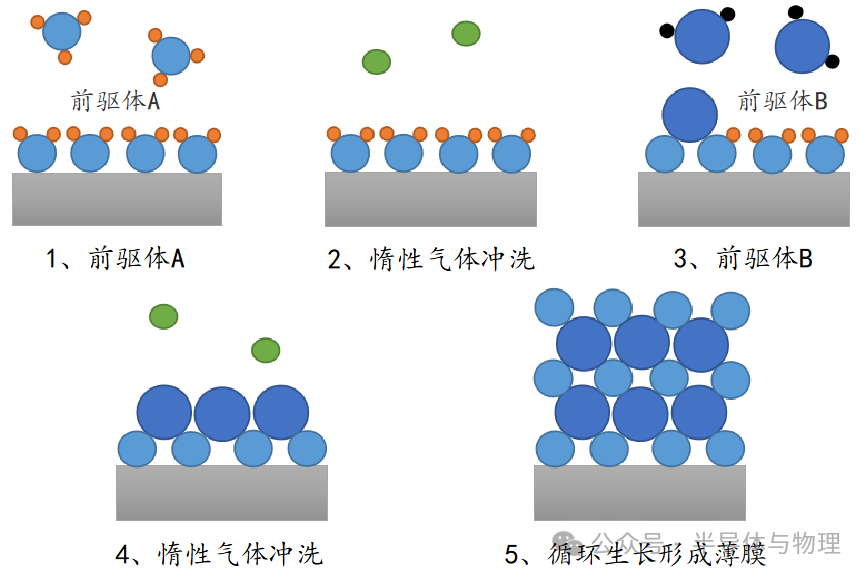

原子層沉積(ALD)ALD是一種特殊的CVD技術,通過脈沖方式交替引入兩種或多種反應前驅體,實現單原子層級別的精確沉積。

熱原子層沉積(TALD):利用熱能使前驅體吸附在基體表面并發生后續化學反應。

等離子體增強原子層沉積(PEALD):利用等離子體增強反應活性,可在較低溫度下實現較快的薄膜沉積速度。

特點:ALD具備精準的膜厚控制能力,沉積薄膜的厚度均勻性和一致性極為優秀,且其臺階覆蓋能力非常強大,適合深槽結構中的薄膜生長。

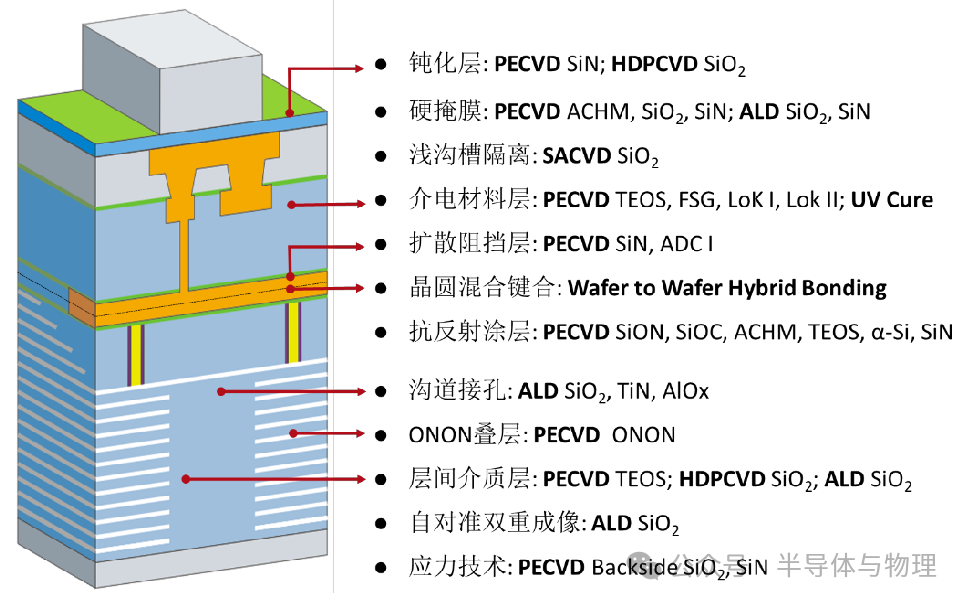

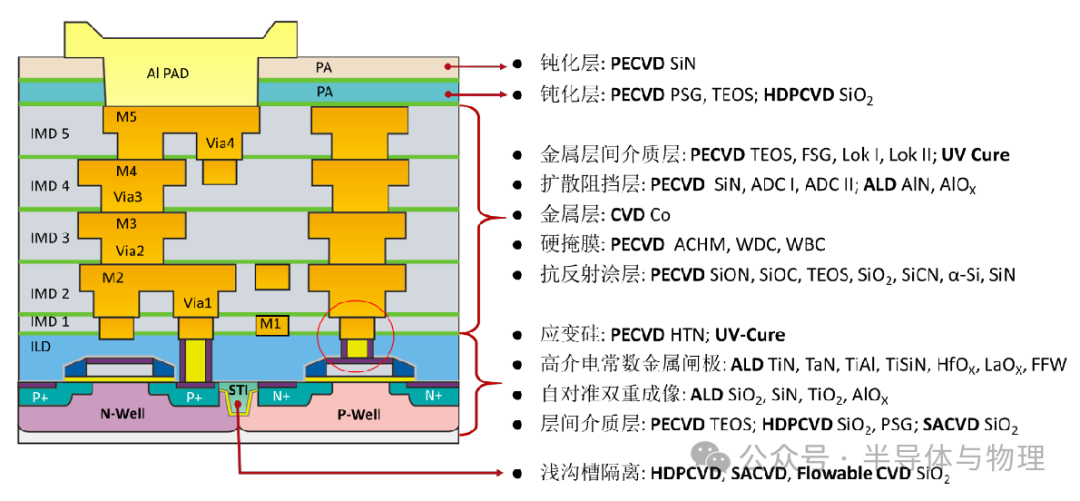

薄膜各個工藝在芯片里的應用

金屬層PVD主要用于沉積超純金屬、過渡金屬氮化物薄膜,如鋁墊、金屬硬掩膜、銅阻擋層和銅籽晶層等。

Al pad:與PCB鍵合的焊盤。

金屬硬掩膜:常用TiN,用于光刻工藝中。

Cu阻擋層:常用TaN,功能為防止Cu擴散。

Cu籽晶層:常用純Cu或Cu合金,作為后續電鍍工藝的種子層。

介質層CVD主要用于沉積各種絕緣材料,如氮化物、氧化物、氮氧化物、碳化物和多晶硅等,用于隔離不同的電路組件,減少干擾。

柵氧化層:用于隔離柵極和溝道。

層間介質:用于隔離不同層次的金屬線。

阻擋層PVD用于防止金屬擴散,保護器件免受污染。

Cu阻擋層:防止銅擴散到其他層中,影響器件性能。

硬掩膜PVD用于光刻工藝中,幫助定義器件結構。

金屬硬掩膜:常用TiN,用于定義圖案。

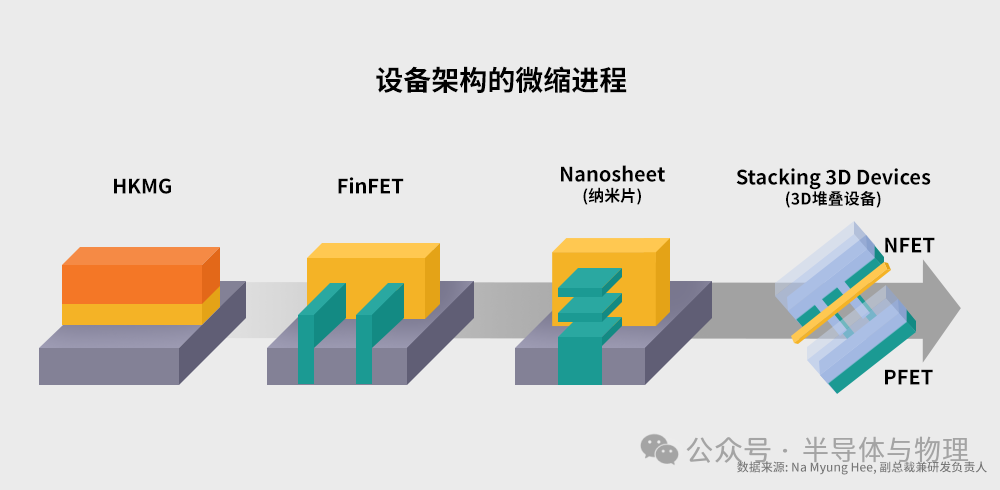

自對準雙重成像(SADP)ALD利用Spacer層實現更精細的圖案化,適用于FinFET中Fin結構的制造。

FinFET:利用Spacer層在心軸圖案邊緣覆蓋的側壁圖形作硬掩膜,實現空間倍頻的效果。

高K金屬柵(HKMG)ALD用于沉積高介電常數材料和金屬柵極,提高晶體管性能,特別是在28納米及以下制程中。

高K介質層:HfO2是目前最普遍的選擇,ALD是其最佳的制備工藝。

金屬柵:由于Hf元素與多晶硅柵容易發生化學反應,兼容性不佳,因此金屬柵技術應運而生。

其他應用ALD在金屬銅互聯擴散阻擋層等技術中也有廣泛應用。

金屬銅互聯擴散阻擋層:防止銅擴散,保護器件性能。

通過上述介紹,我們可以看到,PVD、CVD和ALD三種薄膜沉積技術各有特點和優勢,它們在半導體制造過程中發揮著不可替代的作用。PVD主要用于金屬膜層的沉積,CVD適用于多種介質膜層和半導體膜層的沉積,而ALD則在先進制程中展現出卓越的膜厚控制和臺階覆蓋能力。這些技術的不斷發展和完善,為半導體行業的進步提供了堅實的基礎。

-

芯片

+關注

關注

453文章

50387瀏覽量

421783 -

半導體

+關注

關注

334文章

27003瀏覽量

216265 -

工藝

+關注

關注

4文章

575瀏覽量

28752

原文標題:芯片制造:薄膜工藝

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

《炬豐科技-半導體工藝》IC制造工藝

半導體設備行業跟蹤報告:ALD技術進行薄膜沉積工藝優勢

基于PVD 薄膜沉積工藝

半導體前端工藝之沉積工藝

一文詳解半導體薄膜沉積工藝

一文詳解半導體薄膜沉積工藝

評論