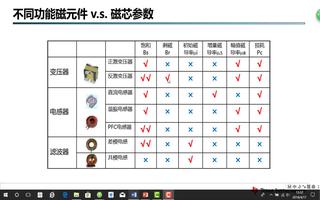

LUCT是什么?

第一層時鐘樹和第二層時鐘樹

時鐘樹設(shè)計及其設(shè)計方式是引起系統(tǒng)芯片性能差異的主要原因。

從歷史角度看,ASIC時鐘樹設(shè)計人員利用商用自動化工具設(shè)計時鐘樹,以確保執(zhí)行時間等性能取得預(yù)期結(jié)果,但是,這種方法的時鐘偏差和插入延時等性能卻不盡人意,另外,高復(fù)雜性、頻率和尺寸設(shè)計使得傳統(tǒng)方法完全沒有可行性。

低不確定性時鐘樹[LUCT]設(shè)計及算法與在系統(tǒng)芯片上實現(xiàn)的第一層時鐘樹的物理定義有關(guān),能夠讓設(shè)計人員克服傳統(tǒng)設(shè)計方法的所有低效率問題。

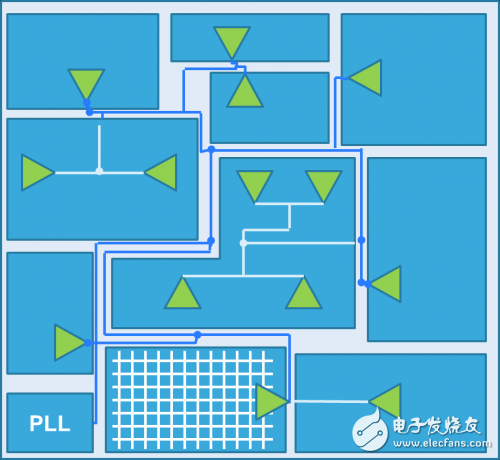

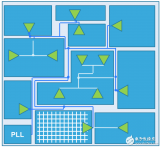

從頂層的根時鐘網(wǎng)絡(luò)(通常是PLL輸出)到中層時鐘網(wǎng)絡(luò),LUCT是一個高質(zhì)量的負(fù)載均衡的時鐘樹,其目標(biāo)是將時鐘信號從中央鎖相環(huán)PLL送到芯片的大部分區(qū)域,詳情參見參考文獻(xiàn)[1]。該文獻(xiàn)詳細(xì)介紹了低不確定性時鐘樹[LUCT]方法和架構(gòu),概括了從規(guī)格定義到單元布局和時鐘合成的全部相關(guān)設(shè)計流程。

按照參考文獻(xiàn)[2]的定義,這種時鐘分配方法屬于結(jié)構(gòu)化時鐘樹。文獻(xiàn)[2]還概括了現(xiàn)有的不同的時鐘設(shè)計方式。從時鐘源到寄存器,整個時鐘樹由第一層時鐘樹和第二層(或本地)時鐘樹組成。商用EDA工具需要實現(xiàn)本地時鐘樹。

LuctGenKit是意法半導(dǎo)體數(shù)字ASIC產(chǎn)品部的設(shè)計方法小組研發(fā)的時鐘設(shè)計工具,可完成LUCT架構(gòu)的物理實現(xiàn)過程。

圖1:在ASIC設(shè)計中優(yōu)化時鐘分配

LUCT工具主要特性

LuCT時鐘合成工具提供LuCT方法中的所有重要特性:

o 均衡的時鐘樹

- 長度均等和主動負(fù)載匹配

- 障礙感知

- 使用低電阻的高層金屬層傳輸信號

- 屏蔽和寄生匹配

o 增強(qiáng)型訂制單元庫,滿足各種信號強(qiáng)度需求

o 支持多種制造工藝,例如,32/28bulk,28fdsoi等

o 模塊布局,障礙布局與避障

o 與布局布線環(huán)境完全集成

LuCT設(shè)計流程

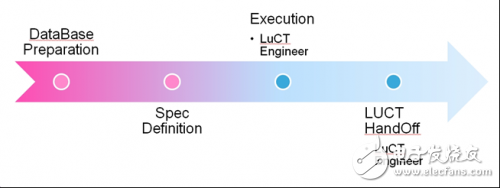

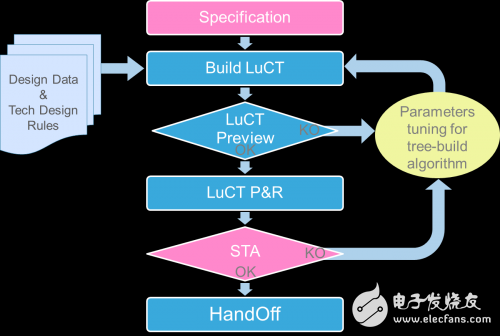

圖2:LuCTgenKit設(shè)計流程

LuCTgenKit設(shè)計流程分為四個階段,本文下面章節(jié)將給予詳細(xì)討論。該工具可簡化復(fù)雜ASIC設(shè)計,在有多個工程師參與整個項目的物理實現(xiàn)的設(shè)計環(huán)境中效果特別明顯。在一個典型設(shè)計組織內(nèi),物理實現(xiàn)的初始階段是數(shù)據(jù)庫準(zhǔn)備和規(guī)格定義,最后階段的工作主要是由專門的LuCT工程師來完成。一旦數(shù)據(jù)庫準(zhǔn)備和規(guī)格定義都完成后,僅一名LuCT設(shè)計工程師在一個工作日內(nèi)即可完成整個頂層時鐘樹(可能不只一個時鐘樹)的實現(xiàn)和定案工作。

LuCT tool 數(shù)據(jù)庫準(zhǔn)備

數(shù)據(jù)庫準(zhǔn)備包括必要的設(shè)計檢查、布局規(guī)劃合理性驗證、讀取電源網(wǎng)格形狀屬性和布局布線工具。其中,布局布線工具用于連接特殊的增強(qiáng)型時鐘庫,并通過LuCT創(chuàng)建算法確保時鐘庫布局連貫。本階段還是使結(jié)構(gòu)化時鐘樹利用現(xiàn)有技術(shù)取得最高性能的關(guān)鍵步驟,特別是在降低電壓降和抗串?dāng)_方面。

LuCT tool LuCT規(guī)格定義

每一個時鐘合成,都需要在該工具內(nèi)輸入下面信息:

o 技術(shù)節(jié)點(diǎn)

o 主要時鐘樹起點(diǎn)(PLL)

- X 和Y坐標(biāo)

o 主要時鐘樹終點(diǎn)

- 每個葉子上的X和Y坐標(biāo)

o 頻率范圍

o 工藝-電壓-溫度角

o 時鐘單元參數(shù)選擇

設(shè)計人員可通過圖形用戶界面輸入所需的全部數(shù)據(jù)和設(shè)計方式。

LuCT tool 執(zhí)行: 創(chuàng)建LuCT

低不確定性時鐘樹合成自動化工具捆綁下列對象:

- 設(shè)計規(guī)格

- 布局規(guī)劃信息(包括布局障礙和布線障礙)

- 電源網(wǎng)格

- 設(shè)計和布局規(guī)則

- 網(wǎng)表

- 布局

- 圖形用戶界面

- 報告

- 定案

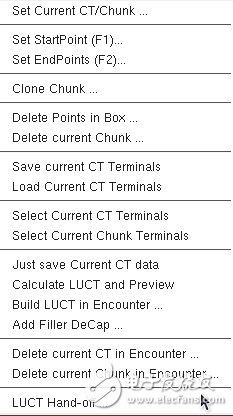

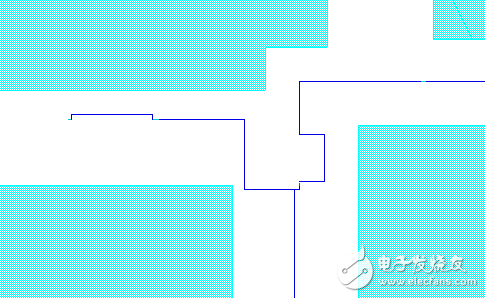

圖3:LuCT應(yīng)用軟件圖形用戶界面菜單

LuCT工具通過意法半導(dǎo)體獨(dú)有的算法生成時鐘樹拓?fù)洹T撍惴ɑ诰獾穆窂介L度和等長同質(zhì)布線。芯片布局規(guī)劃建模和初始化以及路徑計算需要Lemon C++圖形函數(shù)庫[4]。時鐘樹創(chuàng)建過程包含下列步驟:

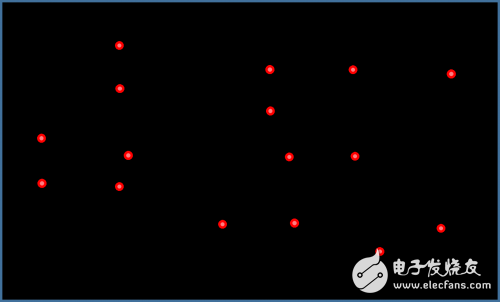

o 網(wǎng)格生成: 在從布局規(guī)劃讀取數(shù)據(jù)后,生成障礙模型和電源網(wǎng)格形狀模型。從這些模型開始計算一個代表LuCT算法定義的布局布線間距的點(diǎn)集合(網(wǎng)格)。

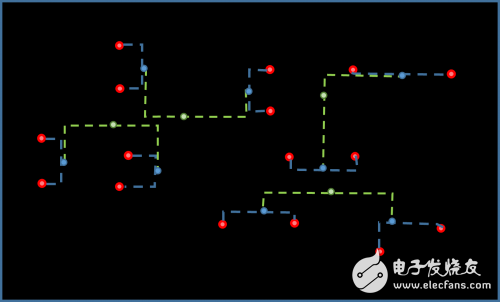

o 構(gòu)建二進(jìn)制樹:使用意法半導(dǎo)體獨(dú)有算法將葉子分組,每組一對。通過計算長度均等的包含避障點(diǎn)的路徑和合并點(diǎn)(即該路徑中間的一點(diǎn))的方式將每對樹葉合并。通過這種方法按照遞歸方式合并新的葉子(合并點(diǎn)),直到只剩下一個點(diǎn)(樹根)為止,詳見圖4到圖6。

o 插入時鐘驅(qū)動器和布線:插入時鐘驅(qū)動器和優(yōu)化布線是采用一個自下向上的方法,分別考慮障礙布局和障礙布線。

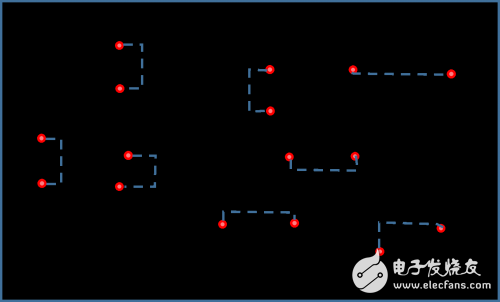

圖 4:終點(diǎn)集合

圖5:LuCT創(chuàng)建樹算法配對決策與合并

圖 6:上一級產(chǎn)生的合并點(diǎn)配對合并

圖7 :采用LuCT工具的設(shè)計流程

一旦生成時鐘樹結(jié)構(gòu),只要在布局布線CAD工具內(nèi)使用腳本程序即可實現(xiàn)布局。對于多個并行時鐘驅(qū)動器的高性能布線/走線、通孔布局和電源噪聲感知布局,取得布局配置需要使用自定義規(guī)則。

通過修改幾個對二進(jìn)制樹架構(gòu)和創(chuàng)建有很大影響的參數(shù),可以優(yōu)調(diào)算法。

下面是一些參數(shù)示例:

o 葉子對生成:可自動或人工生成

o 路徑距離計算:可以是純Manhattan方式或能夠感知障礙

o 彎折最小化:為布線網(wǎng)絡(luò)選擇適合的吸引力

o 通過在每個布線/合并階段全局重映射中心,吸引合并區(qū)向現(xiàn)階段的中心轉(zhuǎn)移

o 時鐘樹性能指標(biāo):障礙強(qiáng)度、時鐘偏差/插入延時性能與障礙的均衡性、時鐘擁堵。

LuCT 工具 示例和結(jié)果

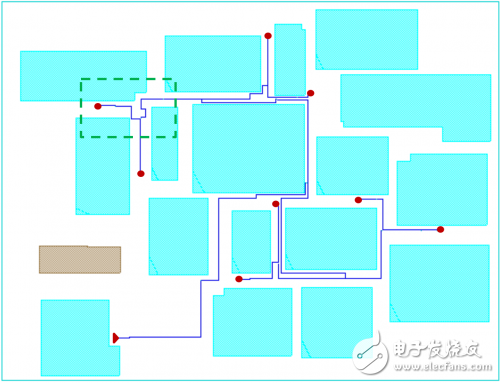

圖8所示是按照上面討論的方法使用LuCTgenKit設(shè)計 28FDSOI芯片的時鐘樹。1GHz時鐘信號從時鐘源分配到8個樹葉,避繞障礙,平衡時鐘偏差,查覺障礙。圖9所示當(dāng)連接高層葉子對時如何執(zhí)行等長計算。

圖 8

圖 9

這個示例的主要結(jié)論是,按照基延遲(base delay)計算,時鐘偏差是非常有限的,不過,出現(xiàn)大量的不常見路徑。

-

時鐘

+關(guān)注

關(guān)注

10文章

1720瀏覽量

131364

發(fā)布評論請先 登錄

相關(guān)推薦

什么是ADC?ADC主要特性有哪些

傳感器特性及其標(biāo)定

LUCT工具主要特性及不確定性時鐘樹設(shè)計方法和算法的介紹

電橋的主要作用及其基本特性測量

LUCT工具主要特性及其使用教程

LUCT工具主要特性及其使用教程

評論