近年間,云計算與人工智能技術(shù)的蓬勃興起,計算中心面臨著數(shù)據(jù)效率低、能耗大等核心挑戰(zhàn),這促使學(xué)術(shù)界和工業(yè)界重新聚焦。

開宗明義,定義先行。

首先,我們先來了解一下什么是存算一體:

存算一體是通過在存儲器中嵌入計算能力,實現(xiàn)數(shù)據(jù)存儲與計算的緊密結(jié)合。其技術(shù)不僅能夠顯著提升計算效率,還能大幅降低能耗。

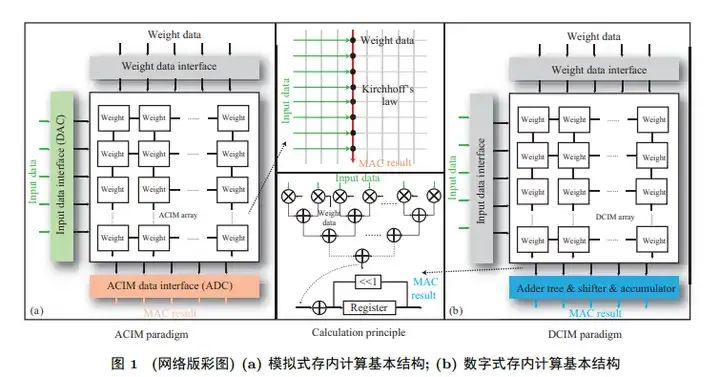

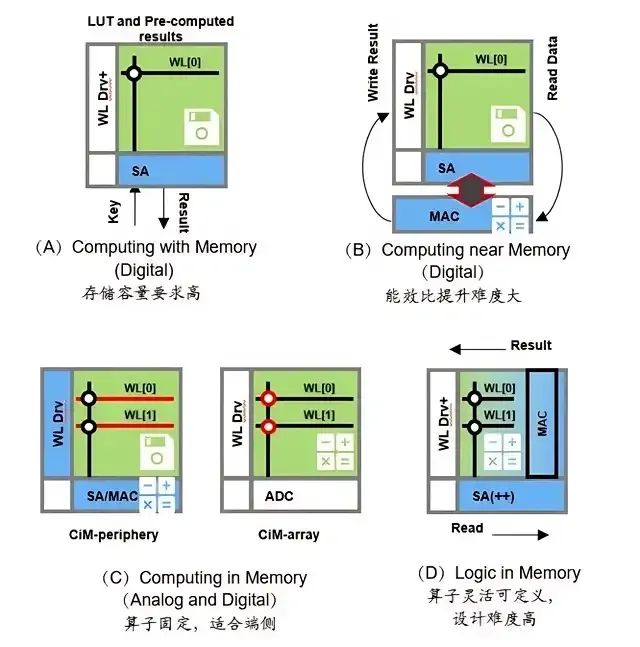

緊接著,存算一體技術(shù)分為三類:近存計算(Processing Near Memory, PNM)、存內(nèi)處理(Processing In Memory, PIM)和存內(nèi)計算(Computing In Memory, CIM)。

近存計算:不改變計算單元和存儲單元本身設(shè)計功能,采用先進的封裝方式及合理的硬件布局和結(jié)構(gòu)優(yōu)化,增強二者間通信寬帶,增大傳輸速率。

存內(nèi)處理:側(cè)重于將計算過程盡可能地嵌入到存儲器內(nèi)部,這種方法的能效比通常較高,但計算精度可能受限。另一種思路是在存儲器內(nèi)部集成額外的計算單元,以支持高精度計算。

存內(nèi)計算:存儲單元與計算單元完全融合,無獨立計算單元,通過存儲器顆粒上嵌入算法,由存儲器芯片內(nèi)部的存儲單元完成計算操作。

圖源:Google

圖源:Google

事實上,存算一體的概念由來已久。早在1969年,斯坦福研究所的Kautz等人提出了存算一體計算機的概念。其受限于當時的芯片制造技術(shù)和算力需求的匱乏,那時存算一體僅僅停留在理論研究階段,并未得到實際應(yīng)用。

因此,后續(xù)研究人員在芯片電路結(jié)構(gòu)、計算架構(gòu)與系統(tǒng)應(yīng)用等方面開展了一系列研究。但受限于電路設(shè)計復(fù)雜度與工藝難度,后續(xù)的大部分研究本質(zhì)上實現(xiàn)的是 “近存計算”,其與存內(nèi)計算最大的區(qū)別是,近存計算仍然需把數(shù)據(jù)從內(nèi)存中讀取出來之后再就近進行計算,計算的結(jié)果再存儲到內(nèi)存當中。

與此同時,存算一體技術(shù)的核心在于將數(shù)據(jù)存儲與計算融合在同個芯片的同片區(qū)之中,從而徹底消除馮諾依曼計算架構(gòu)的瓶頸;將通過存儲器內(nèi)部進行數(shù)據(jù)處理或計算,此技術(shù)能夠大幅減少數(shù)據(jù)在計算與存儲之間的傳輸時間,提升整體性能。

尤其,在馮諾伊曼架構(gòu)中,計算單元與內(nèi)存是兩個分離的單元。計算單元根據(jù)指令從內(nèi)存中讀取數(shù)據(jù),在計算單元中完成計算和處理,完成后再將數(shù)據(jù)存回內(nèi)存。

然而,整個過程中,存儲器與處理器之間數(shù)據(jù)交換通路窄,以及由此引發(fā)的高能耗形成兩大難題,在存儲與計算之間筑起一道“存儲墻”。能耗方面,大部分能耗在數(shù)據(jù)搬運過程中產(chǎn)生,數(shù)據(jù)搬運功耗是計算功耗的1000倍。而數(shù)據(jù)搬運速度方面,AI運算需1PB/s,但DRAM 40GB-1TB/s 都遠達不到要求。

存算一體技術(shù)的分類

存算一體技術(shù)的分類

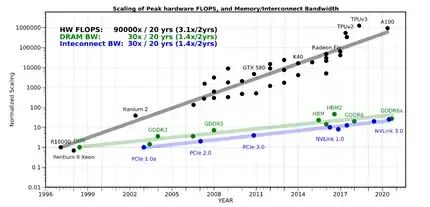

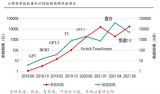

過去數(shù)載,處理器性能以每年大約55%的速度提升,而相比之下,內(nèi)存性能的提升則顯著放緩,其年增長率僅約為10%。這種長期存在的性能發(fā)展不均衡現(xiàn)象,導(dǎo)致當前存儲系統(tǒng)的訪問速度相較于處理器的計算能力出現(xiàn)了顯著的滯后現(xiàn)象。

目前,在傳統(tǒng)計算機的設(shè)定里,存儲模塊是為計算服務(wù)的,因此設(shè)計上會考慮存儲與計算的分離與優(yōu)先級。但如今,存儲和計算不得不整體考慮,以最佳的配合方式為數(shù)據(jù)采集、傳輸和處理服務(wù)。

其中,雖然多核(例如CPU)/眾核(例如GPU)并行加速技術(shù)也能提升算力,但在后摩爾時代,存儲帶寬制約了計算系統(tǒng)的有效帶寬,芯片算力增長步履維艱。從處理單元外的存儲器提取數(shù)據(jù),搬運時間往往是運算時間的成百上千倍,整個過程的無用能耗大概在60%-90%之間,能效非常低,“存儲墻”成為了數(shù)據(jù)計算應(yīng)用的一大障礙。

其次,存內(nèi)計算和存內(nèi)邏輯,即存算一體技術(shù)直接利用存儲器進行數(shù)據(jù)處理或計算,從而把數(shù)據(jù)存儲與計算融合在同一個芯片的同一片區(qū)之中,從而徹底消除馮諾依曼計算架構(gòu)瓶頸,以便適用于深度學(xué)習(xí)神經(jīng)網(wǎng)絡(luò)這種大數(shù)據(jù)量大規(guī)模并行的應(yīng)用場景。

算力發(fā)展速度遠超存儲

算力發(fā)展速度遠超存儲

顯然,存算一體技術(shù)的演進軌跡導(dǎo)向了計算精度的提升、算力輸出的增強及能效比優(yōu)化的高階,以此映射出該技術(shù)內(nèi)進步邏輯的必然走向。

前移至感知端,向 “極致低功耗” 邁進:面向可穿戴設(shè)備、物聯(lián)網(wǎng)設(shè)備等端側(cè)市場,打造超低功耗、超低成本的解決方案。當前感知芯片采集到的模擬信號依賴模數(shù)轉(zhuǎn)換器轉(zhuǎn)換成數(shù)字,信號再通過智能處理器進行處理,速度慢、功耗高。

后移至邊緣端/云端,向 “極致大算力”邁進:面向邊緣端/云端服務(wù)器、數(shù)據(jù)中 心與自動駕駛等場景,利用存算一體芯片大規(guī)模并行運算的特點,打造超大算力解決方案。當前的邊緣端/云端處理器大多基于 GPU 平臺,而 GPU 仍然受 “存儲墻” 限制,存在巨大的數(shù)據(jù)通信開銷,導(dǎo)致其實際算力不到標稱算力的 10%。據(jù)分析, 以 ChatGPT 為代表的主流大模型的基本組成單元 Transformer 中約有 90% 以上的運算為大規(guī)模矩陣運算,可以基于存算一體陣列高效完成。

協(xié)同異構(gòu)架構(gòu)與異構(gòu)集成,實現(xiàn)合力突圍:異構(gòu)架構(gòu)將不同計算架構(gòu)、不同功能的硬件單元進行融合,充分發(fā)揮各自的優(yōu)勢,彌補各自的不足,以實現(xiàn)系統(tǒng)更高的性能。例如,單一的數(shù)字存算一體架構(gòu)或模擬存算一體架構(gòu)在精度、能效、面積、成本等指標上各有優(yōu)劣,采用單一架構(gòu)難以兼具各項性能。

驅(qū)動 EDA 設(shè)計工具與應(yīng)用工具鏈開發(fā):隨著存算一體芯片 從 0 到 1 的突破,已驗證了其在 AI 應(yīng)用中的發(fā)展?jié)摿εc市場前景,進而吸引上下游企業(yè)的加入,催生相應(yīng)的自動化 EDA 設(shè)計工具、開發(fā)環(huán)境、仿真器、編譯工具與智能算法的協(xié)同發(fā)展,縮短芯片的研發(fā)周期與應(yīng)用開發(fā)周期,進而推動開源與標準生態(tài)的建立與繁榮,形成良性循環(huán),加速存算一體芯片的規(guī)模化量產(chǎn)與應(yīng)用。

綜上所述,當前的存算一體芯片研究集中在單點技術(shù),且在器件、電路、架構(gòu)、EDA工具及系統(tǒng)應(yīng)用等方面仍然存在諸多技術(shù)待解決。

另外,從技術(shù)的角度,存算一體芯片未來的研究將圍 繞新型器件優(yōu)化、低功耗數(shù)模混合電路設(shè)計、高性能異構(gòu)芯片架構(gòu)、先進集成與封裝、工具鏈開發(fā)等。

-

處理器

+關(guān)注

關(guān)注

68文章

19165瀏覽量

229128 -

存儲器

+關(guān)注

關(guān)注

38文章

7452瀏覽量

163606 -

算力

+關(guān)注

關(guān)注

1文章

928瀏覽量

14744 -

存算一體

+關(guān)注

關(guān)注

0文章

100瀏覽量

4288

原文標題:打破算力極限,存算一體技術(shù)并駕齊驅(qū)

文章出處:【微信號:奇普樂芯片技術(shù),微信公眾號:奇普樂芯片技術(shù)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

存算一體大算力AI芯片將逐漸走向落地應(yīng)用

比存算一體更進一步,“感存算一體化”前景如何?

探索存內(nèi)計算—基于 SRAM 的存內(nèi)計算與基于 MRAM 的存算一體的探究

存算一體技術(shù)路線如何選

知存科技數(shù)模混合存算一體AI芯片專利解析

存算一體芯片在可穿戴設(shè)備市場有哪些機會

2023年存算一體是芯片設(shè)計的技術(shù)趨勢

關(guān)于存算一體,我們和ChatGPT聊了聊

基于3DIC架構(gòu)的存算一體芯片仿真解決方案

特斯拉的下一代AI芯片:存算一體

ChatGPT開啟大模型“軍備賽”,存算一體開啟算力新篇章

存算一體技術(shù)的分類

存算一體技術(shù)的分類

評論