以下文章來源于FPGA技術實戰,作者FPGA技術實戰

前言:Xilinx7系列FPGA集成了新一代PCI Express集成塊,支持8.0Gb/s數據速率的PCI Express 3.0。本文介紹了7系列FPGA PCIe Gen3的應用接口及一些特性。

1. PCI Express規范演進

PCIe是一種高速串行計算機擴展總線標準,旨在替代傳統的PCI和AGP總線標準,提供更高的數據傳輸速率和更好的信號完整性?。PCIe規范自2003年推出以來,已經從最初的1.0升級到了7.0,提供了更高的帶寬和速度。?表1總結了PCIe基本規范的演變。

表1:PCIe基本規范的演變

1.由于數據包開銷、流量開銷和其他系統效率低下,可實現的系統帶寬小于有效帶寬。

除了修訂基本規范外,PCI-SIG還推廣了支持特定應用的配套規范。一個正在迅速采用的配套規范是I/O虛擬化,特別是Single Root I/O虛擬化(SR-IOV)。SR-IOV大大提高了共享和虛擬化環境中的I/O利用率,Xilinx 7系列FPGA支持此功能。

2. 7系列FPGA PCI Express概述

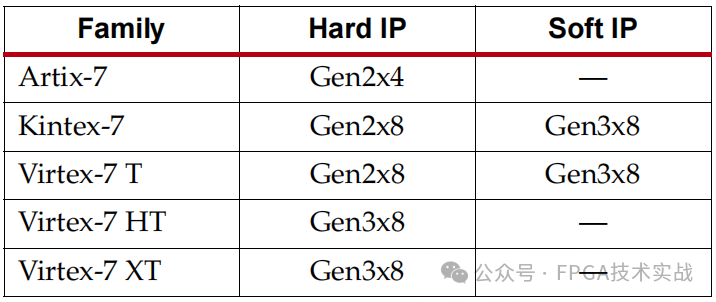

每個Xilinx 7系列FPGA系列都支持PCIe集成根端口和端點解決方案。Artix-7設備最多支持Gen2x4硬核配置。Kintex-7和Virtex-7 T設備最多支持Gen2x8硬核配置。Virtex-7 XT和HT設備具有集成的Gen 3硬核內核,最多8個通道。除了PCIe IP的集成外,第三方聯盟合作伙伴Northwest Logic和PLDA還提供針對Kintex-7和Virtex-7系列的Gen3x8軟IP解決方案。表2總結了每個器件家族支持的IP層級。

表2:7系列FPGA支持的Lane寬度和速度等級

7系列FPGA的集成IP可以使用簡單的基于GUI的工具流進行配置,以創建端點、根端口或根復合體解決方案。系統設計者能夠控制許多可配置的參數,如通道寬度、線速率、最大有效載荷大小、FPGA邏輯接口速度、參考時鐘頻率和基址寄存器設置。另外,Xilinx還提供參考設計以加快設計進度。這些目標參考設計包括PCIe設計的所有組件,如DMA控制器、自定義IP、設備驅動程序和軟件應用程序。

3. 用于Virtex XT和HT設備的PCI Express Gen 3集成IP

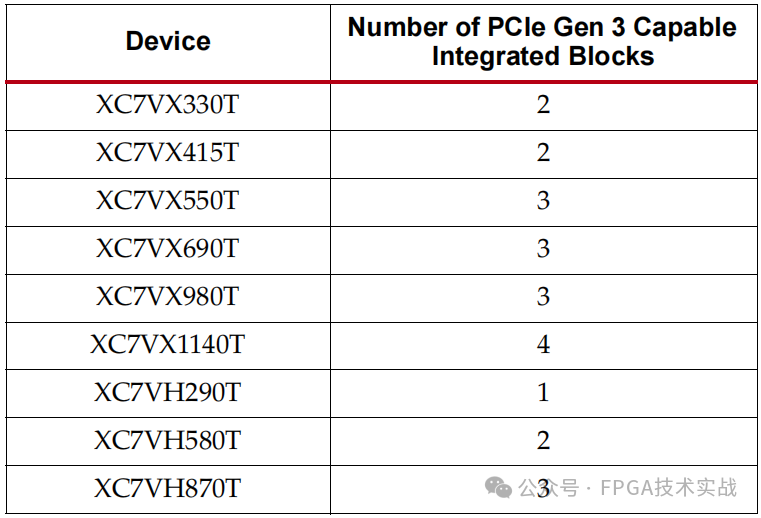

Virtex-7 XT和HT設備支持多個集成的Gen 3集成塊,每個集成塊最多八個通道。該集成塊能夠使用128B/130B編碼以每通道8.0Gb/s的規定數據速率運行。表3顯示了具有Gen 3集成塊的7個系列器件以及每個設備的塊數。

表3:Virtex-7 系列具有Gen 3功能的硬塊器件

3.1 PCIe Gen 3收發器在7系列中的優勢

GTH收發器包含允許在PCIe Gen 3數據速率下非常穩健運行的功能。這些功能包括:

?收發器加重/均衡

?自適應連續時間線性均衡器(CTLE)

?自適應決策反饋均衡器(DFE)

收發器加重電路設計用于克服高頻信道插入損耗,并實現為3抽頭FIR濾波器。這些抽頭是可編程的,通常,用戶不需要顯式設置抽頭值,因為這是由PCIe Gen 3鏈路均衡協議自動處理的。

GTH收發器中的CTLE和DFE電路協同工作,可補償高達20dB的損耗。CTLE采用全自動自適應算法,持續監測輸入信號,并優化高通濾波器功能的頻率響應。這種自適應功能減輕了用戶的負擔,解決了過均衡或欠均衡的問題。

DFE由七個固定抽頭和四個獨立的滑動抽頭實現。當PCIe在背板上使用時,這非常有用,這在許多有線通信和數據中心應用中都很常見。與CTLE類似,DFE也完全自適應于抽頭值和滑動抽頭的位置。

3.2 PCIe Gen3數據吞吐量

PCI-SIG的目標是將每一代PCIe的有效數據吞吐量翻一番,第3代也不例外。重要的是要注意,有效數據吞吐量(有時稱為有效數據傳輸速率)與原始數據傳輸速率(如8Gb/s線路速率)不同。有效數據吞吐率取決于許多變量,例如:

?Lane寬度

?線速率

?系統最大有效負載大小和最大讀取請求大小

?TLP開銷

?鏈路管理(數據鏈路層數據包)

?編碼丟失

?DMA開銷

當配置為在具有256字節系統最大有效負載大小的真實系統中運行的具有x8 Gen 3功能的內核時,用于PCIe的7系列Gen 3集成塊能夠實現每個方向超過7GB/s的持續吞吐量。

3.3 與內存接口

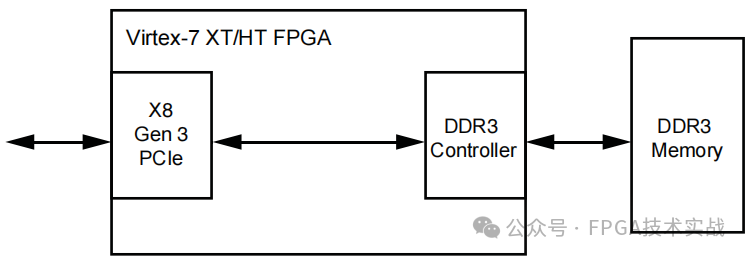

大多數PCIe應用程序使用某種類型的內存進行數據緩沖,通常是DDR SDRAM。

圖1:DDR3內存與Virtex-7 XT/HT FPGA的接口

在確定內存帶寬要求時,設計人員應使用2.5倍的帶寬乘數來考慮讀寫方向和任何額外的開銷,如內存尋址。

例如,如果從PCIe鏈路持續傳輸6.5GB/s,并且所有這些數據都緩沖在DDR3內存中,則設計人員可以計算以下內容以確定內存帶寬和/或接口寬度要求。

確定內存帶寬要求

持續傳輸所需的總內存帶寬:

6.5 GB/s*2.5=16.25 GB/s

示例:如果使用具有1866Mb/s DDR3功能的內存,設計人員可以計算數據接口必須有多寬才能跟上16.25 GB/s。轉換為Gb/s:

16.25GB/s*8位/字節=130Gb/s。

計算DDR3內存所需的接口寬度:

每個引腳130 Gb/s÷1866 Mb/s=約70個引腳

此計算表明,以1866 Mb/s運行的標準72針DDR3接口可以跟上x8 Gen 3 PCI Express鏈路的全雙工數據。支持較慢DDR數據速率(如1600 Mb/s)的FPGA需要額外的引腳和組件。

3.4 PCIe Gen3其他高性能功能

PCIe Gen3集成塊包含許多功能,可實現更好的系統性能。這些功能包括:

?用于流量類型的高性能專用AXI4接口(增強型AXI-4流)

?跨越256位寬接口的數據

?內置標簽管理,最多可處理64個未完成的讀取請求

?靈活的接收緩沖;可配置高達8KB的請求空間和16KB的完成空間

?內置多功能和SR-IOV支持

AXI4接口上的奇偶校驗保護

?對所有內部緩沖存儲器進行ECC保護

?可調整大小的基址寄存器(RBAR)

?地址翻譯服務(ATS)

?原子操作事務

?TLP處理提示能力(TPH)

?優化緩沖區沖洗/填充能力(OBFF)

?動態功率分配能力(DPA)

?功率預算能力(PB)

3.5 可擴展、優化的AXI接口

Xilinx部署的AMBA4 AXI4規范允許以一致的方式連接IP塊,同時更好地利用設計資源。

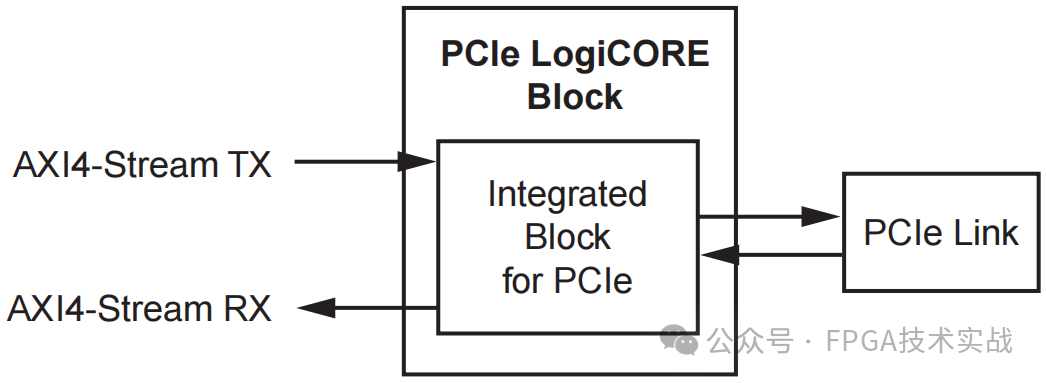

所有適用于7系列FPGA的PCIe解決方案均按照AMBA4 AXI4規范設計。AXI接口提供了三種風格,每種風格都針對不同的客戶用例量身定制。

1.Basic AXI4-Stream:此接口類似于舊Xilinx FPGA系列中的傳統TRN接口。該接口是將基于TRN的設計遷移到7系列設備的最簡單接口,由發送和接收AXI4流接口組成。此接口可用于Artix-7、Kintex-7和Virtex-7 T FPGA上的PCI Express解決方案(在Virtex-7 XT設備上不可用)。

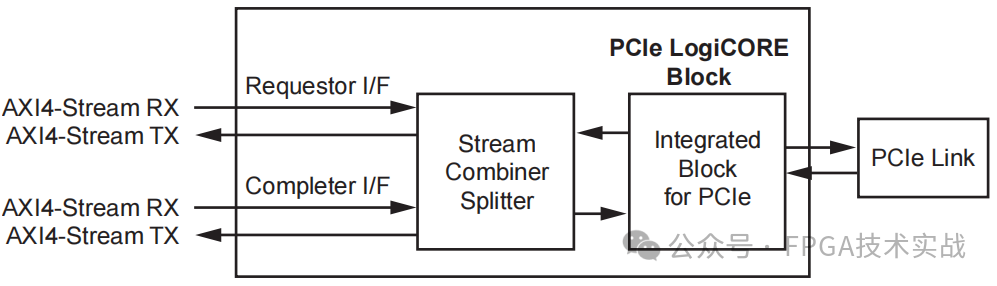

圖2:AXI4流基本界面

2.Enhanced AXI4-Stream:此接口類似于基本的AXI4 Stream接口,但通過將數據流拆分/組合為Completer和Requester流對其進行了擴展。增強版本還允許可選功能,如數據包去分級、數據重新排列和完成標簽管理。此接口可用于PCI Express解決方案的Virtex-7 HT和XT FPGA(在Virtex-7 T、Artix-7和Kintex-7設備上不可用)。見圖3。

圖3:增強型AXI4流接口

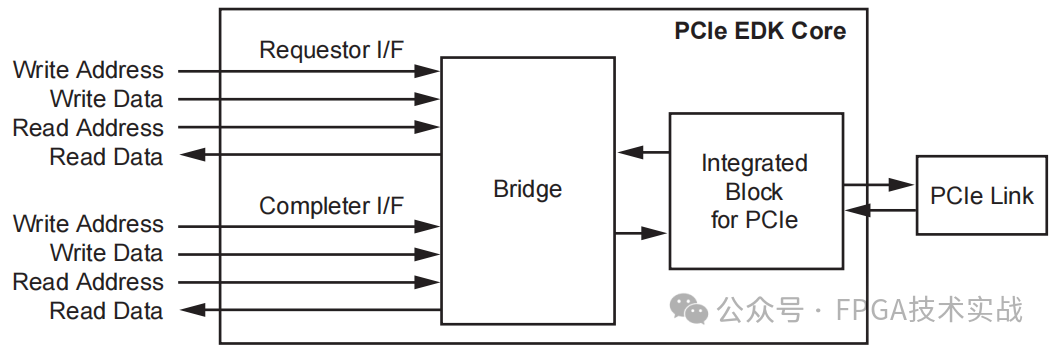

3.AXI4:這是一個內存映射接口,用于基于處理器系統的內核。此接口是嵌入式設計的遷移路徑,可用于PCIe解決方案的Artix-7、Kintex-7和Virtex-7 T、HT和XT FPGA。

圖4:AXI4接口

4. 7系列FPGA的PCIe新功能

7系列FPGA PCIe解決方案中添加了許多新功能,為設計人員提供了PCIe性能、靈活性和易用性。

4.1 PCIe IP塊的快速初始化

PCIe基本規范要求PCIe鏈路在電源穩定后100ms內準備好進行鏈路訓練。傳統上,這對大型FPGA(>100000個邏輯單元)來說是一個挑戰,因為使用常見的閃存設備配置大型FPGA可能需要100多ms。

傳統上使用"蠻力"方法來解決100ms的要求。通常,設計人員使用最快、最寬的閃存設備來實現必要的帶寬,以滿足配置時間要求。在某些情況下,需要使用多個閃存設備和CPLD來實現所需的帶寬。雖然從軟件的角度來看,這可能是最簡單的方法,但由于BOM成本的增加,它通常是最昂貴的。這種方法還使用了寶貴的FPGA I/O,特別是在使用寬輸入總線時,并且隨著Xilinx FPGA的尺寸增長到200萬個邏輯單元甚至更高,這種方法很快就會過時。

注意:此問題通常僅限于端點附加卡設計。

4.2 Tandem PROM和Tandem PCIe

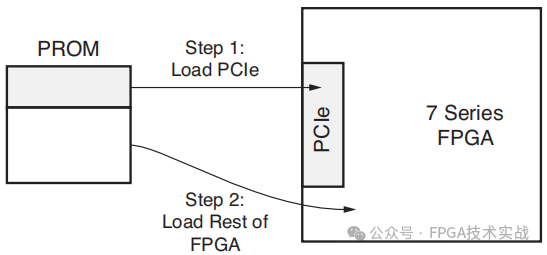

Tandem PROM方法是7系列器件中的新方法,是最簡單、最便宜的實現方法。在構建PCIe IP核時,用戶指示實現工具通過簡單的軟件交換機創建兩級比特流。比特流的第一階段僅包含配置PCIe集成塊所需的配置幀。配置后,FPGA啟動序列發生,PCIe鏈路變為活動狀態,因此很容易滿足100毫秒的要求。然后,在PCIe枚舉/配置系統過程中加載FPGA配置的其余部分。兩階段比特流方法可以使用廉價的閃存設備來保存比特流。

圖5:串聯PROM方法

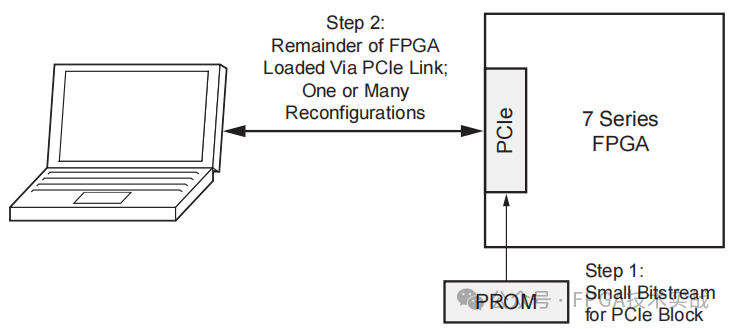

Tandem PCIe解決方案基于Tandem PROM技術構建,允許用戶通過PCI Express鏈路加載第二級比特流。

4.3部分重構

要實現通過PCIe連接的多個用戶應用程序,可以使用部分重新配置工具流。該方法依賴于比特流壓縮來滿足100ms的要求。初始比特流包含與內部配置訪問端口(ICAP)連接的PCe IP核。FPGA的大部分未配置。然后通過使用比特流壓縮來減小初始比特流的大小,從而允許快速初始化。

FPGA未配置部分的部分比特流通過PCe鏈路實時下載。使用部分重新配置工具流,設計者創建一個或多個可以駐留在主機中的應用程序(部分比特流)。高性能計算市場中的協同處理算法加速器等應用受益于這種動態可重編程性。

圖6:部分重新配置工具流程

4.4數據跨接

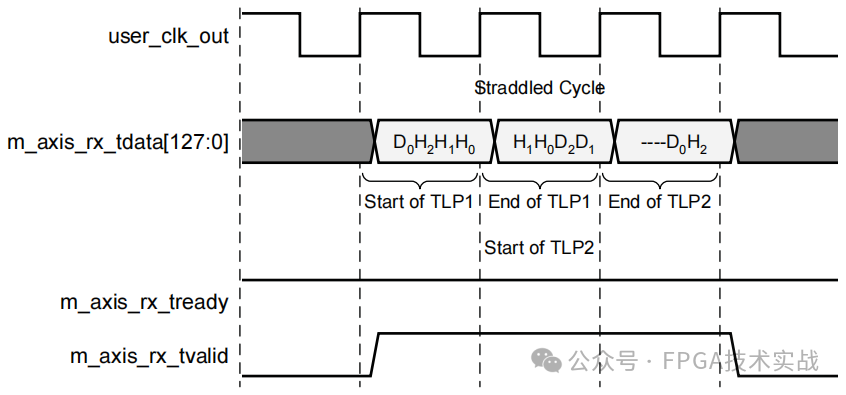

Xilinx對7系列FPGA中的PCIe集成塊進行了許多增強,以提高內核的性能。大多數基于FPGA的解決方案要求用戶界面上的事務層數據包(TLP)以對齊的方式接收,即當TLP結束時。在下一個時鐘周期之前,無法從IP核讀取下一個TLP。

這些解決方案在數據流中引入了缺口,從而降低了整體數據吞吐量。7系列FPGA能夠在用戶界面上跨包(允許一個TLP在同一時鐘周期結束,而另一個開始),從而允許PCIe內核以全線速率運行。這對于需要全線速帶寬的超高端應用非常重要。對于不需要極端帶寬且更喜歡對齊數據包的應用程序,增強的AXI Stream接口具有可選的對齊功能。

圖7:7系列數據跨接

除了支持跨數據包外,7系列FPGA還具有提高整體性能的功能,例如改進了用戶對信用分配方案的控制,以及新的流量控制功能,使用戶能夠更精細地控制已發布和未發布的流量。

4.5 讀取請求完成的標簽管理

當傳輸大于典型系統讀取完成邊界大小64字節的讀取請求TLP時,設計者必須承擔的一項艱巨任務是處理多個完成和無序返回。通常,設計者必須存儲傳出讀取請求的標簽,然后將這些標簽與傳入的完成TLP進行協調和管理。此外,設計者還必須監控錯誤情況,如完成超時。

標簽管理是發送讀取請求的總線主控DMA設計的一個必要功能,換句話說,就是從生產者“拉取”數據。這是通過管理傳出讀取請求的標簽并將傳入的完成與這些標簽進行協調來實現的。Virtex-7 HT和XT設備的PCIe解決方案可選地提供此標簽管理功能,大大簡化了DMA設計人員的設計要求。

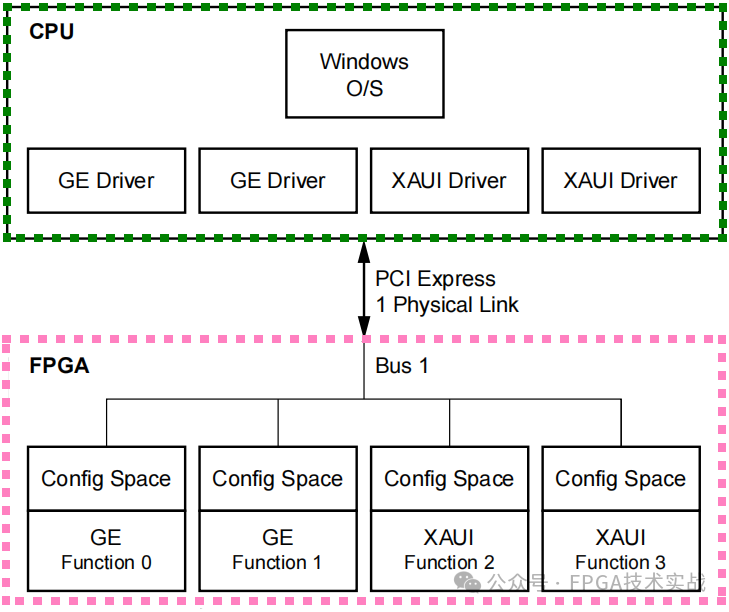

4.6 多功能

7系列FPGA能夠作為多功能設備運行。這種類型的設備具有多種功能,所有功能都共享一個PCIe鏈路。每個功能都有自己的PCIe配置頭空間。因此,從主機系統軟件的角度來看,每個功能在其自己的PCIe鏈路上都表現為一個單獨的PCIe設備。這大大簡化了設備驅動程序的開發和可移植性,因為驅動程序開發人員可以創建單個驅動程序,并為每個硬件功能復制它。見圖8。

圖8:多功能設備

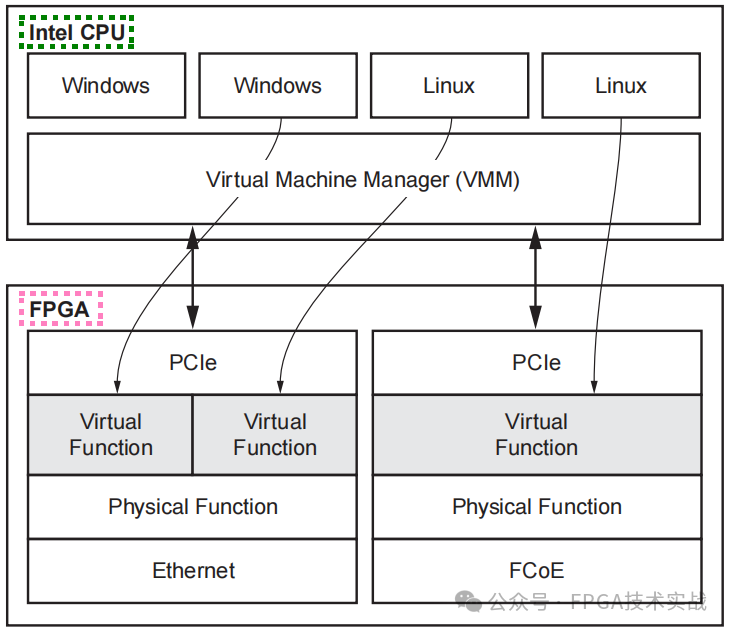

4.7 Single Root I/O虛擬化

Single Root I/O虛擬化(SR-IOV)允許在單個root(CPU子系統)上運行的多個客戶機(操作系統)訪問I/O設備,而不會在不支持SR-I0V的虛擬化系統中產生軟件損失。類似于多功能設備如何為每個物理功能提供單獨的配置空間,SR-IOV通過為訪問I/O設備的每個客戶操作系統提供虛擬功能(虛擬配置空間)來工作。因此,每個客戶操作系統都有自己的I/O設備“視圖”。

圖9:SR-IOV虛擬配置空間

支持SR-IOV的適配器在虛擬化環境中的I/O效率方面有了巨大的提高。SR-IOV不僅成為企業IT市場(數據中心)廣泛采用的標準,而且開始在通信和存儲網絡市場取得進展。

4.8 高級錯誤報告和端到端CRC

高級錯誤報告(AER)是一個可選功能,它為基于PCIe的系統中可能發生的錯誤類型提供了更大的粒度和控制。在非AER PCIe系統中,只定義了三種類型的錯誤:致命、非致命和可糾正。在大多數情況下,這三種定義的錯誤類型沒有為系統提供足夠的信息,無法從錯誤中優雅地恢復。啟用AER后,系統軟件可以確定特定錯誤的確切原因,并在可能的情況下嘗試恢復。

當用戶啟用時,7系列FPGA中的PCIe集成塊可選擇執行自動端到端CRC(ECRC)檢查和生成。已添加新端口以控制錯誤生成,并在檢測到ECRC錯誤時進行標記。設計者不再需要在FPGA中設計這種邏輯。AER和ECRC用于高可靠性和高可用性是關鍵驅動因素的應用。這些功能通常用于航空航天和國防、銀行和金融、通信和存儲等細分市場。

4.9 可調整大小的BAR

許多端點應用程序包含大量的本地內存,例如,高端圖形卡可以包含超過1 GB的DDR3 SDRAM。如基于32位的操作系統,無法將如此多的內存資源分配給單個實體。如果適配器沒有實現某種孔徑窗口方案,操作系統通常會忽略資源請求。因此,系統無法使用適配器。可調整大小的基址寄存器(BAR)功能為設計者提供了一些控制,這樣就不會發生這種情況。如果系統無法分配適配器請求的全部資源,它可以將BAR調整到更小、更可接受的孔徑,從而使適配器仍能在系統內運行。7系列FPGA中的PCIe解決方案完全支持可調整大小的BAR功能。

4.10 Atomic操作

Atomic Operations引入了三種新的TLP類型,旨在通過直接在I/O總線(在本例中為PCIe)上創建標準同步原語(如互斥和自旋鎖)來提高系統性能和延遲。這在任何具有多個生產者和消費者的系統中都很有用,例如多CPU系統。此功能的目標應用程序空間是協同處理和硬件加速適配器。

本文轉載自FPGA技術實戰公眾號

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602004 -

Xilinx

+關注

關注

71文章

2164瀏覽量

121036 -

計算機

+關注

關注

19文章

7430瀏覽量

87732 -

IP核

+關注

關注

4文章

326瀏覽量

49431

原文標題:Xilinx 7系列FPGA PCI Express IP核簡介

文章出處:【微信號:FPGA研究院,微信公眾號:FPGA研究院】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Altera Stratix V GX FPGA實現了與PCIe Gen3的兼容

用于 PCIe Gen-3 卡的高速前端參考設計

基于FPGA的高速以太網適配器卡必備的PCIe Gen3技術

PCIe GEN3 ECRC僅在離線模式下出錯

為什么在我的PCIe Gen3插槽上使用VC709不起作用?

請問XC7K325T-2FFG900支持PCIE PHY GEN3嗎?

符合PCIe Gen1,Gen2和Gen3標準的9端口PCIe時鐘發生器

PCIE高速傳輸解決方案FPGA技術XILINX官方XDMA驅動

PCIe Gen-3高速前端卡參考設計

Altera率先實現Stratix V GX FPGA與PCIe Gen3交換機互操作

Virtex-7 FPGA Gen3 Integrated Block 的 TAG 管理

Xilinx 7系列FPGA PCIe Gen3的應用接口及特性

Xilinx 7系列FPGA PCIe Gen3的應用接口及特性

評論