昨天在朋友圈刷到這張圖,一看好有意思。

就針對這張圖,我們邊學半導體設(shè)備專用單詞邊科普工藝。

感謝咔嚓,晶媛,維族女婿,老楊,關(guān)老師(半導體綜研),天天改簡歷的河哥,又帥又颯的八妹,以及“愛芯片,愛生活,賺大錢”神仙大佬群友的給與的行業(yè)專業(yè)知識支持。

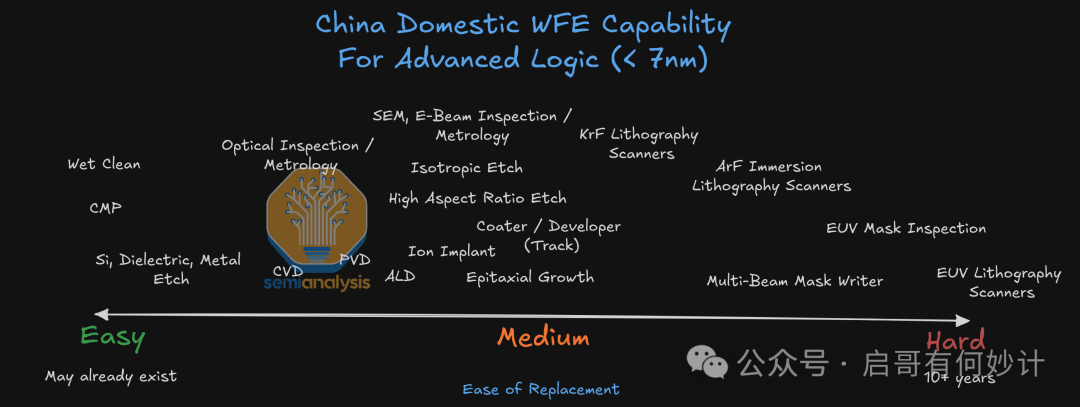

這張圖是一個外媒做,標題是China Domestic WFE Capability For Advanced Logic (7nm)

這段英文對各位評論區(qū)人均英語專八的大佬而言,不難理解,中國國內(nèi)先進邏輯的能力,關(guān)鍵是這個WFE是啥意思?

這是一個縮寫詞,意思是前道工藝設(shè)備。

所以這標題的含義是說中國國內(nèi)N7前道能力到什么水準了?

下面有一個橫軸,這個意思也很明確。

容易做的May already exist(可能已經(jīng)存在)感覺把May這個詞放上去是對中國設(shè)備公司的這么多年下來努力的不信任,呵呵,可能個鬼啊!

中等的Ease of Replacement(容易更換的)和困難的(需要十年以上積累的)。

在容易的領(lǐng)域里,列舉了Wet Clean,CMP,Si/Dielectric/Metal Etch等。

我們一個一個說下,附帶啟哥的對行業(yè)認知。

簡單到中等

Wet Clean,就是濕法清洗設(shè)備,比如ACMR,PNC的主業(yè),甚至那烏拉也有一部分的業(yè)務涉及濕法領(lǐng)域,它是收購北美的Akrion公司來的。

此外Wet 還有濕法刻蝕(Wet Etch),但是這個在12英寸前道工藝里面極其罕見,不過在小尺寸上還有一些應用,此外封裝行業(yè)目前用不少。

清洗業(yè)務在半導體工藝中很頻繁,幾乎每做幾道工藝之后就要清洗,確保送入下一道工藝中,wafer 是絕對清潔的,沒有任何污染物的。

濕法工藝針對不同的工藝也分很多種,比如常見的光刻膠剝離與清洗,CMP后清洗,刻蝕后清洗,沉積后清洗,離子注入后的去厚膠等等。

當然實現(xiàn)的工藝手段和方法也很多,用化學溶液浸泡+超聲波清洗的比較常見,12英寸單片上還有更多種方法的組合手段,來達到清洗目的。

濕法設(shè)備相對而言工藝比較簡單,所以國產(chǎn)化程度非常高,和CMP并稱最容易突破的前道工藝,特別是普通小尺寸別說了,12英寸的單片式都有突破。

CMP,叫化學機械拋光,也就是海哥的主業(yè),除此之外就是45所,一個主打12英寸, 一個主打8英寸, 可惜之前45所上市公司主體晶亦晶微因為某些原因,終止了IPO進程。

目前在這個領(lǐng)域也和濕法設(shè)備一樣國產(chǎn)率超過50%以上,早早實現(xiàn)了國產(chǎn)替代!

為國產(chǎn)設(shè)備點贊!

Si/Dielectric/MetelEtch:這里作者例舉了三種刻蝕對象,分別是硅,介質(zhì)和金屬。

感覺這里說的不是很準確,硅刻蝕要看是啥,如果是最下面的M0-M1層的晶硅與多晶硅刻蝕,依然是非常難的工藝設(shè)備,歸為Easy我個人感覺不是很妥。

金屬與硅多用ICP刻蝕設(shè)備,叫電感耦合刻蝕,那烏拉這塊做的好一些,艾麥可也有,今天直播間有人問起魯汶,巧了,他們當初起家的設(shè)備就是金屬刻蝕。

Dielectric是介質(zhì)層的意思,主要是就是SiO2,Si3N4,這兩種介質(zhì)層,此外要硬算,包括Low-k,High-K,AL2O3也能算。

氧化硅和氮化硅這種刻蝕設(shè)備需要用CCP刻蝕,叫電容耦合刻蝕,這塊就是艾麥可的強項了。

所以同樣是刻蝕設(shè)備,你看不同對象工藝區(qū)別很大!

目前硅與金屬大概占刻蝕總量的60%左右,剩下的40%是介質(zhì)層的刻蝕。

在簡單和中等之間又列舉了幾種設(shè)備,分別是CVD,PVD,Optical Inspection/Metrology。

CVD,叫化學氣相沉積,實際上這是一個大類,這里面各種各樣的設(shè)備實在太多了,包括APCVD(常壓CVD),LPCVD(低壓CVD),SACVD(次常壓),HDPCVD(高密度等離子CVD),PECVD(等離子增強型CVD),MOCVD(金屬有機源CVD)等等。

其中LPCVD常見沉積鎢,高溫氧化膜,多晶硅膜,以及氮化硅膜等;

APCVD常見氧化硅膜,氮化物膜,有機膜等等;

SACVD常見快速填孔比如鎢填孔等等;

PECVD常見,有機膜,氧化硅膜,非晶硅膜等等;

HDPCVD高密度等離子型常見SiO2,其他氧化膜等等;

有人問了好像SiO2,Si3N4在內(nèi)的二氧化硅,氮化硅膜的工藝這么這么多,這不都一樣嗎?這具體看沉薄膜的厚度,質(zhì)量,以及形貌,雖然都是沉膜,還是有一些區(qū)別的。

PVD叫物理氣相沉積,包裹了磁控(Magnetron)和離子束(Ion Beam),以及RF射頻等技術(shù)路線,實際上PVD有將近十種不同的技術(shù)路線。

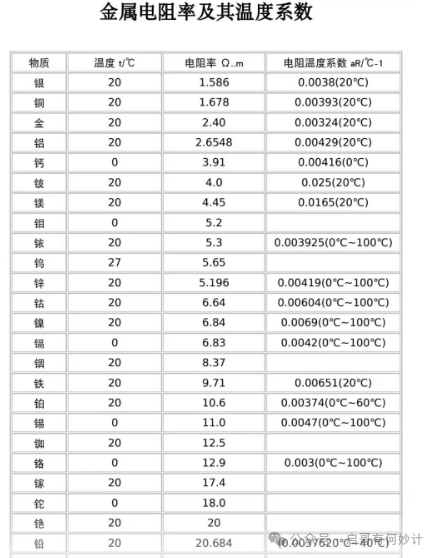

PVD最常見的蒸發(fā)型和濺射型,主要就是各種金屬膜,比如鋁AL,銅Cu,鎢W等。

少部分的錳,釕,鈷,鉍,鉬等金屬也會用PVD,但是主要看工藝和機理結(jié)合。

這里,群里某超級大佬,給我科普的長長一段,我一定要拿出來跟大家分享。(杭所你學著點!)

在10nm節(jié)點以下,銅會遇到一系列問題,比如會發(fā)生電阻突增的問題,而且銅是僅次于銀的電子遷移率第二高的金屬材料。

所以銅特別容易跑出去,跑出去就意味著要漏電,那發(fā)熱量就會大增,這就是巨大的災難。

因此業(yè)內(nèi)想到用銅混著其他金屬材料一起用,然后再用一堆barrier layer 阻擋,這樣整個金屬會變很多層,電阻率又上去了,而且這些孔和溝槽也不好填,因為都是各種各樣的垃圾塞里面,銅想進也進不去,這問題煩透了。

上面提到的錳(Mn),釕(Ru),鈷(Co),鉍(Bi),鉬(Mo),只有鈷和釕可以放在Low Metel層上,鈷和鎢可以用在中段,而錳只能在High Metel層上。

什么intel用鈷,TSMC用鉍,都是說說的,實際上并沒有多大用處。

如果不用barrier和seed層,自然最好,但是對工藝挑戰(zhàn)很大,容易出一堆問題,填了又會搞廢電阻率,屬于兩邊騎虎難下的,非常頭疼。

實際上我并沒有完全吃透這些基本道理,但是大佬說什么是什么。

總之PVD主要以沉積金屬為主,因為很多金屬不能被氧化,所以不能用CVD(這是又帥又颯的八妹跟我說的)。

總而言之,我也不太懂,只能東問西問。

當然了PVD在面板行業(yè)以及光伏行業(yè)也是非常重要的沉膜設(shè)備,面板叫真空蒸鍍型。

國內(nèi)干這個基本也就那烏拉了,整個PVD占了10%-15%的設(shè)備總量。

Optical Inspection/Metrology叫光學檢測/計量設(shè)備。

檢測計量這又是一個大類,它包括了。

表面缺陷(Surface),缺陷(Defect),三維圖形(3D),污染物檢測(Contamination),應力(Stress),電學參數(shù)(Parameter)等等,這些叫檢測(Inspection);

關(guān)鍵尺寸(CD-SEM),套刻精度(Overlay),膜厚(Film),幾何圖形(Geometry),注入量(Implant Metrology),缺陷SEM(Defect Review SEM)這些叫計量設(shè)備(Metrology)。

這個作者歸為容易到中等中間,我覺得有點高估了咱們水平,這塊前道量檢測設(shè)備,是除了光刻機之外前道工藝設(shè)備里國產(chǎn)化比例最低的一塊,當然這個賽道上的創(chuàng)業(yè)玩家也非常多,關(guān)老師一統(tǒng)計國內(nèi)幾十家………………

不過大多擠在普通光學,膜厚,電子束,套刻方向上,和KLA,應材,日立等國外龍頭差距巨大。

國內(nèi)五大家,上海精測,飛測,睿勵,東方晶源和御微,算這個行業(yè)的龍頭公司,當然這些公司的業(yè)務有不同的側(cè)重點,并不是全做了,就看誰能脫穎而出!

期待,國產(chǎn)量測設(shè)備的大突破。

中等難度

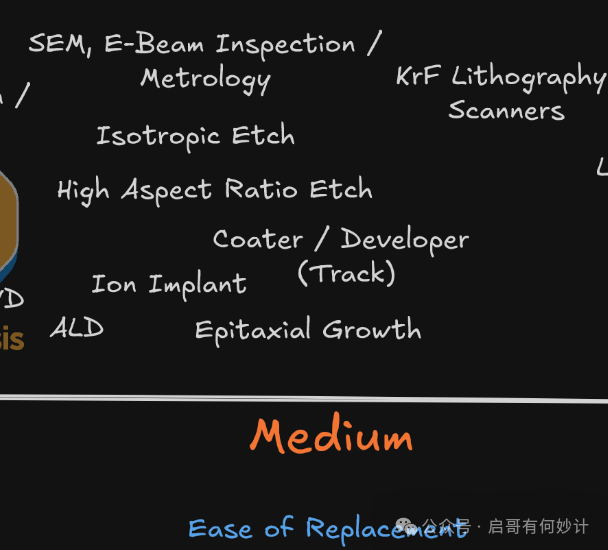

然后中等難度下就更多了,作者列舉了。

SEM,E-BeamInspection/Metrology;Isotropic Etch,HighAspectRatio Etch;Coator/Developer (Track); IonImplant EpitaxialGrowth,ALD,以及KrF Lithography Scanners等。

SEM,E-BeamInspection/Metrology,電子束檢測設(shè)備,這個前面講檢測行業(yè)說過了就不說了。

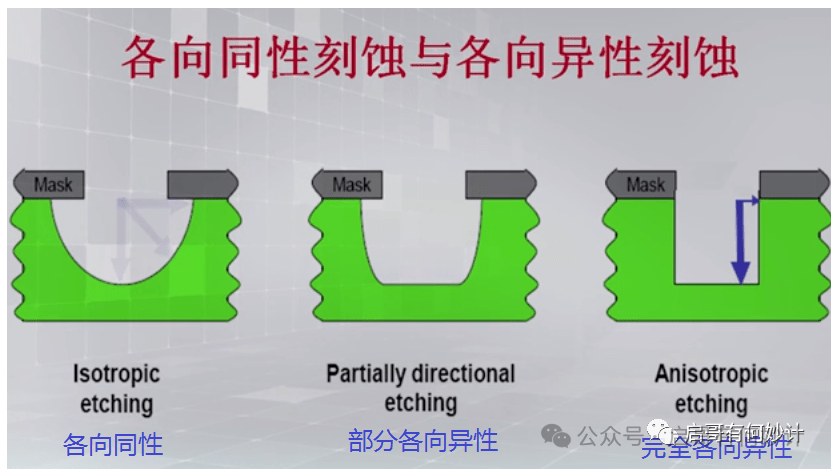

Isotropic Etch,叫各向同性刻蝕,我屬于萬萬沒想到,作者居然把這種工藝分這么細,這東西在DRAM制程上挺多的,這個也叫高選擇比刻蝕。

在各向異性/同性刻蝕,是指刻蝕沿著不同晶硅格方向,同性刻蝕,可以理解往橫軸方向了,各項異性是往垂直方向。

這些東西特別是在存儲制程上特別常見。

然后加下來,HighAspectRatio Etch,高縱橫比刻蝕,也就是高深寬比刻蝕。

這個在NAND上打深孔常見刻蝕工藝,什么1:40,1:60,就是指這些,之前市場火爆關(guān)注艾麥可進Y家的預期,好像也是這個原因。

所以這個作者把存儲上用的常見兩大刻蝕制程,高選擇比和高深寬比給你們分這么細,我是真沒想到,看來老外也是非常關(guān)注,國內(nèi)存儲廠的國產(chǎn)設(shè)備進度。

當然國內(nèi)包括那烏拉,艾麥可,以及維族女婿他們公司這個領(lǐng)域三家比較強。

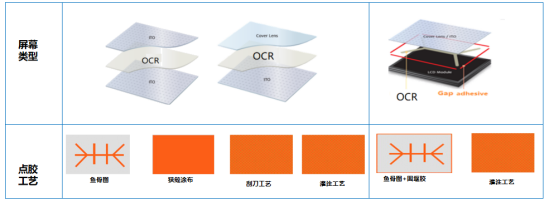

Coator/Developer (Track),這個就是涂膠顯影,國內(nèi)有且只有一家大哥,就是葬的好。

借用咔嚓的原話,Track 這東西看似簡單,但是這么多年了,國內(nèi)似乎也沒第二家說自己做的特別好,看來,這東西里面還有很多門道。

大家可以理解成Track 設(shè)備會針對不同的光刻膠性能參數(shù)做微調(diào),實際上屬于半定制設(shè)備。

所以這東西還是需要很深的積累,是需要和客戶FAB那端反復磨出來的!

IonImplant,就是離子注入機,這個沒啥好說的,國內(nèi)基本就是凱世通與48的中科信。

離子注入機,主要就是高束流(High Current),中束流(Medium Current),高能量(High Energy),低能量(Low Energy)等,此外在碳化硅行業(yè)有個很特殊的叫高溫離子注入(High Temperature)。

不過我想說的是離子注入這個東西在這個半導體設(shè)備行業(yè)屬于幾乎沒有增長的那部分,目前僅僅只占了3%-4%左右,還不如濕法和CMP的行業(yè)規(guī)模大。

深入其原因,第一是離子注入的工藝比較少,一個FAB也用不了多少臺,不算產(chǎn)能瓶頸設(shè)備,第二是現(xiàn)在有其他工藝能替代離子注入的摻雜,特別是在存儲制程上,所以就挺尷尬的。

EpitaxialGrowth,就是長外延設(shè)備,這里應該主要是指硅的外延設(shè)備, 常見就是外延爐,這東西小尺寸硅外延爐早國產(chǎn)化了,12英寸的硅外延設(shè)備也不難。

難點是啥?特殊的外延設(shè)備,比如鍺硅外延,這東西應材賣5000多萬人民幣一臺,各位就知道這東西有多難了。

好像聽大佬們說“500億”說自己干出來了,也不知道真假。

鍺硅外延常見14nm以下工藝里,是國產(chǎn)設(shè)備急需突破的一大難點!

國內(nèi)工程師們加油!

ALD,這又是一種常見的薄膜沉積類設(shè)備,叫原子層沉積。

然后這個領(lǐng)域又分好多種不同的工藝類型的設(shè)備,比如單片的,爐管的,還有等離子增強型的PEALD。

單片式國外大哥就是ASMi,國內(nèi)就是老三和微導,這種常見沉積HFO2,還有其他High-K材料。

爐管式國外就是KE和TEL,KE就是之前的日立國際電氣,后面美國資本巨頭KKR花了2517億日元從日立手里買下,再經(jīng)過拆分重組運營后變成現(xiàn)在的KE,Kokusai,科意,去年10月再在日本IPO上市。

國內(nèi)就是那烏拉和維族女婿他們做這個。

爐管式對應工藝是TaN 和TiN,TaN和TiN是非常非常重要的緩沖層,包裹在各種金屬線的結(jié)構(gòu)外面,這些都需要爐管式ALD設(shè)備來實現(xiàn)。

前文提到的,除了離子注入做摻雜之外,ALD也能一定程度上起到類似的作用,定向的長薄膜的時候進行摻雜改變其電學參數(shù),所以我說現(xiàn)在離子注入設(shè)備天花板比較低了。

最后一個KrF Lithography Scanners,這個是248nm的光刻機,這個不多說了。

KrF的光刻機,大致對應180-90nm工藝,在8英寸以及早期12英寸工藝上比較常見。

當然了,現(xiàn)在也有改良過后的針對12英寸先進工藝中端金屬層的KrF 光刻機,別說KrF了,還有i-line的12英寸光刻機呢!

佳能:正是在下!

這些作者都歸為有可能替代,也比較中肯,確實國內(nèi)突破很多了。

十年后的詩與遠方!

這里作者列舉了也許我們需要十年甚至更長時間才能突破的半導體設(shè)備技術(shù),包括了:

ArFImmersionLithography Scaners,EUV Mask Inspection,Multi-Beam Mask Writer,EUV Lithography Scanners。

ArFImmersionLithography Scaners,也就是193nm浸沒型光刻機啊,這個就是ASML主流設(shè)備,從45nm節(jié)點開始一直到7nm,主要的光刻工藝用的就是這個。

其實還有個不帶Immersion的,也就是193nm干式光刻機,它對應90-65/55節(jié)點,尼康還在這個領(lǐng)域混口飯吃,每年還出不少貨。

關(guān)于光刻機國產(chǎn)化進度的消息屬于國家機密,我不能多說,只能說有,一直在努力,二正在驗證。

希望早日國產(chǎn)突破!

至于EUV Mask Inspection,EUV掩膜板檢測,Multi-BeamMask Writer多電子束掩膜板寫入設(shè)備(掩膜板光刻機),EUVLithography Scanners,EUV光刻機那是不敢想,真不敢想。

特別是這個Mask Writer,其實國內(nèi)根本就沒人做過,不管是不是EUV的包括DUV的,這東西基本就是尼康一家獨大,貴的有上億美金的!基本和EUV設(shè)備價格沒什么差了!

最后可能作者對半導體設(shè)備并不是很了解,它漏了好多東西。

我給大家再捋捋。

濕法設(shè)備設(shè)備里還有一個大類,雖然都叫濕法但是一般我們把它單獨列出來。

PR Stripper,光刻膠濕法剝離設(shè)備,這個做的不少,比如PNC,那烏拉,ACRM等,高溫硫酸工藝,就是這玩意兒。

Ashing,等離子干法去膠,也叫灰化設(shè)備,之前Mastton,也就是現(xiàn)在屹唐就是干這個的,然后還有韓國的PSK。

之前Ashing沒人做,但是近些年一堆人干這個,特別是在化合物和小尺寸上,現(xiàn)在初創(chuàng)公司多如牛毛,隨便一抓國內(nèi)干這個起碼十多家!

Ashing的去膠和Stripper不太一樣,Ashing更多用在離子注入前的光刻膠的厚膠上,利用等離子技術(shù)快速去厚膠,但是整個工藝不能單獨使用,要結(jié)合Stripper的濕法去膠,因為干法只能去掉80%,剩下20%還得濕法來,才能完全弄干凈。

說句不好聽的,目前把Ashing設(shè)備當主業(yè)的設(shè)備公司屬于把自己路走窄了,因為這個市場體量并不大,隨著做的人原來越多,價格越來越低,根本沒有利潤,必須要想辦法開拓第二主力產(chǎn)品才能活下去。

唉,說說容易做做難,誰不想呢?但是現(xiàn)在窗口期正在過去,各位創(chuàng)業(yè)公司加油吧。

此外還有氧化(Oxidation),包括濕氧(Wet-Oxygen),水汽氧化(Steam),干式氧化(Dry-Oxygen),這個在以前的8英寸工藝上很多,12英寸上比較少見,都不用這個方案了。

那烏拉前身七星好像就是干這個的。

然后還有退火(Annealing),這個又是一個很重要的設(shè)備分支,包括普通的退火,激光退火(Laser Annealing),快退火(RTA),快速熱處理(RTP)等。

激光退火現(xiàn)在碳化硅行業(yè)很火,主要是碳化硅的特性原因,這個RTP也是屹唐的拳頭產(chǎn)品,此外國內(nèi)那烏拉這塊也很多,基本屬于國產(chǎn)化比例不低的領(lǐng)域了。

洋洋灑灑5000多字,雖然字數(shù)不多,但是基本全是精華了,啟哥把我知道的半導體設(shè)備與工藝知識,能搬的全都搬上來了!

在此感謝,“愛芯片,愛生活,賺大錢”的群友們的支持,半夜三更還騷擾他們,他們還耐心給我解釋。

你們給我的打賞,到時候都變?nèi)杭t包發(fā)給他們。

總之,啟哥我知識水平有限,本文肯定還有很多不足之處,望各位大佬指正,虛心學習,評論區(qū)見!

-

半導體

+關(guān)注

關(guān)注

334文章

27010瀏覽量

216301 -

設(shè)備

+關(guān)注

關(guān)注

2文章

4473瀏覽量

70540 -

芯片工藝

+關(guān)注

關(guān)注

0文章

13瀏覽量

7117

發(fā)布評論請先 登錄

相關(guān)推薦

SMT貼片貼裝工藝流程 SMT貼片焊接技術(shù)解析

【書籍評測活動NO.50】親歷芯片產(chǎn)線,輕松圖解芯片制造,揭秘芯片工廠的秘密

esp32上使用chatGPT做一些有意思的事情

科普EEPROM 科普 EVASH Ultra EEPROM?科普存儲芯片

引線框架貼膜工藝在QFN封裝制程中的應用

榮耀終端榮獲“貼膜設(shè)備與貼膜方法”專利

昨天看到消息Altera從Intel獨立出來了,不知道大家常用的FPGA是什么?

SMT是什么工藝 smt有幾種貼裝工藝

基于全志D1s實現(xiàn)智能家居中控虛擬光渲交互

這圖特別有意思,芯片工藝與設(shè)備的大型科普貼,我知道的全搬上來了!

這圖特別有意思,芯片工藝與設(shè)備的大型科普貼,我知道的全搬上來了!

評論