安信可技術論壇官方B站賬號來啦

提前關注不迷路

在這里優先預告各類活動、教程

以下作品由安信可社區用戶

一只呆頭鵝制作

實驗目的

使用安信可科技的 GP-01 模塊實現衛星授時,顯示在數碼管上。

程序設計思路

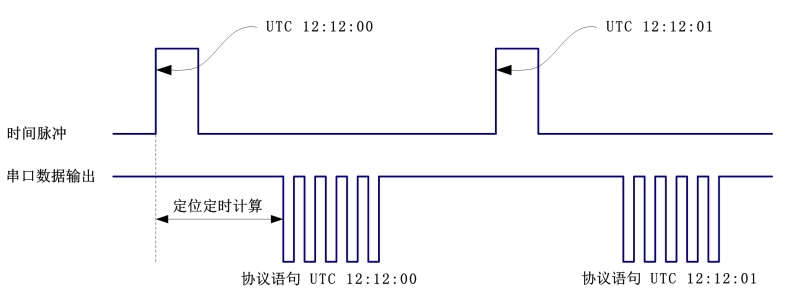

GP01 模塊有 24 個接口,寫代碼的時候只需要關注 TX 引腳,GP-01 模塊獲得的數據送到 FPGA,使用狀態機獲取我們想要的年月日、實時時間。此時得到的時間是 UTC 時間,并不是我們想要的北京時間,我們只需要在小時上加八,然后就把數據傳到數碼管顯示就可以了。

代碼

串口接收模塊

把 GP01 的單比特數據轉換成八比特的數據。

module uart_rx

#(

parameter UART_BPS = 'd9600, //串口波特率

parameter CLK_FREQ = 'd50_000_000 //時鐘頻率

)

(

input wire sys_clk , //系統時鐘50MHz

input wire sys_rst_n , //全局復位

input wire rx , //串口接收數據

output reg [7:0] po_data , //串轉并后的8bit數據

output reg po_flag //串轉并后的數據有效標志信號

);

//********************************************************************//

//****************** Parameter and Internal Signal *******************//

//********************************************************************//

//localparam define

localparam BAUD_CNT_MAX = CLK_FREQ/UART_BPS ;

//reg define

reg rx_reg1 ;

reg rx_reg2 ;

reg rx_reg3 ;

reg start_nedge ;

reg work_en ;

reg [12:0] baud_cnt ;

reg bit_flag ;

reg [3:0] bit_cnt ;

reg [7:0] rx_data ;

reg rx_flag ;

//********************************************************************//

//***************************** Main Code ****************************//

//********************************************************************//

//插入兩級寄存器進行數據同步,用來消除亞穩態

//rx_reg1:第一級寄存器,寄存器空閑狀態復位為1

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

rx_reg1 <= 1'b1;

else

rx_reg1 <= rx;

//rx_reg2:第二級寄存器,寄存器空閑狀態復位為1

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

rx_reg2 <= 1'b1;

else

rx_reg2 <= rx_reg1;

//rx_reg3:第三級寄存器和第二級寄存器共同構成下降沿檢測

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

rx_reg3 <= 1'b1;

else

rx_reg3 <= rx_reg2;

//start_nedge:檢測到下降沿時start_nedge產生一個時鐘的高電平

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

start_nedge <= 1'b0;

else if((~rx_reg2) && (rx_reg3))

start_nedge <= 1'b1;

else

start_nedge <= 1'b0;

//work_en:接收數據工作使能信號

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

work_en <= 1'b0;

else if(start_nedge == 1'b1)

work_en <= 1'b1;

else if((bit_cnt == 4'd8) && (bit_flag == 1'b1))

work_en <= 1'b0;

//baud_cnt:波特率計數器計數,從0計數到BAUD_CNT_MAX - 1

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

baud_cnt <= 13'b0;

else if((baud_cnt == BAUD_CNT_MAX - 1) || (work_en == 1'b0))

baud_cnt <= 13'b0;

else if(work_en == 1'b1)

baud_cnt <= baud_cnt + 1'b1;

//bit_flag:當baud_cnt計數器計數到中間數時采樣的數據最穩定,

//此時拉高一個標志信號表示數據可以被取走

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

bit_flag <= 1'b0;

else if(baud_cnt == BAUD_CNT_MAX/2 - 1)

bit_flag <= 1'b1;

else

bit_flag <= 1'b0;

//bit_cnt:有效數據個數計數器,當8個有效數據(不含起始位和停止位)

//都接收完成后計數器清零

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

bit_cnt <= 4'b0;

else if((bit_cnt == 4'd8) && (bit_flag == 1'b1))

bit_cnt <= 4'b0;

else if(bit_flag ==1'b1)

bit_cnt <= bit_cnt + 1'b1;

//rx_data:輸入數據進行移位

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

rx_data <= 8'b0;

else if((bit_cnt >= 4'd1)&&(bit_cnt <= 4'd8)&&(bit_flag == 1'b1))

rx_data <= {rx_reg3, rx_data[7:1]};

//rx_flag:輸入數據移位完成時rx_flag拉高一個時鐘的高電平

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

rx_flag <= 1'b0;

else if((bit_cnt == 4'd8) && (bit_flag == 1'b1))

rx_flag <= 1'b1;

else

rx_flag <= 1'b0;

//po_data:輸出完整的8位有效數據

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

po_data <= 8'b0;

else if(rx_flag == 1'b1)

po_data <= rx_data;

//po_flag:輸出數據有效標志(比rx_flag延后一個時鐘周期,為了和po_data同步)

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

po_flag <= 1'b0;

else

po_flag <= rx_flag;

endmodule

獲取日歷、時間模塊

因為 GP01 模塊獲取的數據不光只有日歷和時間數據,所以需要用一個狀態機來判斷接收到的數據是不是日歷、時間數據。

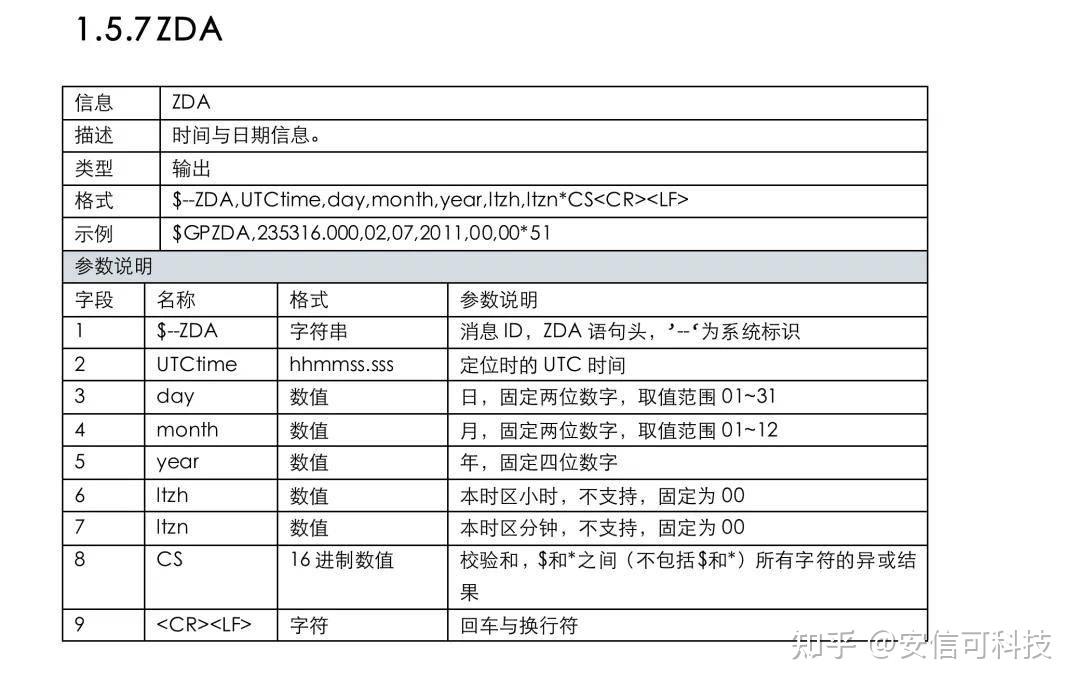

EMEA 協議中的時間與日歷信息格式如圖所示:

module Data_processing (

input wire sys_clk ,

input wire sys_rst_n ,

input wire uart_recv_done,

input wire [7:0] uart_recv_data,

output reg [31:0] time_data ,

output reg [31:0] calendar_data ,

output reg led3 ,

output reg led2 ,

output reg led

);

reg [8:0] state ;

reg [31:0] time_data_temp;

reg [31:0] calendar_temp ;

wire [7:0] recv_time ;

wire [7:0] recv_calendar ;

parameter WATI = 9'b0000_0000_0;

parameter IDLE = 9'b0000_0000_1;

parameter ONE = 9'b0000_0001_0;

parameter TWO = 9'b0000_0010_0;

parameter THREE= 9'b0000_0100_0;

parameter FOUR = 9'b0000_1000_0;

parameter FIVE = 9'b0001_0000_0;

parameter SIX = 9'b0010_0000_0;

parameter SIX_1 = 9'b0010_0000_1;

parameter SIX_2 = 9'b0010_0001_0;

parameter SIX_3 = 9'b0010_0001_1;

parameter SIX_4 = 9'b0010_0010_0;

parameter SIX_5 = 9'b0010_0010_1;

parameter SIX_6 = 9'b0010_0011_0;

parameter SIX_7 = 9'b0010_0011_1;

parameter SIX_8 = 9'b0010_0100_0;

parameter SIX_9 = 9'b0010_0100_1;

parameter SEVEN = 9'b0100_0000_0;

parameter SEVEN_1 = 9'b0100_0000_1;

parameter SEVEN_2 = 9'b0100_0001_0;

parameter SEVEN_3 = 9'b0100_0001_1;

parameter SEVEN_4 = 9'b0100_0010_0;

parameter SEVEN_5 = 9'b0100_0010_1;

parameter SEVEN_6 = 9'b0100_0011_0;

parameter SEVEN_7 = 9'b0100_0011_1;

parameter SEVEN_8 = 9'b0100_0100_0;

parameter SEVEN_9 = 9'b0100_0100_1;

parameter SEVEN_10 = 9'b0100_1001_0;

parameter EIGHT= 9'b1000_0000_0 ;

parameter TEN = 9'b1000_0000_1 ;

parameter CNT_MAX = 23'd7_500_000 ;

assign recv_time = uart_recv_data - 8'd48; //ascll碼 0-9

assign recv_calendar = uart_recv_data - 8'd48;

always @(posedge sys_clk or negedge sys_rst_n) begin //這里的狀態機用來接收日歷和時間

if (sys_rst_n == 1'b0) begin

state <= WATI;

end

else if( uart_recv_done == 1'd1) begin

case (state)

WATI : begin

if ((uart_recv_data == 8'h24)) state <= IDLE ; else if ((uart_recv_data == 8'h47) ) state <= ONE; else state <= WATI; //固定格式 $GPZDA,

end

IDLE : state <= ((uart_recv_data == 8'h47)) ? ONE : WATI;

ONE : state <= ((uart_recv_data == 8'h4E)) ? TWO : WATI;

TWO : state <= ((uart_recv_data == 8'h5A)) ? THREE : WATI;

THREE : state <= ((uart_recv_data == 8'h44)) ? FOUR : WATI;

FOUR : state <= ((uart_recv_data == 8'h41)) ? FIVE : WATI;

FIVE : state <= ((uart_recv_data == 8'h2C)) ? SIX : WATI;

SIX : state <= ((uart_recv_data != 8'h2C)) ? SIX_1 : WATI; //時間 //

SIX_1 : state <= ((uart_recv_data != 8'h2C)) ? SIX_2 : WATI;

SIX_2 : state <= ((uart_recv_data != 8'h2C)) ? SIX_3 : WATI;

SIX_3 : state <= ((uart_recv_data != 8'h2C)) ? SIX_4 : WATI;

SIX_4 : state <= ((uart_recv_data != 8'h2C)) ? SIX_5 : WATI;

SIX_5 : state <= ((uart_recv_data != 8'h2C)) ? SIX_6 : WATI;

SIX_6 : state <= ((uart_recv_data == 8'h2E)) ? SIX_7 : WATI; //.

SIX_7 : state <= ((uart_recv_data == 8'h30)) ? SIX_8 : WATI; //000

SIX_8 : state <= ((uart_recv_data == 8'h30)) ? SIX_9 : WATI;

SIX_9 : state <= ((uart_recv_data == 8'h30)) ? SEVEN : WATI;

SEVEN : state <= ((uart_recv_data == 8'h2C) ) ? SEVEN_1 : WATI; //,

SEVEN_1 : state <= ((uart_recv_data != 8'h2C) ) ? SEVEN_2 : WATI; //日

SEVEN_2 : state <= ((uart_recv_data != 8'h2C) ) ? SEVEN_3 : WATI;

SEVEN_3 : state <= ((uart_recv_data == 8'h2C) ) ? SEVEN_4 : WATI;

SEVEN_4 : state <= ((uart_recv_data != 8'h2C) ) ? SEVEN_5 : WATI; //月

SEVEN_5 : state <= ((uart_recv_data != 8'h2C) ) ? SEVEN_6 : WATI;

SEVEN_6 : state <= ((uart_recv_data == 8'h2C) ) ? SEVEN_7 : WATI;

SEVEN_7 : state <= ((uart_recv_data != 8'h2C) ) ? SEVEN_8 : WATI; //年

SEVEN_8 : state <= ((uart_recv_data != 8'h2C) ) ? SEVEN_9 : WATI;

SEVEN_9 : state <= ((uart_recv_data != 8'h2C) ) ? SEVEN_10 : WATI;

SEVEN_10 : state <= ((uart_recv_data != 8'h2C) ) ? EIGHT : WATI;

EIGHT : state <= ((uart_recv_data == 8'h2C) ) ? TEN : WATI;

TEN : state <= ((uart_recv_data == 8'h30) ) ? WATI : WATI;

default: state <= WATI;

endcase

end

end

always @(posedge sys_clk or negedge sys_rst_n) begin

if (sys_rst_n == 1'b0) begin

led <= 1'b0;

end

else if((state == FIVE) && (uart_recv_done == 1'b1))

led <= ~led;

else

led <= led;

end

always @(posedge sys_clk or negedge sys_rst_n) begin

if (sys_rst_n == 1'b0) begin

led2 <= 1'b0;

end

else if((state == SEVEN) && (uart_recv_done == 1'b1))

led2 <= ~led2;

else

led2 <= led2;

end

always @(posedge sys_clk or negedge sys_rst_n) begin

if (sys_rst_n == 1'b0) begin

led3 <= 1'b0;

end

else if((state == EIGHT) && (uart_recv_done == 1'b1))

led3 <= ~led3;

else

led3 <= led3;

end

always @(posedge sys_clk or negedge sys_rst_n) begin //

if (sys_rst_n == 1'b0)

time_data_temp <= 32'b0;

else if(state == SIX )

time_data_temp <= {recv_time[3:0],time_data_temp[27:0]};

else if(state == SIX_1 )

time_data_temp <= {time_data_temp[31:28],recv_time[3:0],time_data_temp[23:0]};

else if(state == SIX_2 )

time_data_temp <= {time_data_temp[31:20],recv_time[3:0],time_data_temp[15:0]};

else if(state == SIX_3 )

time_data_temp <= {time_data_temp[31:16],recv_time[3:0],time_data_temp[11:0]};

else if(state == SIX_4 )

time_data_temp <= {time_data_temp[31:8],recv_time[3:0],time_data_temp[3:0]};

else if(state == SIX_5 )

time_data_temp <= {time_data_temp[31:4],recv_time[3:0]};

else

time_data_temp <= {time_data_temp[31:24],4'd10,time_data_temp[19:12],4'd10,time_data_temp[7:0]};

end

always @(posedge sys_clk or negedge sys_rst_n) begin

if (sys_rst_n == 1'b0)

calendar_temp <= 32'd0;

else if(state == SEVEN_1)

calendar_temp <= {calendar_temp[31:8],recv_calendar[3:0],calendar_temp[3:0]};

else if(state == SEVEN_2)

calendar_temp <= {calendar_temp[31:4],recv_calendar[3:0]};

else if(state == SEVEN_4)

calendar_temp <= {calendar_temp[31:16],recv_calendar[3:0],calendar_temp[11:0]};

else if(state == SEVEN_5)

calendar_temp <= {calendar_temp[31:12],recv_calendar[3:0],calendar_temp[7:0]};

else if(state == SEVEN_7)

calendar_temp <= {recv_calendar[3:0],calendar_temp[27:0]};

else if(state == SEVEN_8)

calendar_temp <= {calendar_temp[31:28],recv_calendar[3:0],calendar_temp[23:0]};

else if(state == SEVEN_9)

calendar_temp <= {calendar_temp[31:24],recv_calendar[3:0],calendar_temp[19:0]};

else if(state == SEVEN_10)

calendar_temp <= {calendar_temp[31:20],recv_calendar[3:0],calendar_temp[15:0]};

end

always @(posedge sys_clk or negedge sys_rst_n) begin

if (sys_rst_n == 1'b0) begin

calendar_data <= 32'b0;

end

else if((state == TEN) && (uart_recv_done == 1'b1) )

calendar_data <= calendar_temp;

else

calendar_data <= calendar_data;

end

always @(posedge sys_clk or negedge sys_rst_n) begin

if (sys_rst_n == 1'b0) begin

time_data <= 32'b0;

end

else if((state == SEVEN) && (uart_recv_done == 1'b1) )

time_data <= time_data_temp;

else

time_data <= time_data;

end

endmodule //Data_processing

UTC 處理模塊

這里是將 UTC 時間轉換成北京時間,日歷與時間每隔五秒切換一次。

module display (

input wire sys_clk ,

input wire sys_rst_n ,

input wire [31:0] time_data ,

input wire [31:0] calendar_data ,

output wire [31:0] display_data

);

localparam COUNT_MAX = 50_000_000 ;

localparam CNT_10S_MAX = 6'd5 ;

reg [26:0] count ;

reg [3:0] cnt_500ms ;

reg display_flag ;

reg [31:0] time_data_temp ;

always @(posedge sys_clk or negedge sys_rst_n) begin

if (sys_rst_n == 1'b0) begin

count <= 0;

end else begin

if (count == COUNT_MAX - 1) begin

count <= 0;

end

else begin

count <= count + 27'd1;

end

end

end

always @(posedge sys_clk or negedge sys_rst_n) begin

if (sys_rst_n == 1'b0) begin

time_data_temp <= 32'd0;

end

else if (display_flag == 1'd1 && ((time_data[27:24] + 4'd8) >= 4'd10 ))begin //因為獲取的時間是UTC時間轉換成北京時間加上八就可以了

time_data_temp[31:28] <= time_data[31:28] + 4'd1;

time_data_temp[27:24] <= (time_data[27:24] + 4'd8) % 4'd10;

end

else if (display_flag == 1'd1 && time_data[27:24] + 4'd8 < 4'd10 )begin

time_data_temp[31:28] <= time_data[31:28];

time_data_temp[27:24] <= time_data[27:24]+ 4'd8;

end

else

time_data_temp <= {time_data_temp[31:24],time_data[23:0]};

end

always @(posedge sys_clk or negedge sys_rst_n) begin

if (sys_rst_n == 1'b0) begin

cnt_500ms <= 4'd0;

end

else if (cnt_500ms == CNT_10S_MAX) //5S

cnt_500ms <= 4'd0;

else if (count == COUNT_MAX - 1)

cnt_500ms <= cnt_500ms + 4'd1;

end

always @(posedge sys_clk or negedge sys_rst_n) begin

if (sys_rst_n == 1'b0) begin

display_flag <= 1'd0;

end

else if (cnt_500ms == CNT_10S_MAX) begin

display_flag <= ~display_flag;

end

else

display_flag <= display_flag;

end

assign display_data = display_flag ? calendar_data :time_data_temp;

endmodule //display

數碼管顯示模塊

module smg (

input wire sys_clk ,

input wire sys_rst_n ,

input wire [31:0] smg_seg_in ,

output reg [7:0] smg_sel ,

output reg [7:0] smg_seg

);

localparam CNT_1MS_MAX = 16'd50_000 ;

reg [15:0] cnt_1ms ;

reg [3:0] flag_1ms ;

reg [3:0] data_disp ;

always @(posedge sys_clk or negedge sys_rst_n) begin

if(sys_rst_n==1'b0)

cnt_1ms<=16'b0;

else if (cnt_1ms==CNT_1MS_MAX-1)

cnt_1ms<=16'b0;

else

cnt_1ms<=cnt_1ms+16'b1;

end

always @(posedge sys_clk or negedge sys_rst_n) begin

if(sys_rst_n==1'b0)

flag_1ms<=4'b0;

else if ((cnt_1ms==CNT_1MS_MAX-1)&&(flag_1ms==7))

flag_1ms<=4'b0;

else if (cnt_1ms==CNT_1MS_MAX-1)

flag_1ms<=flag_1ms+4'b1;

else

flag_1ms<=flag_1ms;

end

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

data_disp <= 4'b0;

else case(flag_1ms)

4'd0: data_disp <= smg_seg_in[3:0] ;

4'd1: data_disp <= smg_seg_in[7:4] ;

4'd2: data_disp <= smg_seg_in[11:8] ;

4'd3: data_disp <= smg_seg_in[15:12];

4'd4: data_disp <= smg_seg_in[19:16];

4'd5: data_disp <= smg_seg_in[23:20];

4'd6: data_disp <= smg_seg_in[27:24];

4'd7: data_disp <= smg_seg_in[31:28];

default:data_disp <= 4'b0 ;

endcase

always @(posedge sys_clk or negedge sys_rst_n) begin

if(sys_rst_n ==1'b0)

smg_sel<=8'b1111_1110;

else case (flag_1ms)

0: smg_sel<=~8'b1111_1110;

1: smg_sel<=~8'b1111_1101;

2: smg_sel<=~8'b1111_1011;

3: smg_sel<=~8'b1111_0111;

4: smg_sel<=~8'b1110_1111;

5: smg_sel<=~8'b1101_1111;

6: smg_sel<=~8'b1011_1111;

7: smg_sel<=~8'b0111_1111;

default:smg_sel<=8'b1111_1110;

endcase

end

always @(posedge sys_clk or negedge sys_rst_n) begin

if(sys_rst_n ==1'b0)

smg_seg<=8'b1111_1100;

else case (data_disp)

1: smg_seg<=~8'b0110_0000;

2: smg_seg<=~8'b1101_1010;

3: smg_seg<=~8'b1111_0010;

4: smg_seg<=~8'b0110_0110;

5: smg_seg<=~8'b1011_0110;

6: smg_seg<=~8'b1011_1110;

7: smg_seg<=~8'b1110_0000;

8: smg_seg<=~8'b1111_1110;

9: smg_seg<=~8'b1111_0110;

0: smg_seg<=~8'b1111_1100;

10:smg_seg<=~8'b0000000001;

default:smg_seg<=8'b1111_1100;

endcase

end

endmodule //smg

視頻演示

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602004 -

gps

+關注

關注

22文章

2886瀏覽量

166054 -

DIY

+關注

關注

176文章

886瀏覽量

348281

發布評論請先 登錄

相關推薦

wifi授時電子鐘如何對時間

AT3340:可替換國外授時板,BDS/GPS雙模授時板規格書

AT3340:支持BDS/GPS雙模授時板datasheet

通信基站授時常用定位授時模塊對比:ATGM332D-5T和ATGM331C-5T-發燒友

衛星授時安全隔離防護裝置施工方案

同步時鐘:北斗/GPS衛星、電信基站、NTP以太網校時方式的區別

stm32f051r8中RTC日歷時鐘如何將年月日時分秒轉換成秒計數?

同步時鐘:北斗/GPS衛星、電信基站、NTP以太網等多種校時方式的區別

電子DIY作品 基于FPGA的GPS授時日歷時鐘

電子DIY作品 基于FPGA的GPS授時日歷時鐘

評論