伴隨大語言模型和相關訓練系統迅猛增長、對非結構化數據處理的需求急劇上升,市場對算力的需求也是呈指數級增加。PCIe作為計算機和服務器中使用廣泛的高速數據傳輸技術發展迅猛,今年4月份PCI-SIG已經批準 Draft 0.5版基礎規范,目前0.7版本基礎規范正在審核中,預計2025年敲定最終發行版本。

PCIe 7.0 規范包括以下功能目標:

通過 x16 配置提供 128 GT/s 原始比特率和高達 512 GB/s 的雙向比特率。

利用 PAM4信令, 以實現更高效的信號傳輸和更高的數據吞吐量。

關注通道參數和覆蓋面, 以優化數據傳輸的質量和距離。

持續實現低時延和高可靠性的目標。

提高電源效率。

保持與所有前幾代 PCIe 技術的向后兼容性。

傳輸技術的挑戰

PCIe技術歷經Gen1-Gen6,已經發展到單 Lane 128G的傳輸速率,超高速的傳輸速率帶來了巨大挑戰,協會不得不加入越來越多、越來越復雜的輔助機制,控制信號和數據完整性。那么,今天我們將主要探討未來PCIe 7.0光傳輸技術的必要性及其挑戰。

1計算資源限制

面向超大集群、超輕邊緣的兩極分化的數據中心新場景,未來計算將突破馮諾依曼架構瓶頸,計算、存儲和通信等模塊通過統一總線對等互聯,而PCIe作為數據中心服務器間互聯的主力,承擔著高速數據傳輸的重任。數據中心中的計算密集型任務,對內存帶寬和利用率提出了更高要求。當前,大部分數據中心仍依賴本地內存,這不僅限制了數據處理的速度,還導致內存資源的利用效率低下。光傳輸方案則可以實現計算資源實現分散化,通過使處理單元能夠訪問更多分布在不同服務器單元或機架中的內存單元(跨服務器,跨機架訪問),進而釋放高度本地化且經常未使用的本地內存,使數據中心能夠更高效地配置資源。

2電信號傳輸距離受限

大語言模型的快速迭代離不開海量GPU集群的強勁支持。目前而言,這個海量已經來到了千卡萬卡級別,集群之間的互連通常是基于GPU上原生的PCIe接口。就PCIe 技術而言,PCIe 1.0時,銅纜傳輸距離為10米,而發展到PCIe 5.0時,這一距離縮短至1-2米;當速率進一步提高到64 GT/s和128 GT/s,也即PCIe 6.0和未來的PCIe 7.0,銅纜傳輸距離將進一步縮短至幾十厘米,幾乎無法通過PCIe標準的銅纜實現機架間數十米的傳輸要求。再加上PCIe技術需考慮到重定時器的使用,其技術復雜、昂貴又耗電。且隨著PCIe技術升級,傳輸距離縮短,所需要的retimer的數量也會越來越多,還會引入更多的功耗和時延。而光連接通過光纖傳輸信號,可以在極高帶寬下保持信號的完整性和穩定性。不僅可以顯著提升數據傳輸速度,還能降低數據傳輸的延遲。

3成本衡量

前面我們提到過,帶寬的提升將致使鏈路中retimer數量上升,在相同的傳輸距離下,如果采用光傳輸技術,所需的retimer和SCU(信號調節單元)會更少。此外,光組件的設計制造工藝較為成熟,成本也會變得更加可控,加上光纖所占空間明顯小于銅纜,也有機會提升數據中心的整體密度,實現系統成本的降低。

另一方面,單 Lane 128G的傳輸速率將直接對PCIe 布線層面發起挑戰。在Gen5/Gen6布線標準中提供了使用銅電纜在系統內部和系統之間傳輸 PCIe 的選項。銅電纜比 PCB 走線具有更少的信號損失,能克服高頻通信的直接缺點,技術的升級將使得PCIe 7.0采用較粗的銅纜來克服高頻通信,相較于前一代技術勢必會帶來成本的增加。PCIe 7.0技術升級也會對相應的服務器PCB工藝帶來挑戰,隨著信號速率的飆升,PCB產品層數增加,BGA間距縮小,板厚顯著增加,厚徑比提升明顯。這些變化也將導致材料成本和加工工藝難度的大幅增加。

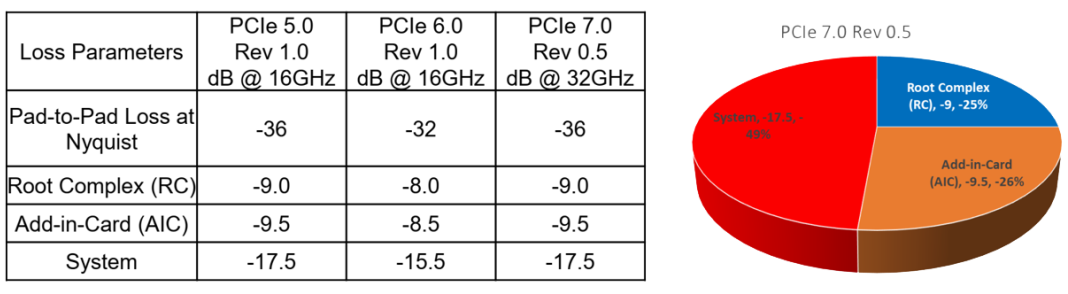

如下圖所示,PCIe 7.0 Rev 0.5版本定義的理論損耗和分配,在7.0的奈奎斯特頻率點(32GHz),Pad到Pad的損耗要求為-36dB,與6.0和5.0相比,在相同頻點(16GHz)的損耗大大收緊。

光傳輸技術的可實現性

PCI-SIG于去年8月宣布組建PCIe光學工作組,并計劃采用多種技術來支持 PCIe,包括可插拔光收發器、板載光學器件、共封裝光學器件和光學 I/O。而我們也在今年看到了不同產業鏈的廠商在開展基于PCIe的光學產品研究,較為實際的例子是某服務器廠商基于PCIe Gen5的光互連方案將信號的傳輸距離從1.4米擴展到20米。該方案成功體現了光傳輸的優越性。

然而,短期內實現光傳輸技術的過渡卻是較為困難,最初PCIe的接口并沒有考慮過光傳輸的可能性,這就意味著現有的PCIe技術的架構幾乎是基于電信號傳輸設計。首先我們需要考慮光傳輸與電氣層兼容問題,其次是與PCIe 協議層的適配性,再者是如何通過光纖傳輸PCIe 信號以及基于光纖的PCIe 外形標準如何制定 、FEC標準如何制定等等問題,小編相信伴隨協會的技術完善以及越來越多廠商的加入,我們將能看到更清晰的基于PCIe光傳輸技術應用的前景。

是德科技PCIe 7.0測試解決方案

在年初的展會上是德科技也與各廠商聯合展出了基于Gen7的測試方案預研。下面,我們就一起來看看Gen7基于光電技術測試方案詳情。

1傳統電氣層解決方案

是德科技聯合 ALPHAWAVE SEMI于2024年1月30日-2月1日舉辦的DesignCon 2024展會上聯合展示了128G Gen7 收發端解決方案。

DesignCon2024-EnablePCIe 7.0 Technology

該解決方案由PCI-SIG協會主席Rick Eads演示,方案主要由 UXR系列實時示波器及高性能誤碼儀M8050A組成。

2光傳輸技術解決方案初探究

是德科技于2024年3月24-28日舉辦的OFC2024展會上展示了低功耗 PCIe 7.0 光互連技術,支持新興的大型語言模型對更高效信號傳輸的需求。

OFC2024-PCIe7.0OverOptics Demonstration

該解決方案包括M8050A 高性能誤碼儀(120G baud)、DCA-M N1092A(光通道)、N7736C光開關和800G DR8 LPO產品。

關于是德科技

是德科技(NYSE:KEYS)啟迪并賦能創新者,助力他們將改變世界的技術帶入生活。作為一家標準普爾 500 指數公司,我們提供先進的設計、仿真和測試解決方案,旨在幫助工程師在整個產品生命周期中更快地完成開發和部署,同時控制好風險。我們的客戶遍及全球通信、工業自動化、航空航天與國防、汽車、半導體和通用電子等市場。我們與客戶攜手,加速創新,創造一個安全互聯的世界。

-

計算機

+關注

關注

19文章

7418瀏覽量

87711 -

服務器

+關注

關注

12文章

9017瀏覽量

85182 -

PCIe

+關注

關注

15文章

1217瀏覽量

82436 -

是德科技

+關注

關注

20文章

868瀏覽量

81676

原文標題:PCIe 7.0 互連— PCIe的盡頭會是光嗎?

文章出處:【微信號:是德科技KEYSIGHT,微信公眾號:是德科技KEYSIGHT】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

PCIe 5.0產品測試驗證火熱進行中,為未來引領消費者市場做好準備

是德科技發布最新針對 802.11ad 測試解決方案

是德科技物聯網測試解決方案

是德科技推出全新的發射機(Tx)和接收機(Rx)綜合測試解決方案

泰克提供業界首創的 PCIe 6.0 測試解決方案

是德科技發布端到端PCIe5.0/6.0測試解決方案

SK hynix公司使用是德科技PCIe測試解決方案驗證計算快速鏈路技術

PCIe 7.0規范何時最終確定?

新思科技推出業界首款PCIe 7.0 IP解決方案

新思科技發布PCIe 7.0 IP解決方案,賦能AI與HPC前沿設計

新思科技推出業界首款PCIe 7.0 IP解決方案

新思科技PCIe 7.0驗證IP(VIP)的特性

是德科技推出PCIe和UCIe仿真解決方案

Cadence展示完整的PCIe 7.0 IP解決方案

是德科技PCIe 7.0測試解決方案

是德科技PCIe 7.0測試解決方案

評論