產品簡述

MS5046T/MS5047T/MS5048T/MS5048N 是適合高精

度、低成本測量應用的 16bit 模數轉換器。其內部集成低

蕩器。MS5047T、MS5048T、MS5048N 內部還集成低溫

漂基準和兩路匹配的可編程電流源。MS5048T/MS5048N

支持四路差分輸入,MS5047T 支持兩路差分輸入,

MS5046T 支持單路差分輸入。此外,MS504XT 系列芯片

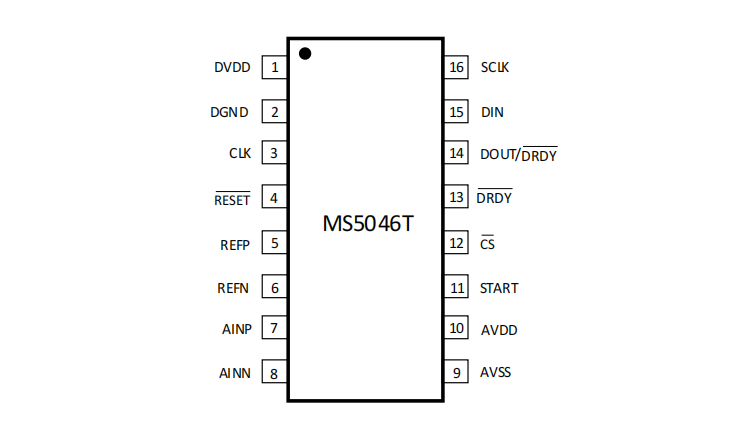

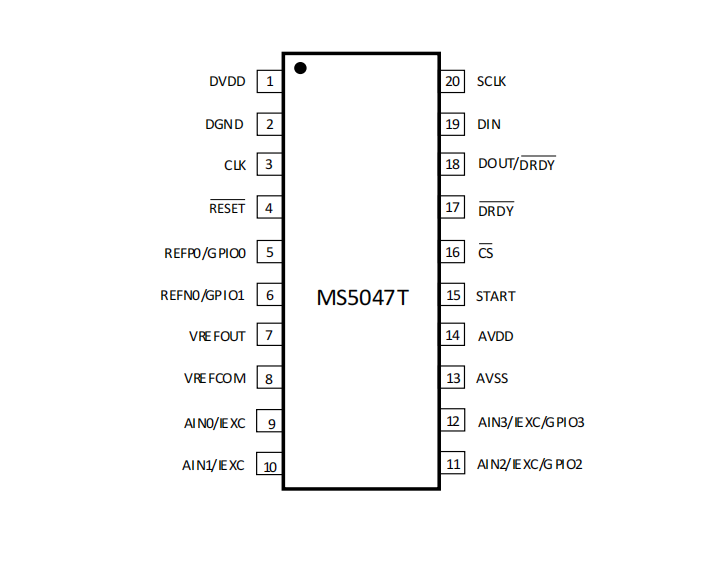

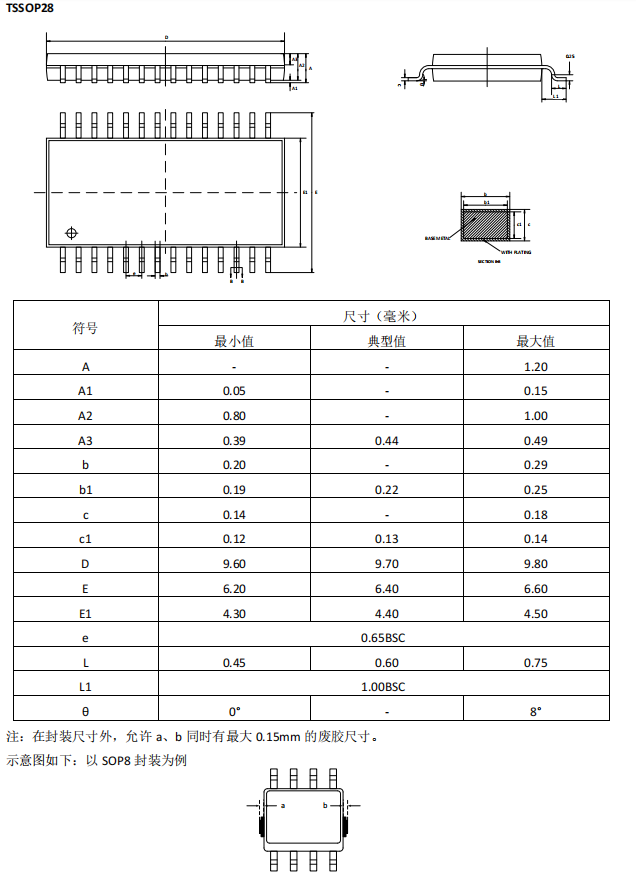

MS5046T采用TSSOP16 封裝,MS5047T 采用 TSSOP20

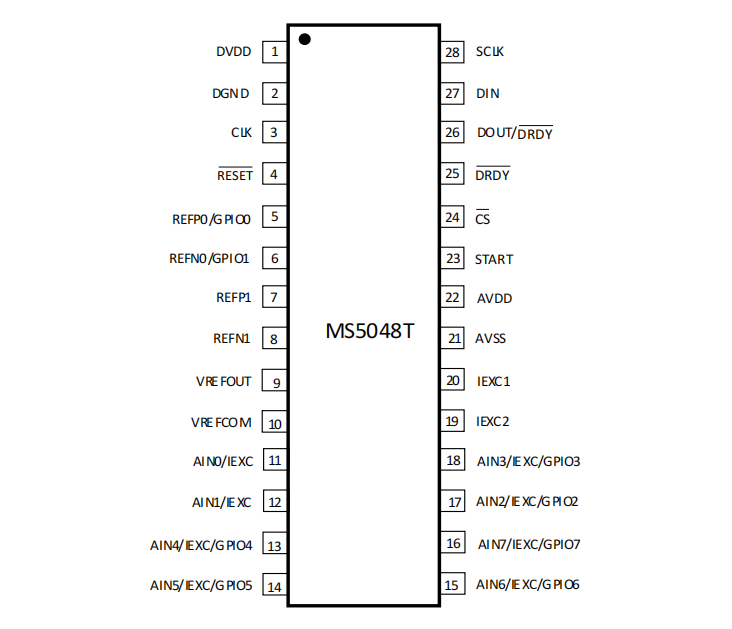

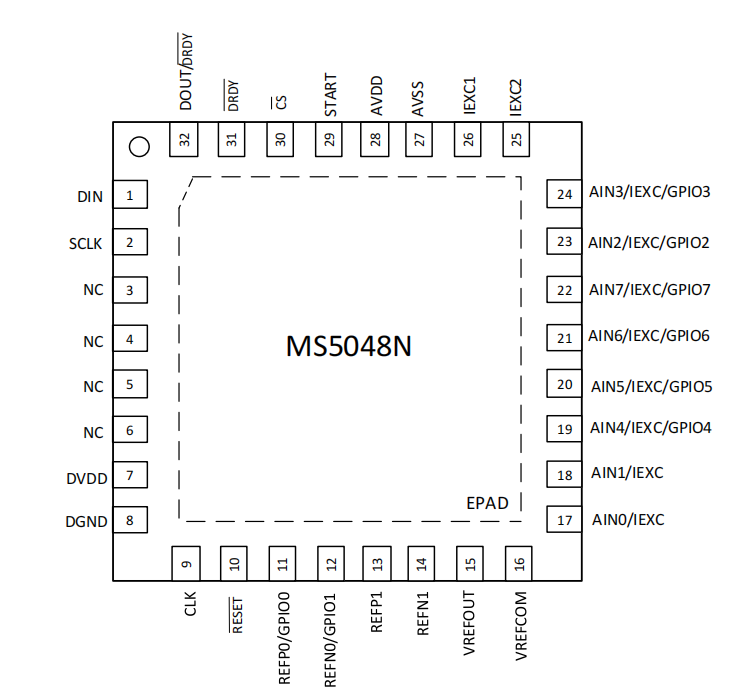

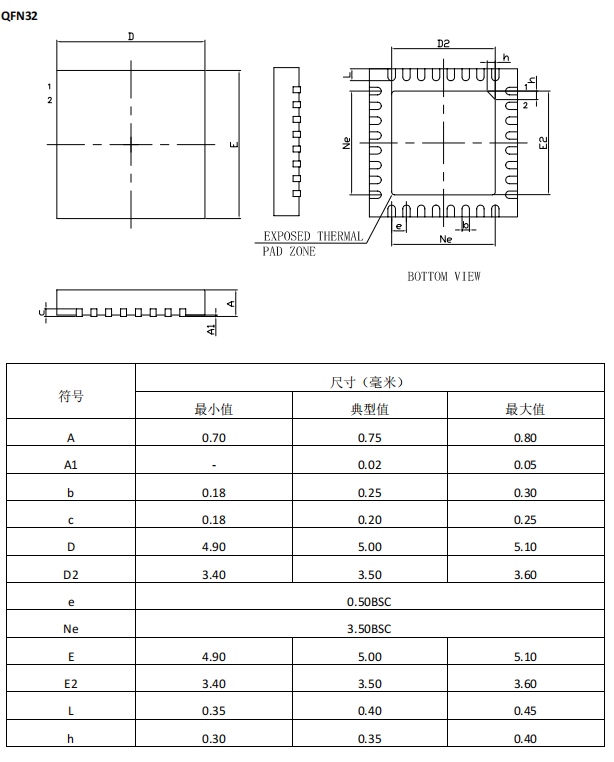

封裝,MS5048T 采用 TSSOP28 封裝,MS5048N 采用

QFN32 封裝。

主要特點

?可編程轉換速率:最高 2kSPS

?集成輸入多路選擇器

?可編程增益:1 到 128

?集成雙路匹配可編程電流源

?集成內部溫度傳感器

?集成電源檢測電路和 VREF 檢測電路

?集成自校準和系統校準

?兼容 SPI 接口

?集成 50Hz/60Hz 限波濾波@20SPS

單電源:2.7V 到 5.25V

雙電源:±2.5V

?工作溫度范圍:-40°C ? 125°C

應用

?應力檢測

?溫度檢測

?流量計

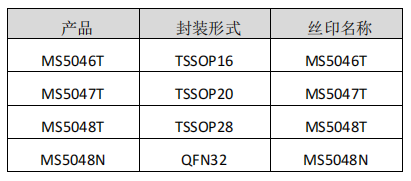

產品規格分類

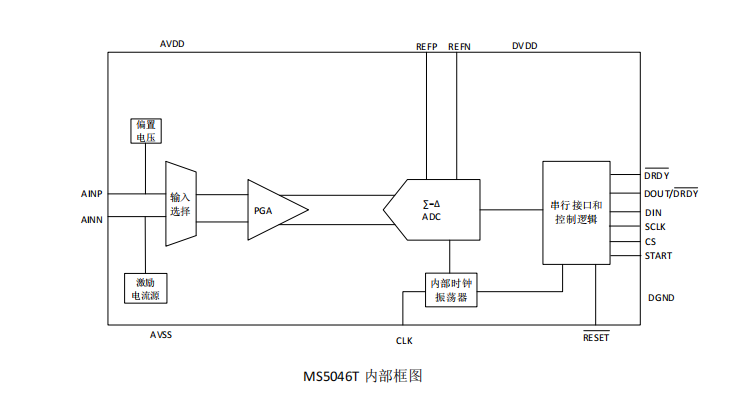

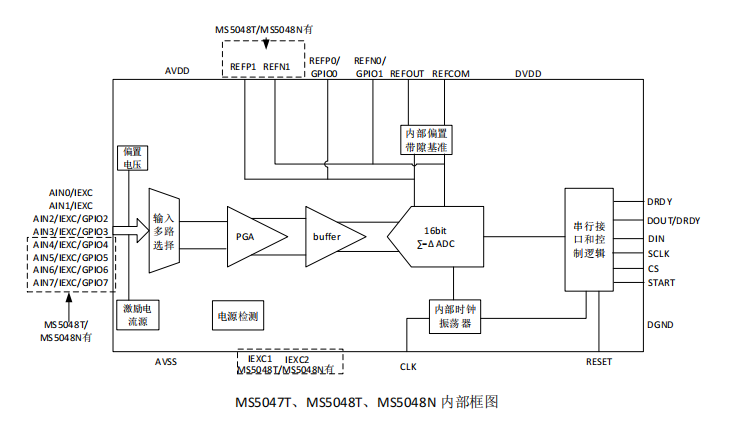

內部框圖

管腳圖

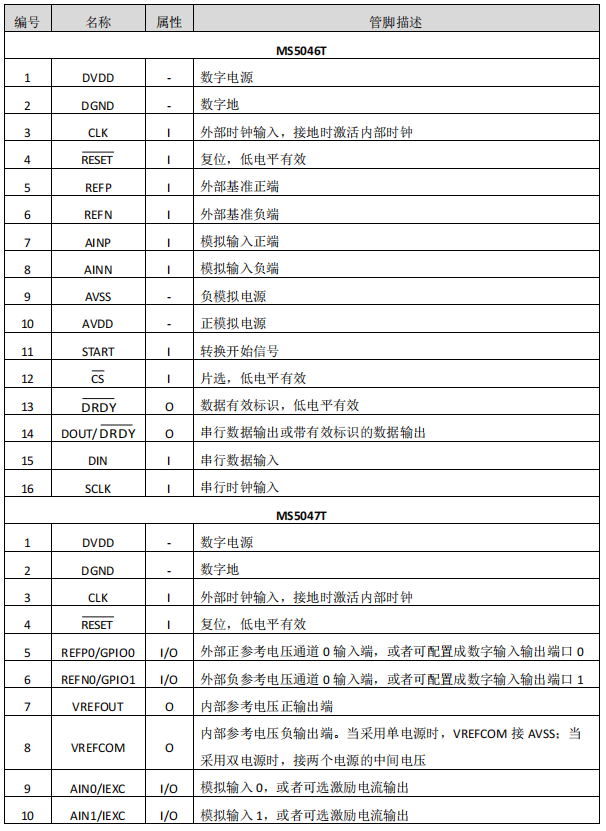

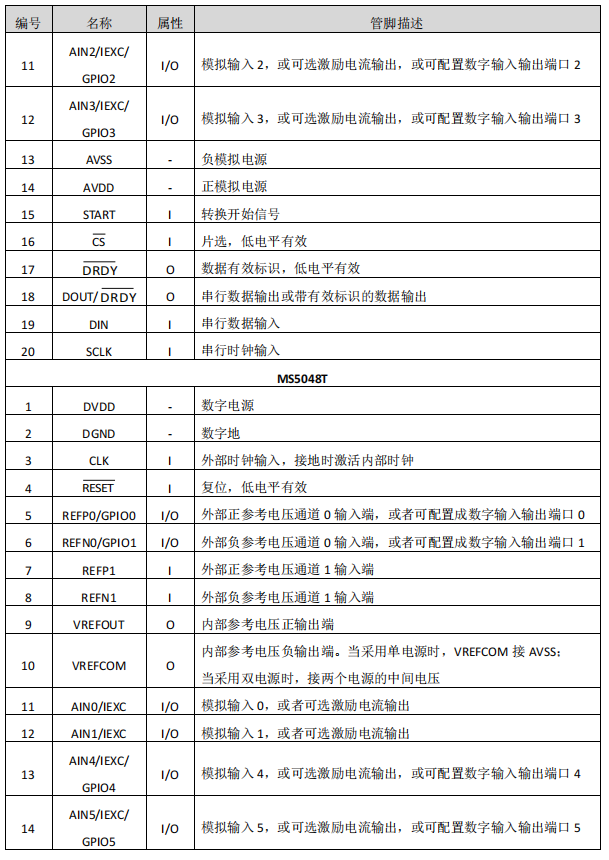

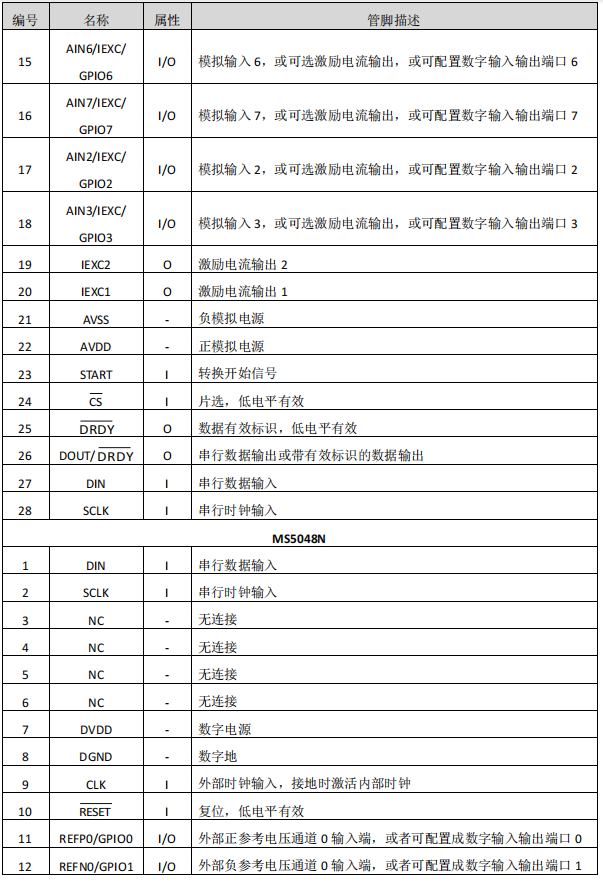

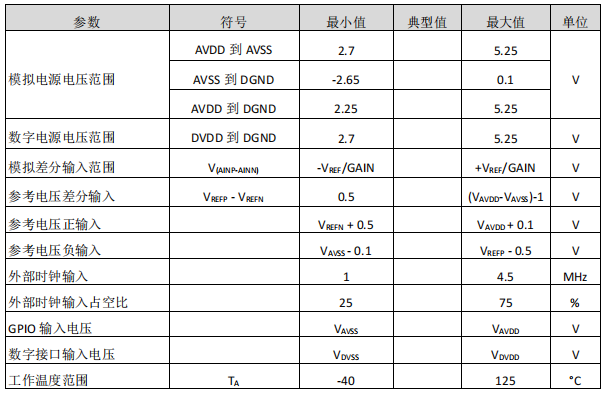

管腳說明

如有需求請聯系——三亞微科技 王子文(16620966594)

極限參數

芯片使用中,任何超過極限參數的應用方式會對器件造成永久的損壞,芯片長時間處于極限工作

狀態可能會影響器件的可靠性。極限參數只是由一系列極端測試得出,并不代表芯片可以正常工作在

此極限條件下。

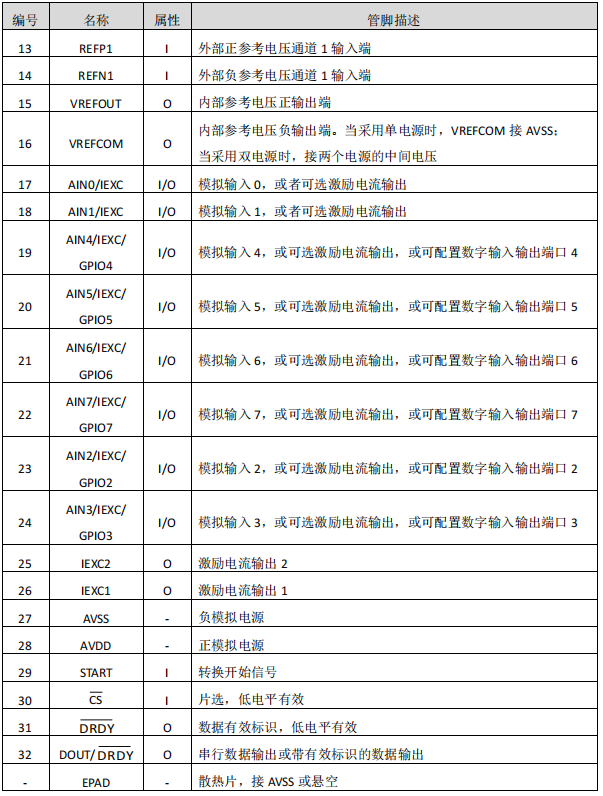

推薦工作條件

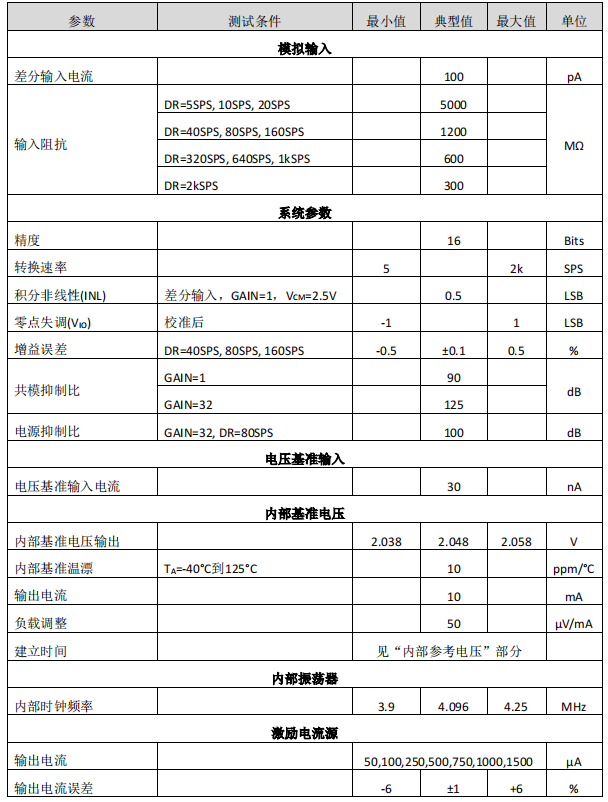

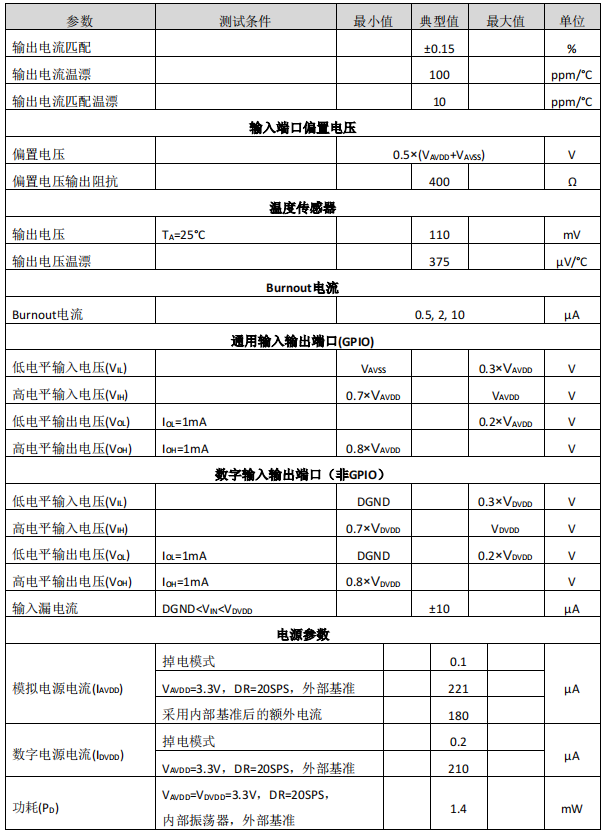

電氣參數

VAVDD=5V;VDVDD=3.3V;VAVSS=0V;外部VREF=2.048V;fCLK=4.096MHz。

除非另外標注,參數為全溫度范圍。

如有需求請聯系——三亞微科技 王子文(16620966594)

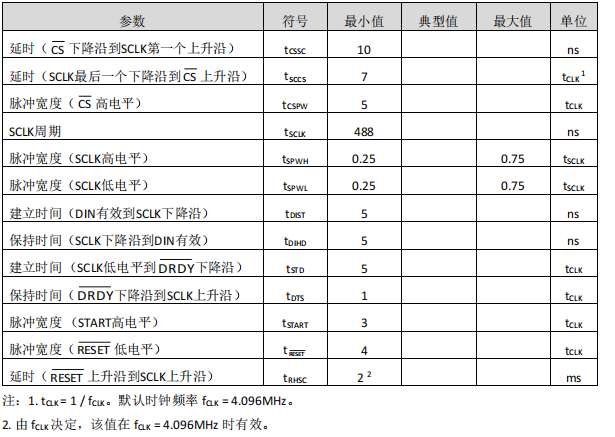

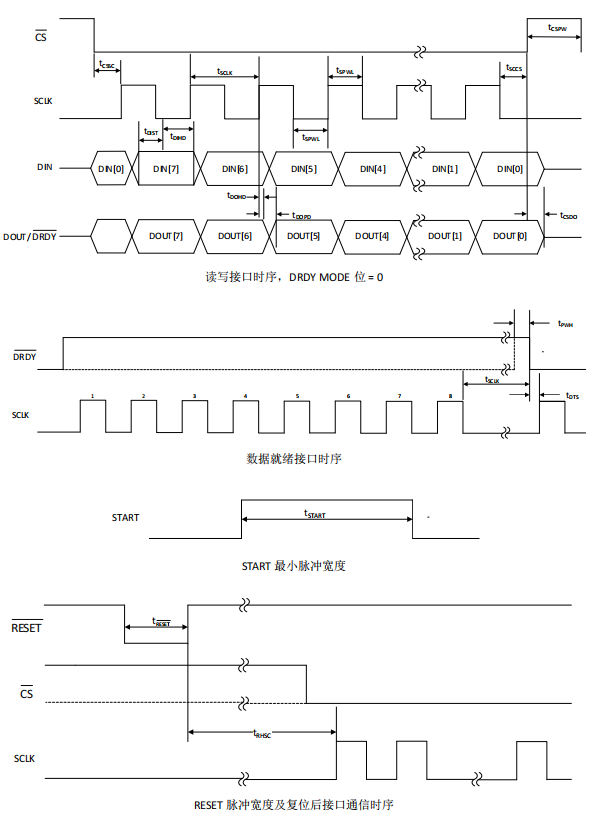

時序參數

VDVDD=2.7V 到 5.25V,DGND=0V,輸入邏輯 1=DVDD,輸入邏輯 0=GND。

除非另外標注,參數為全溫度范圍。

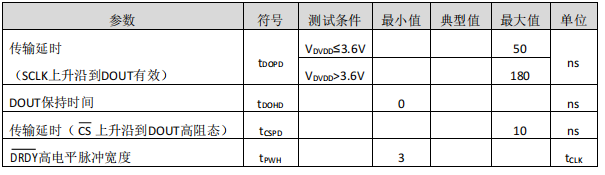

開關參數

VDVDD=2.7V 到 5.25V,DGND=0V,輸入邏輯 1=DVDD,輸入邏輯 0=GND。

除非另外標注,參數為全溫度范圍。

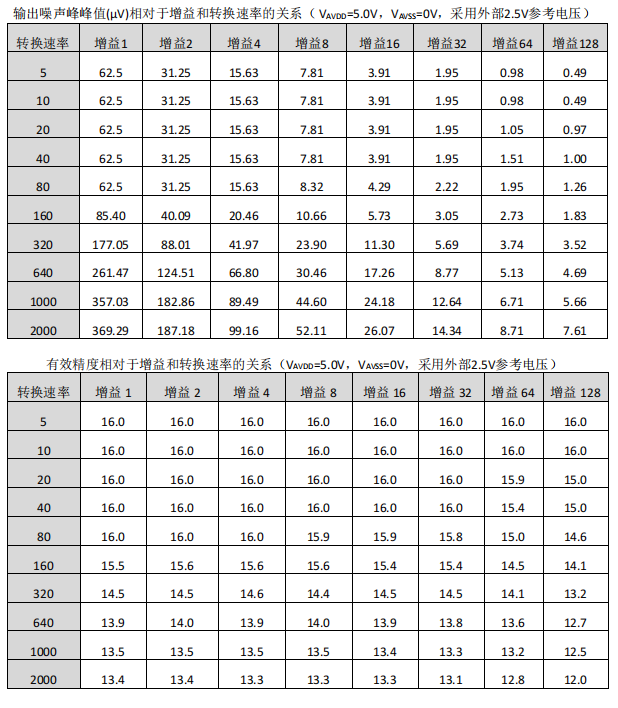

輸出噪聲和分辨率(外部參考電壓)

下表給出一些增益和轉換速率設置下的 MS5048T 的輸出均方根噪聲。所提供的數據是針對雙極性

輸入范圍以及采用 2.5V 外部基準電壓源而言。這些數值是差分輸入電壓為 0V 時的典型值。注意 ,有

效分辨率 是利用均方根噪聲計算得出的。這些數值為典型值,四舍五入到最接近的 LSB。

功能描述

概述

MS5046T/MS5047T/MS5048T/MS5048N 是高集成度的 16bit 模數轉換器,集成了低噪聲、高輸入阻

抗可變增益放大器、輸入多路選擇器、低溫漂基準、∑-Δ ADC、內部振蕩器和 SPI 接口。

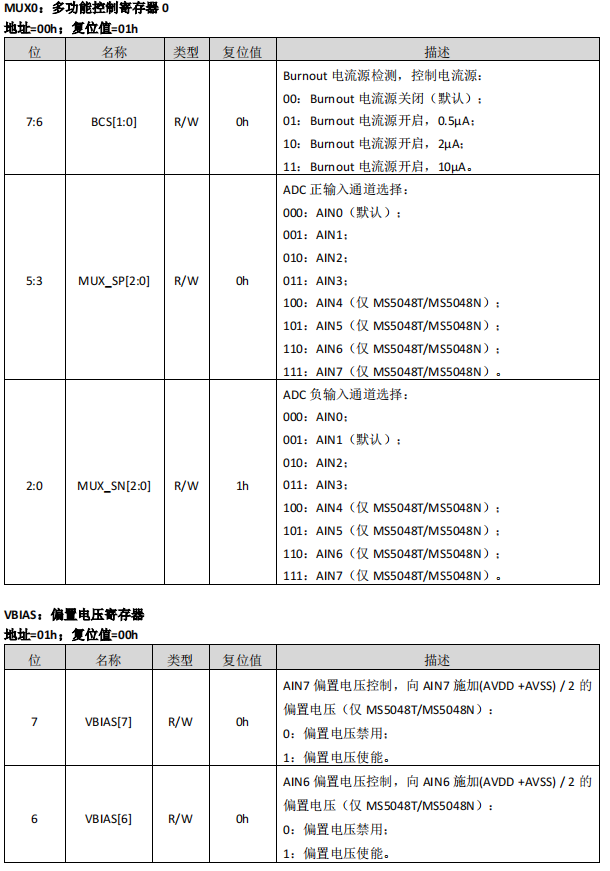

模擬輸入通道

模數轉換器的輸入通過片上多路選擇器和 PGA 輸入到內部調制器。MS5046T 有一對差分輸入端口;

MS5047T 可通過寄存區 MUX0,配置成兩路差分輸入;MS5048T/MS5048N 可通過寄存區 MUX0 配置成

4 路差分輸入。此外,輸入端口可以配置連接到內部激勵電路產生器或偏置電壓產生器。通過輸入多

路選擇器也可檢測溫度、AVDD、DVDD 和外部基準信號。輸入端口也可配置成通用 GPIO 端口。

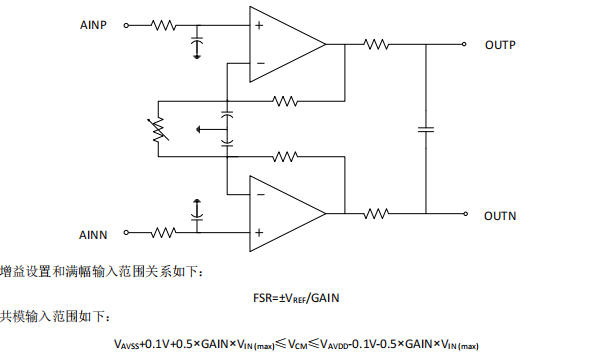

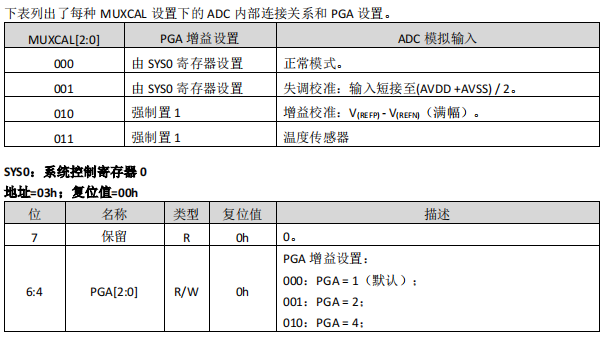

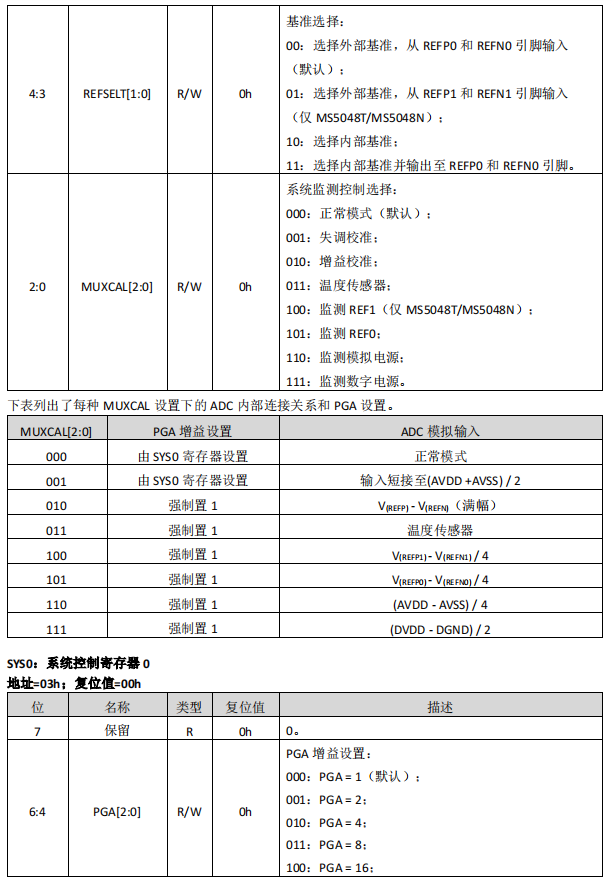

低噪聲 PGA

MS5046T/MS5047T/MS5048T/MS5048N 內部集成一個低漂移、低噪聲、高輸入阻抗的可編程放大

器。通過寄存器 SYS0,增益設置成 1、2、4、8、16、32、64、128。PGA 由兩個斬波穩定放大器和電

阻反饋組成,PGA 的輸入通過一個防電磁干擾濾波器,示意圖如下:

時鐘源

MS5046T/MS5047T/MS5048T/MS5048N 可使用外部時鐘或內部時鐘。在上電或復位前,把 CLK 腳接

GND,可激活內部時鐘。CLK 腳在任何時候接外部時鐘源,都會關閉內部時鐘,此時器件會一直工作在

外部時鐘模式,此種情況下,只有重新上電或復位,器件才會更改時鐘工作模式。

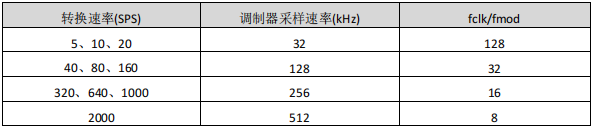

調制器

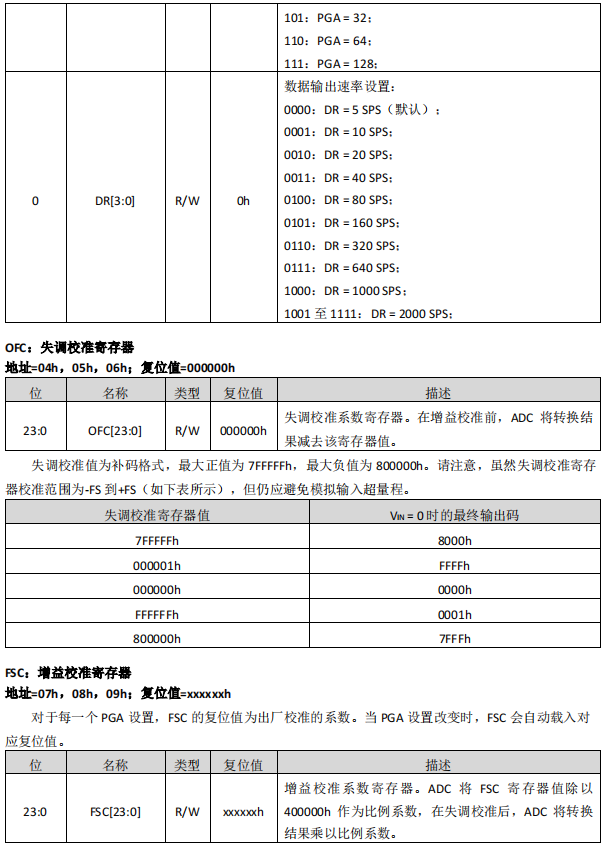

芯片內部集成了 3 階調制器,輸出 PCM 碼流到數字濾波器,調制器的時鐘速率設置如下:

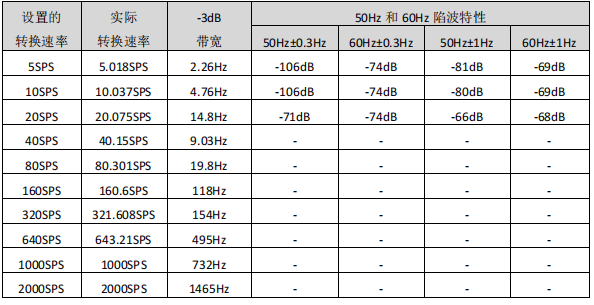

數字濾波器

芯片內部集成一個可編程的 FIR 數字濾波器,下表顯示在 4.096MHz 外部時鐘下的濾波特性。

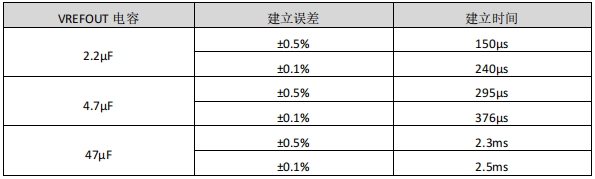

內部參考電壓

芯片內部集成了一個 2.048V 低溫漂電壓基準,電壓基準輸出 VREFOUT 和 VREFCOM 端需接

2.2μF~47μF 電容,較大電容噪聲濾波效果較好,但是基準啟動時間也較大。出于穩定性考慮,

VREFCOM 需要有小于 10Ω 的 AC 通路到 AVSS。下圖列出基準啟動時間和外圍電容關系。

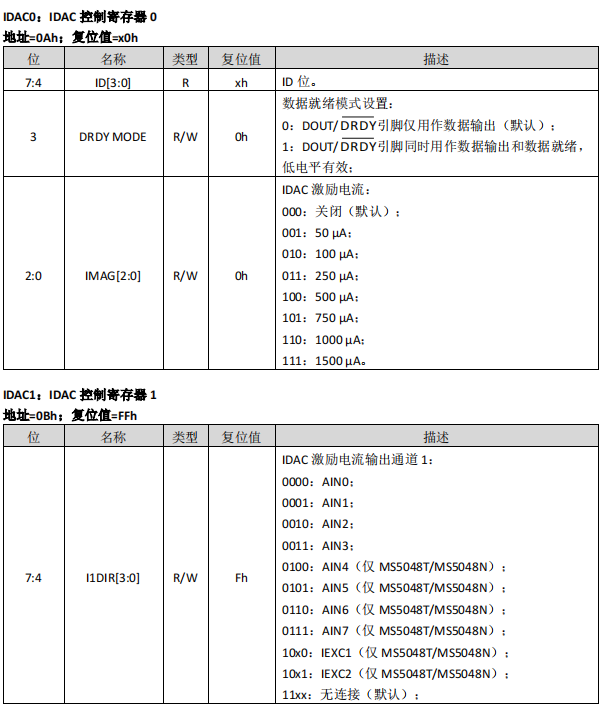

激勵電流輸出

對于 RTD 應用,MS5047T、MS5048T、MS5048N 內部集成了兩路匹配的激勵電流源(IDACs)。對于三

線 RTD 應用,匹配電流源可以消除線電阻誤差影響,輸出電流源可以配置為 50μA、100μA、250μA、

500μA、750μA、1000μA、1500μA。

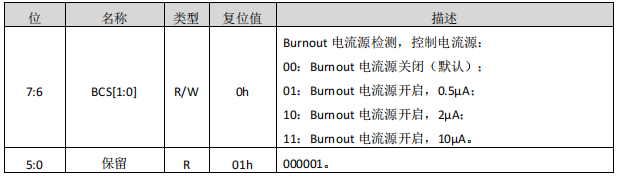

傳感器檢測

通過內部寄存器可以配置 Burnout 電流(0.5μA、2μA、10μA)來檢測外接傳感器的失效,當傳感

器處于斷路狀態,內部 Burnout 電流源把正輸入端拉到 AVDD,負輸入端拉到 AVSS,導致滿幅轉換輸

出,這樣會指示傳感器過載或沒有參考電壓,而接近 0V 的轉換輸出指示可能是傳感器短路。

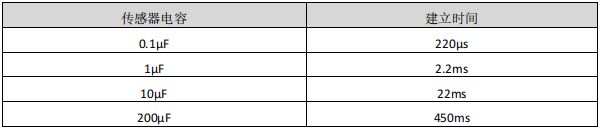

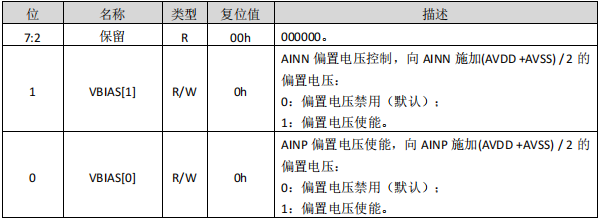

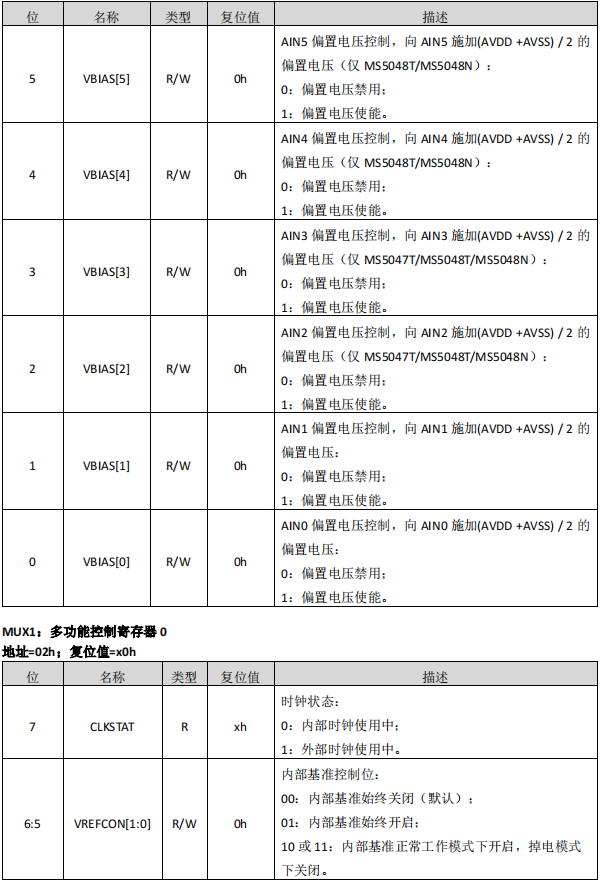

偏置電壓產生器

對于無偏置的熱電偶應用,芯片內部集成了偏置電壓產生器,電壓為模擬電源電壓的中間電平。

對于不同電容的傳感器,偏置電壓建立時間不同,如下表所示。當偏置電壓應用于多個通道時,可導

致應用的通道內部短路,所以必須限制流過器件的電流。

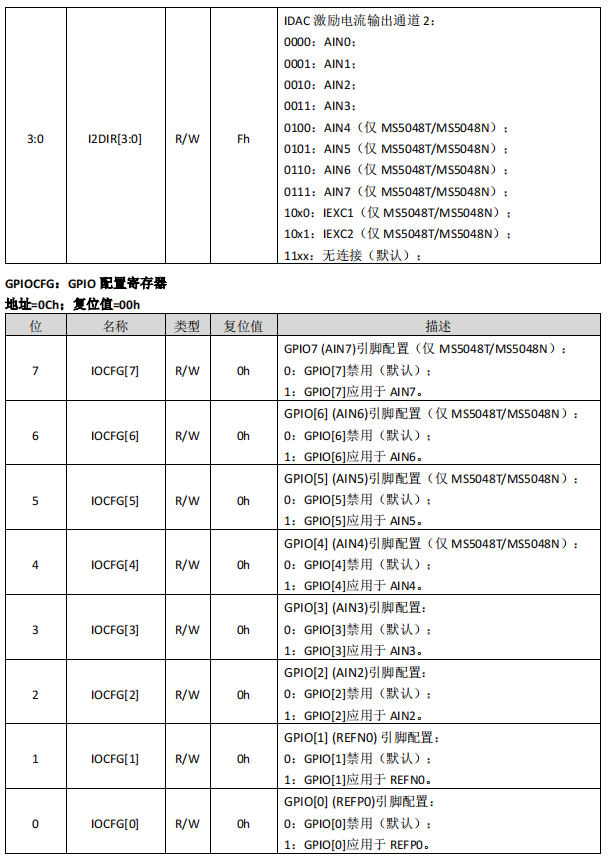

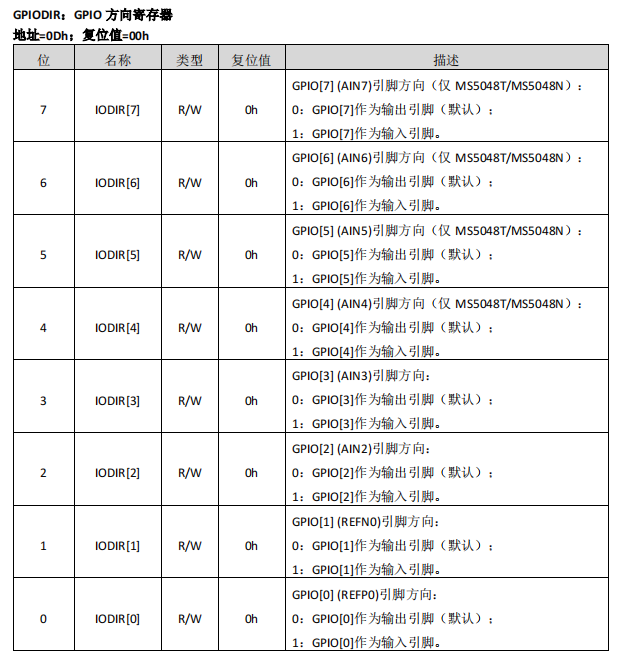

數字通用 IO

通過寄存器可以控制模擬輸入復用端口的屬性,可配置成模擬輸入或 GPIO,寄存器 IOCFG 控制是

否作為數字 IO,寄存器 IODIR 控制數字端口的輸入輸出特性,IODAT 控制數字輸入輸出的具體數據類

型。

電源電壓檢測

芯片內部集成檢測數字和模擬電源電壓,檢測結果是 1/4 的電源電壓。

外部參考電壓檢測

芯片內部集成外部參考電壓檢測功能,檢測結果是 1/4 的實際外部參考電壓。檢測外部參考電壓

時,必須使能內部集成基準電壓。

環境溫度檢測

芯片內部集成環境溫度檢測功能,當打開溫度檢測功能時,兩個二極管的陽極連到模擬輸入,在

室溫下,二極管輸入差壓為 110mV,溫漂為 375μV/°C。

上電

芯片上電過程中,內部上電復位電路產生一個復位脈沖,可復位全部數字電路,復位時間為 2 16個

系統時鐘周期。復位過程中 SPI 接口不能操作。建議上電后執行一次復位操作。

復位

當RESET 腳變低時,觸發芯片內部復位,所有寄存器復位到默認值。當系統時鐘為 4.096MHz,

RESET 腳上升沿到來后,芯片會在 2ms 后退出復位狀態。芯片復位也可通過設置 RESET 指令執行。

掉電

芯片使用 SLEEP 指令或把 START 置低,進入掉電模式。

轉換控制

芯片通過 START 的上升沿,可精確控制轉換周期的開始,轉換完成后芯片內部 DRDY 置低。當寄存器 IDAC0 中

DRDY MODE 位值 1 時,輸出 DOUT/ DRDY 在轉換完成后置低。轉換完成后且START 為低電平,芯片自動進入

掉電模式,當下一個 START 上升沿到來后,內部模擬電路需要 32 個fmod時鐘周期的建立時間。

當 START 為高電平時,芯片會連續轉換。

芯片轉換也可通過 SPI 指令來執行,使用 WAKEUP 指令可喚醒一次轉換過程,當使用指令控制時,

START 必須置高。另外。發送 SYNC 指令,可立刻開始一個新的轉換過程。對寄存器 MUX0、VBIAS、

MUX1 和 SYS0 任意一個寄存器寫操作,都會復位數字濾波器,相應的也會重新啟動一次轉換。

單周期建立

對于所有的增益和轉換率設置,MS5046T/MS5047T/MS5048T/MS5048N 可以完成單周期建立。在

轉換率為 2kSPS 時,改變配置寄存器需要使用 WREG 指令,SCLK 時鐘周期不能超過 520ns,相鄰兩個寄

存器字節不能超過 4.2μs,另外,當開始對四個地址寄存器進行多個寫操作后,需等待至少 64 個系統

時鐘周期,才能做其他寫指令。

數字濾波器復位操作

當芯片執行下列操作時,會復位數字濾波器:發送 RESET 指令、對 MUX0、VBIAS、MUX1、SYS0 四

個寄存器進行寫操作、發送 SYNC 指令和 START 腳出現上升沿。

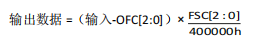

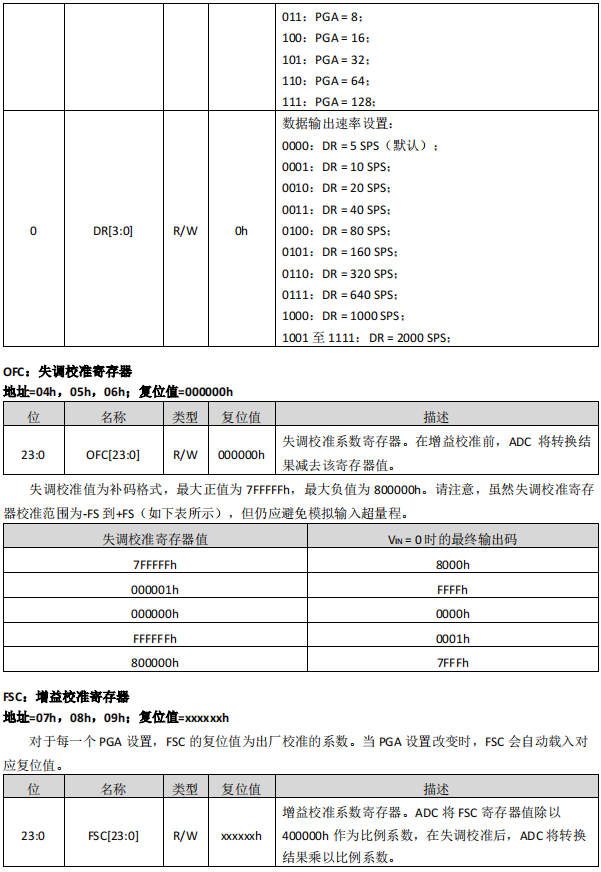

校準

轉換結果輸出前要進行失調校準和增益校準,ADC 轉換結果首先減去零點校準值(存在 OFC 寄存

器),后乘以增益校準系數。

校準指令

芯片提供三種校準指令:系統增益校準、系統失調校準和失調自校準。

系統失調和自失調校準

系統失調校準可以校準芯片內部和外部的失調誤差,系統失調校準可以通過發送 SYSOCAL 指令來

觸發。失調自校準可以通過發送 SELFOCAL 指令來觸發,在失調自校準期間,配置的輸入通道和外部電

路斷開,在芯片內部短接到電源電壓的中間值,轉換完成后更新 OFC 寄存器。

系統增益校準

系統增益校準信號通路上的增益誤差,可通過發送 SYSGCAL 指令來激活。

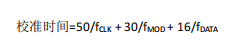

校準時間

校準激活后,芯片會進行 16 次相應的轉換,并把轉換結果求平均后計算校準值,這可以提高校準

精度。校準所需時間如下:

如有需求請聯系——三亞微科技 王子文(16620966594)

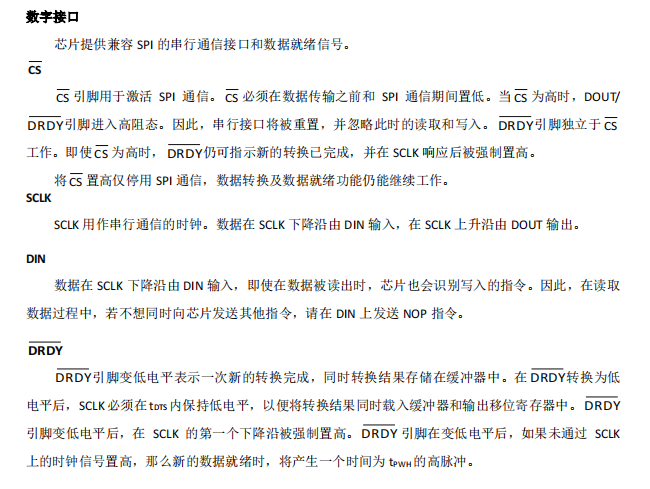

SPI 復位

可通過將 CS 引腳拉高,僅復位串行接口而不復位寄存器和數字濾波器。將 RESET 引腳置低,可復

位串行接口以及所有數字功能模塊,并開啟一次新的轉換。

當 CS 一直保持低電平時,必須以完整的 8 位作為一個字節寫入寄存器,否則會導致 SPI 通信異常,

芯片將無法識別指令。若 SPI 空閑時間超過 64 個轉換周期,將會重置接口。

掉電模式下的 SPI 通信

當 START 引腳為低或者芯片處于掉電模式,只能發送 RDATA、RDATAC、SDTAC、WAKEUP 和 NOP 指

令。RDATA 指令可用于重復讀取上一次轉換結果。

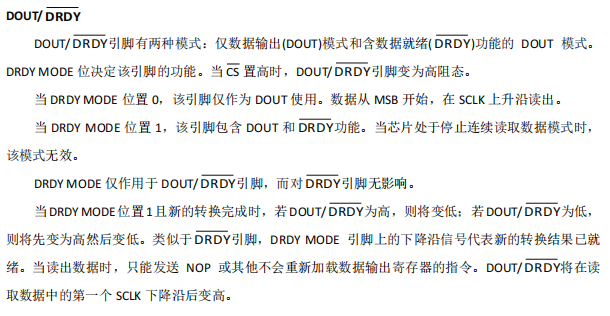

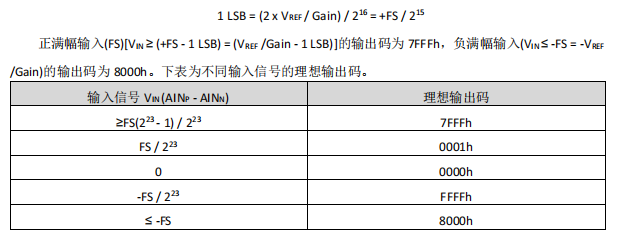

數據結構

芯片輸出數據格式為 16 位二進制補碼。LSB 計算公式為:

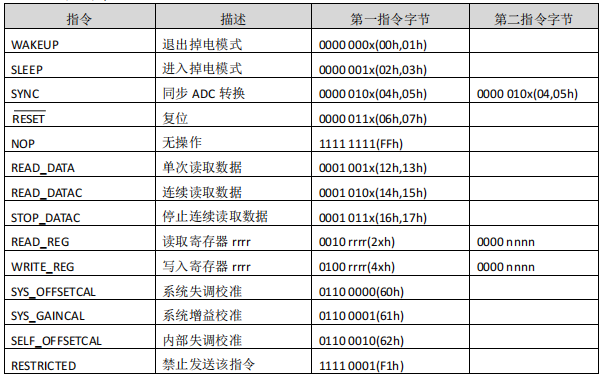

指令

可通過 13 個指令來控制芯片。其中對于芯片寄存器數據的讀寫指令(RREG 和 WREG),需要額

外的字節作為指令的一部分。NOP 指令可用于僅讀出芯片數據,同時不發送其他指令。

1. n = 讀寫寄存器數 - 1;

2. r = 寄存器地址;

3. x = 任意值;

WAKEUP(0000 000x)

在執行 SLEEP 指令后,可通過 WAKEUP 指令使芯片上電。執行 WAKEUP 指令后,芯片將在 SCLK 的

第 8 個下降沿開始上電。

SLEEP(0000 001x)

發送 SLEEP 指令后,芯片完成當前轉換后,進入掉電模式。注意該指令不會關斷內部參考電壓。

在 SLEEP 指令后,發送 WAKEUP 指令,芯片會執行單次轉換。

WAKEUP 和 SLEEP 指令等效于芯片的 START 引腳的控制效果。

如果 START 引腳為低電平,WAKEUP 指令無效。當 SLEEP 指令生效時, CS 必須保持低電平。

SYNC(0000 010x)

SYNC 指令會復位 ADC 數字濾波器。通過發送 SYNC 指令,可以同步連接到同一 SPI 總線的多個設

備。

RESET(0000 011x)

復位指令可復位所有寄存器和數字濾波器。該指令等效于 RESET 引腳。但是 RESET 指令無法復位

串行接口。可以先用 CS 引腳復位串行接口,然后發送 RESET 指令來復位芯片。RESET 指令與硬件復位

類似,當系統時鐘頻率為 4.096MHz 時,需要 2ms 來完成復位。因此,在發送 RESET 指令后,必須等待

2ms 后,才能再次開始 SPI 通信。

READ_DATA(0001 001x)

READ_DATA 指令可載入最近一次轉換結果至輸出寄存器。在 READ_DATAC 模式下,該指令也能生

效。

當多次讀取轉換結果時,可以在讀取上一次轉換結果時,在最后 8 個時鐘發送該指令。

READ_DATAC(0001 010x)

READ_DATAC 指令使能連續讀取數據模式。該模式為上電復位后的默認模式。在連續讀取數據模式

下,新的轉換結果將自動加載到 DOUT 上。當 DRDY 變低后,可通過發送 16 個 SCLK,從芯片讀取轉換

結果。READ_DATAC 指令必須在 DRDY 變低后發送,并在下一次 DRDY 變低時生效。

確保在 DRDY 回到低電平前,完成數據讀取(轉換結果或者寄存器回讀),否則數據將會丟失。

STOP_DATAC(0001 011x)

STOP_DATAC 指令停止連續讀取數據模式。在停止連續讀取數據模式下,當 DRDY 變低時,轉換結

果將不會自動加載到 DOUT 上。在此模式下,新的 ADC 轉換完成不會中斷芯片的讀取,可使用

READ_DATA 指令來獲取轉換結果。STOP_DATAC 指令在下一次 DRDY 變低時生效。

READ_REG(0010 rrrr, 0000 nnnn)

通過 READ_REG 指令,可讀取 15 組寄存器的數據。讀取的寄存器的數量等于指令第二字節數+1。

如果待讀取數超過剩余寄存器數,地址將會回到初始位置。READ_REG 指令的兩字節結構如下:

1. 第一指令字節:0010 rrrr,其中 rrrr 是第一個讀取的寄存器地址;

2. 第二指令字節:0000 nnnn,其中 nnnn = 待讀取寄存器數-1。

WRITE_REG(0100 rrrr, 0000 nnnn)

通過 WRITE_REG 指令,可對 15 組寄存器寫入數據。寫入的寄存器的數量等于指令第二字節數+1。

WRITE_REG 指令兩字節結構如下:

1.第一指令字節:0100 rrrr,其中 rrrr 是第一個寫入的寄存器地址;

2.第二指令字節:0000 nnnn,其中 nnnn = 待寫入寄存器數-1。

SYS_OFFSETCAL(0110 0000)

SYS_OFFSETCAL 指令啟動系統失調校準。當系統失調校準時,模擬輸入必須外部短接至輸入共模

范圍內的電壓。模擬輸入應該接近(AVDD + AVSS) / 2。當該指令完成后,OFC 寄存器會自動更新。

SYS_GAINCAL(0110 0001)

SYS_GAINCAL 指令啟動系統增益校準。當系統增益校準時,模擬輸入必須設置為滿幅。當該指令

完成后,FSC 寄存器會自動更新。

SELF_OFFSETCAL(0110 0010)

SELF_OFFSETCAL 指令啟動系統失調校準。當系統失調校準時,芯片內部將模擬輸入短接至中間電

源并執行校準。當該指令完成后,OFC 寄存器會自動更新。

NOP(1111 1111)

空操作指令。

RESTRICTED

禁止發送該指令至芯片

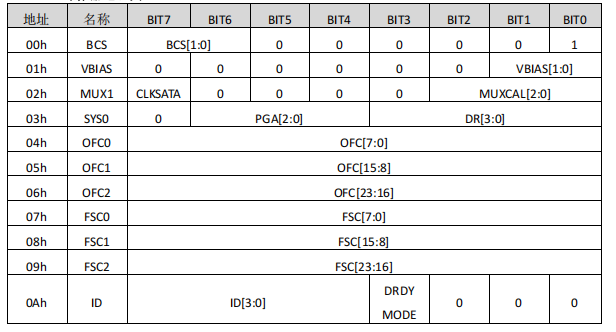

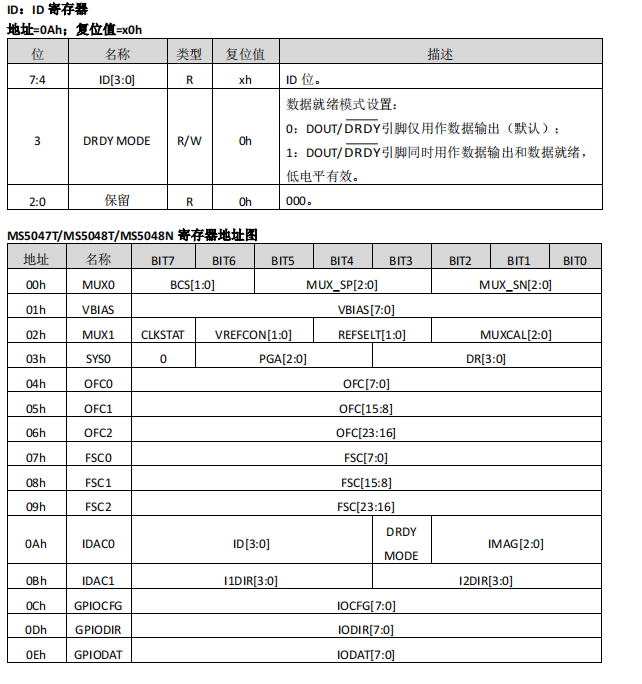

寄存器地址圖

MS5046T 寄存器地址圖

BCS:Burnout 電流源寄存器

地址=00h;復位值=01h

VBIAS:偏置電壓寄存器

地址=01h;復位值=01h

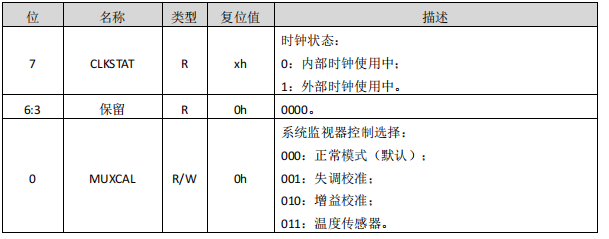

MUX:多功能控制寄存器

地址=02h;復位值=x0h

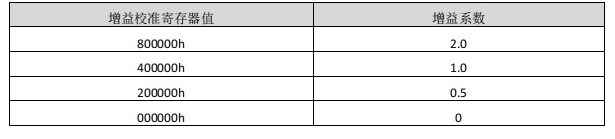

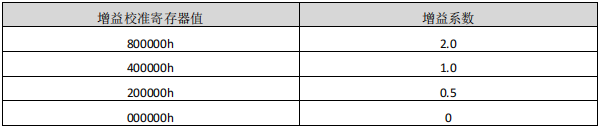

增益校準值為無符號二進制格式,當值為 400000h 時系數為 1.0。請注意,雖然增益校準寄存器可

以校準大于 1 的增益誤差(如下表所示),但仍應避免模擬輸入超量程。

如有需求請聯系——三亞微科技 王子文(16620966594)

如有需求請聯系——三亞微科技 王子文(16620966594)

增益校準值為無符號二進制格式,當值為 400000h 時系數為 1.0。請注意,雖然增益校準寄存器可

以校準大于 1 的增益誤差(如下表所示),但仍應避免模擬輸入超量程。

如有需求請聯系——三亞微科技 王子文(16620966594)

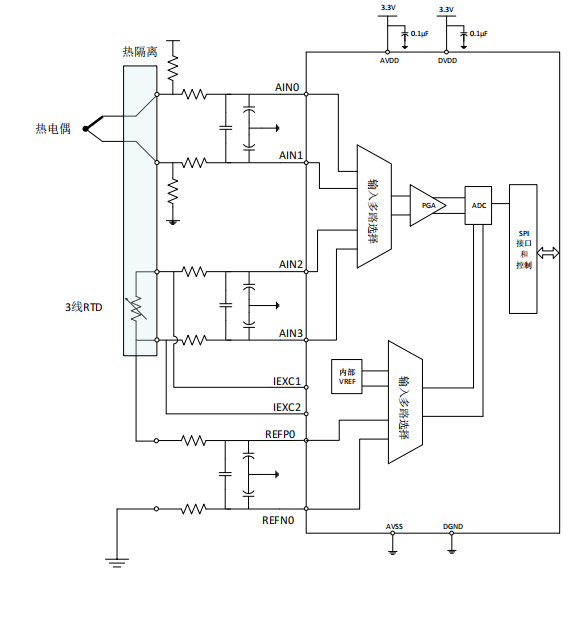

典型應用圖

下圖是 MS5048T/ MS5048N 用作熱電偶測量應用的示意圖。

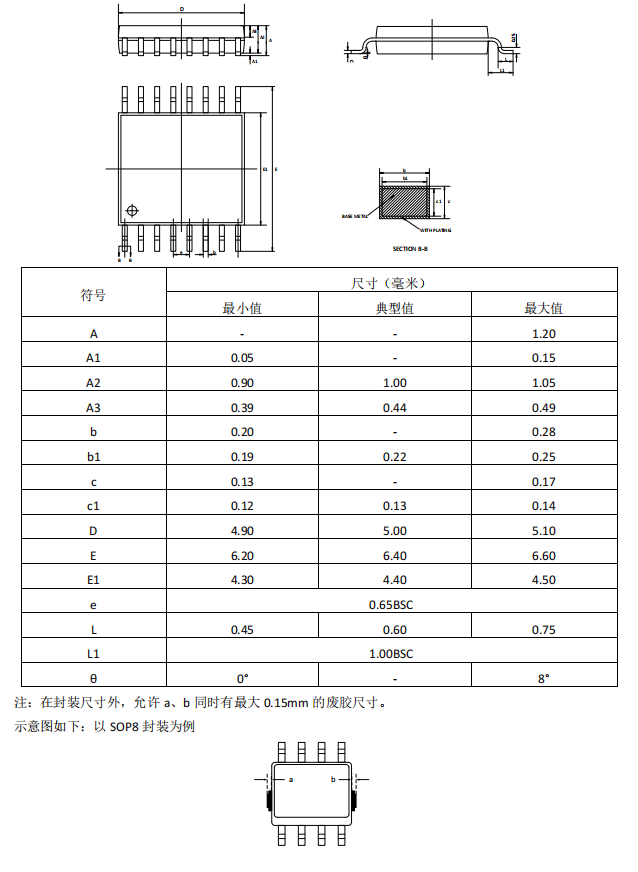

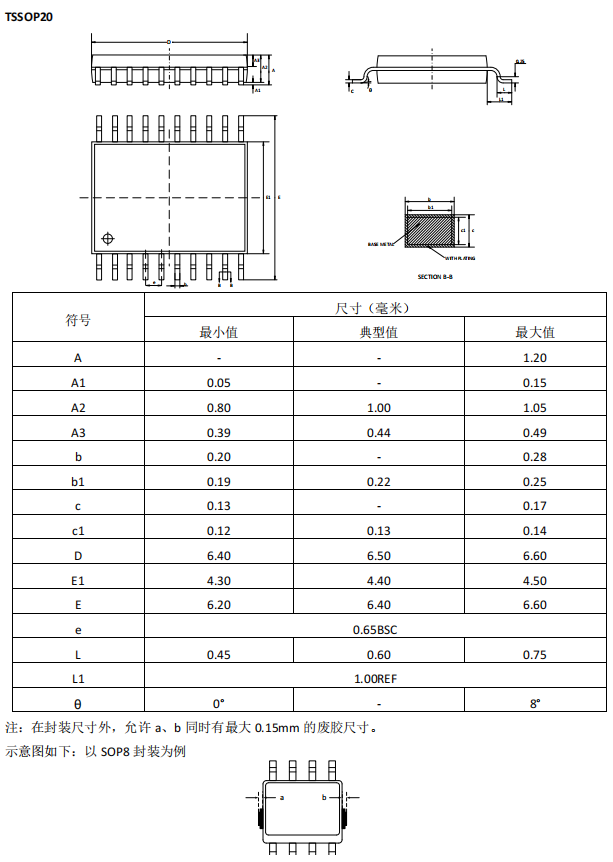

封裝外形圖

TSSOP16

——愛研究芯片的小王

審核編輯 黃宇

-

adc

+關注

關注

98文章

6452瀏覽量

544145 -

模數轉換器

+關注

關注

26文章

3144瀏覽量

126747

發布評論請先 登錄

相關推薦

MS5182N/MS5189N——16bit、4/8 通道、250kSPS、 SAR 型 ADC

MS51588N——16bit、8 通道、500kSPS、 SAR 型 ADC

MS5198T/MS5199T——低噪聲、低功耗、16/24 位 ∑-Δ ADC

MS5196T/MS5197T——低噪聲、低功耗、16/24 位∑-ΔADC

MS5194T/MS5195T——低噪聲、低功耗、24/16 位 ∑-Δ ADC

MS5192T/MS5193T——低噪聲、低功耗、16/24 位∑-ΔADC

ADS122C04 24位4通道2kSPS Δ-Σ ADC數據表

ADS112C04 16位4通道2kSPS Δ-Σ ADC數據表

ADS112U04 16位4通道2kSPS Δ-Σ ADC數據表

ADS1120 4通道、2kSPS、低功耗、16位ADC數據表

MS5046T/5047T/5048T/5048N——2kSPS、16bit Σ-Δ ADC

MS5046T/5047T/5048T/5048N——2kSPS、16bit Σ-Δ ADC

![RA6<b class='flag-5'>T2</b>的<b class='flag-5'>16</b>位模數轉換器操作 [10] 配置RA6<b class='flag-5'>T2</b> <b class='flag-5'>ADC</b>模塊 (7)](https://file1.elecfans.com/web2/M00/BB/1B/wKgZomWXtb6ACk_NAAARMuEl9ZA261.png)

評論