隨著摩爾定律的放緩與面臨微縮物理極限,半導體巨擘越來越依賴先進封裝技術推動性能的提升。隨著封裝技術從2D向2.5D、3D推進,芯片堆迭的連接技術也成為各家公司差異化與競爭力的展現。而“混合鍵合”(Hybrid Bonding)被視為芯片連接的革命性技術。

混合鍵合:優勢與挑戰并存

混合鍵合在先進封裝領域越來越受歡迎,因為它提供了功能相似或不同的芯片之間的最短垂直連接,以及更好的熱、電和可靠性結果。

其優點包括互連縮小到亞微米間距、高帶寬、增強的功率效率以及相對于焊球連接的更好擴展。但是,盡管一些芯片制造商在大批量制造(HVM)中確實擁有混合鍵合技術,但目前該工藝的成本太高,無法大規模采用。而且由于混合鍵合將前端和后端生產線連接在一起,因此芯片放置等組裝工藝現在必須滿足前端規格。

其他挑戰包括需要更好的銅平整度均勻性、更快的芯片到晶圓(D2W)放置和更好的精確性、多個鍵合和解鍵合載體帶來成本增加以及更低溫的退火能力。最后,必須降低顆粒水平,尤其是在芯片放置和切割步驟中。

Brewer Science首席應用工程師Alice Guerrero表示:“要成功地將混合鍵合進行大批量生產,需要解決與缺陷控制、對準精度、熱管理、晶圓翹曲、材料兼容性和工藝吞吐量相關的挑戰。”

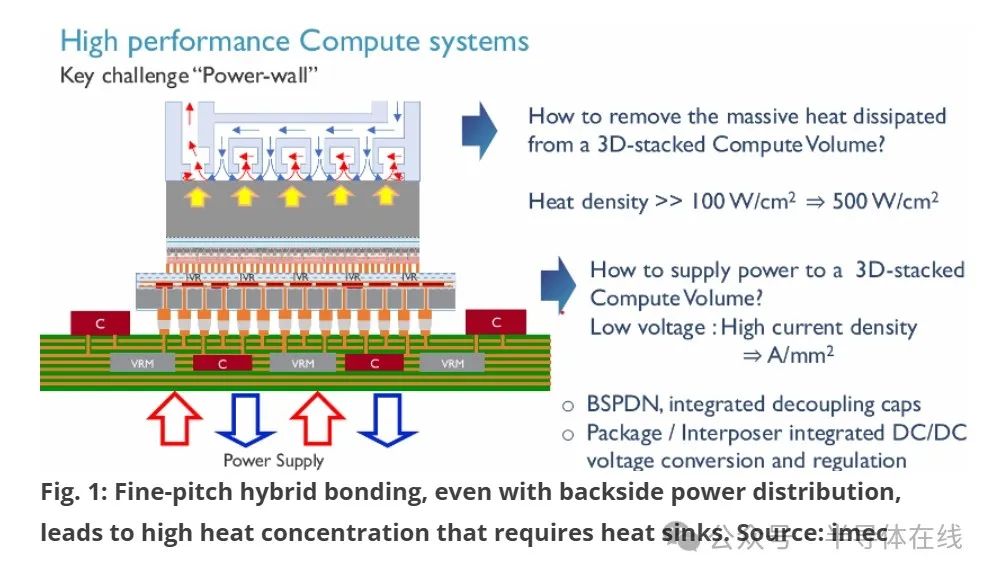

人工智能(AI)芯片組和模塊是混合鍵合和先進封裝的巨大驅動力。它們的高性能和高價格有助于推動行業發展。事實上,DRAM制造商正在評估從熱壓縮焊球鍵合轉向混合鍵合的凈收益(見圖1)。混合鍵合之后的下一代擴展是順序3D集成,其中鍵合甚至延伸到薄膜。

混合鍵合是將SoC分解為更模塊化的芯片組技術的關鍵推動因素。比利時微電子研究中心imec高級研究員、研發副總裁兼3D系統集成項目總監Eric Beyne表示:“我們對單片IC進行了某種分解,將擁有專門的技術,例如用于SoC、邏輯和I/O設備的邏輯和SRAM內存。”“我們需要推動一種看似單片或完全集成的解決方案,在這種解決方案中,你看不到不同設備之間的界限。我們必須打破這種障礙,即脫離芯片會在帶寬或能源使用方面造成的損失。”

高帶寬存儲器(HBM)制造商可以轉向混合鍵合或熔融鍵合(介電質到介電質),但存在缺點。“熔融鍵合目前確實是一種經過驗證的300mm晶圓制造工藝,這種鍵合對HBM非常有效。”EV Group(EVG)業務開發總監Thomas Uhrmann表示,“HBM目前堆疊12層芯片,制造商很快就會增加到16層。但由于每個芯片的性能并不相同,因此基本上最薄弱的環節限制了整個堆棧的性能。這不僅僅是產量問題,因為DRAM晶圓的產量非常好。速度分選實際上是一個很大的障礙。需要實施預排序才能進行補償。”

此外,混合鍵合還面臨一大挑戰——散熱。混合鍵合的新功率密度水平需要新的方法來釋放熱量。imec的研究人員利用3D打印技術開發了微流體冷卻技術。采用這種方法,通道的直徑很重要。

“在100~300μm時,水可以更自然地流入結構,產生直接流向芯片背面的水射流,像淋浴噴頭一樣直接冷卻系統。”Beyne說道。他指出,通過用交織的針翅結構對芯片背面進行額外修改,熱傳輸進一步減少,實現10W/㎡-K的傳熱系數值。“總體而言,冷卻可以將芯片溫度降低約50℃。”

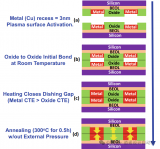

每次將混合鍵合工藝縮小到更小的線寬和間距時,鍵合強度和對準度都必須提高。鍵合強度需要更好,晶圓的平整度也需要更好,這在很大程度上取決于晶圓廠的化學機械拋光能力。

在制造過程中,焊料凸塊的間距為45μm。“晶圓對晶圓鍵合提供了一條通往400nm和200nm間距的路徑,但芯片對晶圓的鍵合稍落后于它們,在10~1μm的范圍內,這可能是該技術的最優點。”Beyne說道。

混合鍵合技術發展擁有強大的驅動力

晶圓對晶圓鍵合方案是用于CMOS圖像傳感器混合鍵合的首個技術,其中像素陣列芯片與邏輯芯片鍵合,以最大化背面照明面積。現在,其他應用也開始采用這種辦法,結合了處理器/緩存、3D NAND、MicroLED以及用于ChatGPT等大型語言模型(LLM)應用的AI模塊。

小芯片(Chiplet)集成在先進封裝中提供了新的靈活性。“在先進封裝中,你可以定制系統。”Tignis首席執行官Jon Herlocker表示,“你可以說,‘這部分邏輯非常復雜,所以我將在300mm代工廠的先進節點上進行這項工作,但我將從一個或多個更成熟的節點中獲取其他功能并將其放在同一個封裝上。’你可以有效地利用成熟節點及其可預測的高產量流程,從而降低整體風險。因此,一旦你決定進行先進封裝,那么從復雜芯片中取出盡可能多的東西并使用更成熟的技術,然后通過該先進封裝進行連接,就會帶來各種好處。”

電源管理和對功率效率的需求是芯片堆疊和新鍵合方法的額外驅動因素。混合鍵合使公司能夠創建“阻力最小的路徑”,這意味著更短的連接、更高的互連密度以及更大的散熱挑戰。

在這一發展過程中,需要降低半導體的功耗。可擴展性變得至關重要(見圖2)。“我們有功率墻,因此目前的能量密度通常為每平方厘米100W,但未來我們需要每平方厘米500W的能量密度,因此散熱市場將是一個相當大的增長。”Beyne說,“如果每平方毫米的電流為500A,那么通過微凸塊和焊料凸塊發送可能不是最佳方法,因為電流高達每平方毫米500A。“這可以通過將電源管理系統集成到設備附近來解決。我們可能不只是通過整個堆棧發送1.7V,但也許你會提出更高的電壓,例如48V,然后在封裝或板級使用DC/DC轉換來達到最終電壓。”

Uhrmann指出,測試增加了另一層復雜性。“雖然凸起的器件可以輕松測試,但混合鍵合就不那么容易了。你可以為混合鍵合創建一個雙層結構,因為這樣你就有了一個可以測試的底層,但你仍然需要在頂層有鍵合層。”

混合鍵合工藝如何實現?

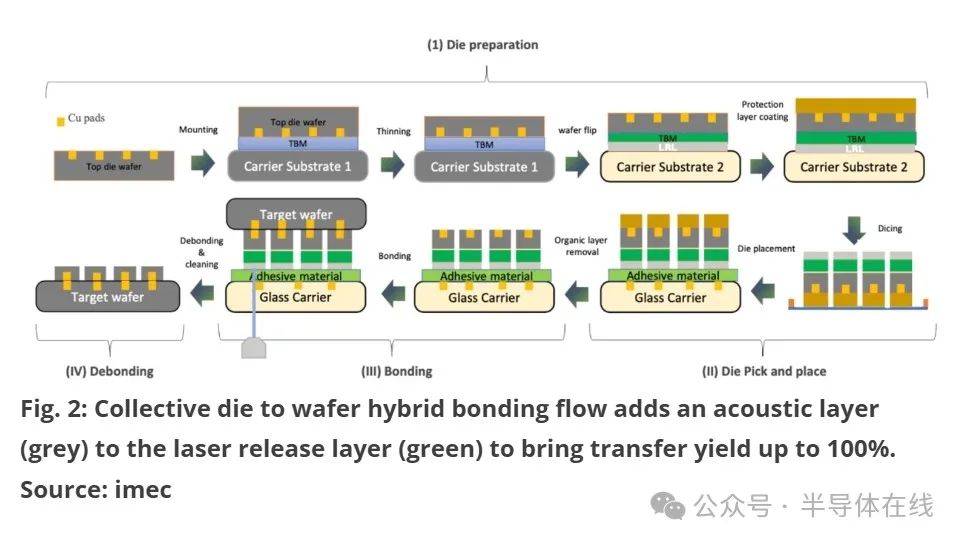

晶圓到晶圓(wafer-to-wafer)鍵合工藝比芯片到晶圓方案更成熟,但它有一個主要缺點——芯片必須大小相同。這對于處理器堆疊上的靜態隨機存取存儲器(SRAM)等應用效果很好,但如果要在設計和制造中獲得更大的靈活性,則需要采用芯片對晶圓鍵合,即將較小的芯片鍵合到較大的芯片上。在這里,集體D2W(die-to-wafer)鍵合的概念變得有吸引力(見圖2)。

如圖所示,該工藝使用多種載體,包括硅和玻璃。混合鍵合的流程將已經通過最終金屬化層處理的晶圓進行處理,然后執行類似于片上鑲嵌(damascene)工藝的步驟。介電蝕刻在SiCN介電層中形成方形腔體,然后通過電化學沉積(ECD)用阻擋金屬層、銅種子層和銅填充物填充這些腔體。隨后的化學機械拋光(CMP)工藝經過優化,可實現極高的晶圓間均勻性,從而產生盡可能光滑的介電表面,同時在銅墊區域形成小凹陷。

第二步是將晶圓安裝到載體上,然后對硅晶圓進行研磨/減薄。將晶圓翻轉并粘合到第二個載體上,然后涂覆光刻膠層以在膠帶框架上切割時保護表面。第三個載體粘合到該芯片場,然后去除光刻膠。將其放置在新載體上,準備與目標晶圓粘合,然后通過刀片、紅外激光或紫外光進行解粘合。

接下來,在真空室中進行的介電活化步驟使用等離子體來優化鍵合表面,與懸掛的Si-O-鍵結合。隨后使用DI水沖洗以水合介電層。第二片晶圓通過銅CMP處理進行面對面(或背對背)鍵合,處理方式與晶圓1相同,然后與晶圓1對齊并鍵合。然后,對晶圓在350℃的爐管中退火兩個小時。

現在,鍵合可以為下一個晶圓減薄。imec和其他公司已經證明,非常薄(50μm)到非常厚(775μm)的芯片可以從臨時載體轉移到目標晶圓,轉移率和鍵合率均為100%。對于超薄芯片,硅基是首選。玻璃基板確實允許紫外線解鍵合,但它們與前端工具不兼容。

Imec、Brewer Science和Suss MicroTec最近證明,集體芯片到晶圓鍵合流程可以擴展到三到四個晶圓。在有機激光釋放層中添加了所謂的聲學層,以吸收解鍵合工藝引起的沖擊波,這可能會損壞芯片邊緣。值得注意的是,通過紅外顯微鏡測量的對齊是倒裝芯片工具和鍵合工具對齊的組合功能。

轉移良率和鍵合良率是關鍵指標,在完全優化的制造和組裝工藝下可達到100%。將集體芯片到晶圓流程擴展到兩個、三個和四個晶圓會使工藝變得復雜,因為在加工過程中會出現翹曲、粘合劑去除不完全以及芯片損壞等狀況。

載體基板的選擇基于臨時鍵合材料(TBM)及其解鍵合能力。Brewer Science公司的Guerrero表示:“粘合劑將芯片暫時粘合到TBM上的能力取決于其機械、熱和化學特性以及芯片表面條件的控制。”“通常,粘合頭溫度和載體(卡盤)溫度之間的相互作用將根據TBM的熱特性進行調整,以實現最佳芯片鍵合效果。激光解鍵合因其最小的機械力而最適合在芯片解鍵合中使用。”

Guerrro指出,薄芯片存在芯片損壞的風險,但這些風險可以通過材料和工藝設計來減輕。“機械解鍵合是一種更具成本效益的解決方案,因為與激光相比,機械解鍵合的設備成本更低,但其應用范圍并不廣泛。”Guerrro提到,“紫外線解鍵合并不普及,在載體層面實施起來也很有挑戰性。紫外線解鍵合膠帶隨處可見,是最經濟的解鍵合方法,但它在處理小于50μm的芯片時會受到限制。”

工具清潔對于防止鍵合界面出現空洞至關重要,這在C-SAM圖上顯示為白點。“有趣的是,由于清潔方式和工藝,一些顆粒仍會在表面上移動。所以這并不意味著你不能有一個顆粒。”Adeia工程高級副總裁Laura Mirkarimi認為,“這是一個可以處理一些顆粒的工藝,但不移動的大顆粒會阻止它鍵合。鍵合前沿在晶圓鍵合中移動得非常快,即使在芯片對晶圓鍵合中也是如此,所以它實際上是一種自發鍵合,需要通過仔細處理表面來管理。”

這就解釋了為什么在整個混合鍵合流程中必須優化多個清潔步驟。

EV Group開發了一種新型無機粘合劑鍵合和激光釋放工藝,該工藝使用硅載體晶圓,提供100nm的TTV、更好的幾何穩定性和更高的熱導率。

后者在硅載體上工藝還允許硅載體重復使用,從而減少了工藝步驟并降低了擁有成本。“我們使用了一種完全不同的釋放層,一種與前端兼容的無機材料。”EVG的Urhmann說,“但硅載體可以廣泛使用。所以現在你可以擁有與熔融鍵合一起工作的載體,你還可以攜帶混合鍵合晶圓或非常薄的器件、外延層。因此,它將整個產品組合擴展到前端轉移,但并不局限于此。高精度意味著遠低于100nm。”

這樣的發展也會影響可持續性。“水循環和保持水清潔的成本很高。”EVG的Urhmann說,“通過研磨和拋光會產生大量的顆粒,甚至是納米顆粒,所以過濾成本很高。”

雖然有很多關于面對面鍵合的討論,但許多工藝需要背對背鍵合,這意味著你首先需要把它放在載體上并減薄,然后轉移到另一個載體上。”Urhmann提到,“所以你有薄的器件晶圓,然后如果需要減薄另一個載體晶圓,你就得犧牲兩片晶圓,這是不劃算的。”

直到最近,具有HVM能力的倒裝芯片鍵合機的對準公差為±3μm(3sigma),但精度已提高到1μm。Adeia的Mirkarimi說:“對準精度的經驗法則是,鍵合機的精度必須是焊盤直徑的0.1~0.25倍,或者對于1μm焊盤,鍵合機的精度為100~250nm。”最近,多家供應商已經開發并提供具有亞微米精度的鍵合機,包括BESI(BE Semiconductor)和Suss MicroTec。

“盡管D2W HB具有優勢,但它在組裝方面面臨兩大挑戰,”英特爾的Feras Eid及其同事說。“首先是對準,當前甚至下一代鍵合設備都無法滿足亞1μm間距的放置要求。第二個是吞吐量,即使在當今相對寬松的間距(例如9μm)下,D2W HB連接步驟也是整個HB流程中最慢且最昂貴的步驟。”

因此,英特爾和其他公司正在探索拾取和放置的替代方案,例如流體自對準,它使用微小的水珠和兩個芯片上的引導圖案來自對準結構。該工藝由CEA-Leti和英特爾聯合開發。重要的是,芯片到晶圓可能在x、z和theta(旋轉)方向上錯位。在特定條件下,液體限制可將芯片到晶圓的錯位降低到200nm。雖然該工藝還不適合生產,但它有潛力用估計10倍的產量提高取代耗時的芯片放置。

盡管半導體行業已經證明混合鍵合適用于各種應用,但人們仍在不斷減少晶圓步驟和成本。雖然制造AI芯片的公司可以負擔得起更復雜的工藝,但要使該技術滲透到更便宜的系統中,它必須更簡單。

直接裸晶對晶圓(die-to-wafer)鍵合工藝比集體裸晶到晶圓方法簡單得多,后者只將已知良好的裸晶放置在重建的晶圓上,然后將其鍵合到另一個晶圓上。然而,直接鍵合容易受到污染,因為芯片放置工具直接接觸敏感的鍵合表面,需要非常高的工具清潔度,甚至可能需要原位芯片清潔能力。

巨頭紛紛搶進布局HBM將是下一個里程碑

事實上,盡管讓先進封裝備受關注的是AI芯片,但是第一個采用混合鍵合的商用化產品其實是搭載于智能手機的圖像傳感器(CIS)。索尼2016年為三星旗艦手機Galaxy S7 Edge生產的IMX260 CIS,就采用混合鍵合技術,將像素層堆迭于ISP(圖像信號處理器)上,實現了接點間距僅9μm左右的突破。

除了CIS,高端CPU是另外一個采用混合鍵合的領域,臺積電的3DFabric技術已實現該領域的商業化。第一個采用混合鍵合技術的CPU是AMD于COMPUTEX 2021發布的3D V-Cache,即臺積電3D封裝-SoIC解決方案Cu / Oxide Hybrid Bonding高密度封裝,將SRAM堆迭于運算單元CCX上,讓CPU獲得更多SRAM容量。相較微凸塊(Microbumps),3D V-Cache混合鍵合加上TSV,讓芯片接點密度提升15倍,互聯能效超過三倍。

而英特爾也在2020年的Architecture Day發布了采用混合鍵合的先進封裝技術,計劃用于3D封裝Foveros Direct,當時宣布同年試產混合鍵合芯片。據悉,英特爾有望今年在邏輯芯片與互聯器上先采用混合鍵合。英特爾白皮書表示,Foveros Direct采用晶粒對晶圓混合鍵合,間距預估9μm,第二代產品縮小至3μm。

此外,需多層堆棧的HBM產品領域也在積極開發混合鍵合新產品。HBM通過堆棧DRAM層數提高數據處理速度,通過TSV加上填充物連接數層DRAM層。業內消息顯示,韓國DRAM芯片大廠三星和SK海力士都計劃在即將推出的新一代HBM4中采用新的混合鍵合技術。SK海力士曾在其第三代8層堆疊的HBM2E上進行過測試,使用混合鍵合制程后,通過了所有可靠性測試;三星今年4月使用子公司Semes的混合鍵合設備制作了16層的HBM樣品,并表示芯片運作正常。此外美光此前在COMPUTEX 2024上表示,公司也正著手開發HBM4,會考慮采用包括混合鍵合在內等相關技術,目前一切都在研究中。市場調查機構TrendForce集邦咨詢最新研究顯示,三大HBM原廠正在考慮是否于HBM4 16hi采用混合鍵合,并已確定將在HBM5 20hi世代中使用這項技術。

結論

設備制造商、設備公司和材料供應商正在合作采用多種方法,以找到以較低成本實現最佳性能的工藝流程,以便非前沿設備能夠充分利用混合鍵合所提供的優勢。但新技術正在經歷成長的煩惱。它需要新程序、新工具能力,甚至一些新工藝。

此外,不同的應用有不同的需求,因此很可能會出現幾種方法成為領導者。不過,就目前而言,混合鍵合工藝和供應鏈處于不斷變化之中,這在新技術中并不罕見。

-

芯片

+關注

關注

454文章

50460瀏覽量

421965 -

英特爾

+關注

關注

60文章

9900瀏覽量

171548 -

先進封裝

+關注

關注

1文章

379瀏覽量

224

原文標題:先進封裝爭奪戰:混合鍵合成“芯”寵

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

AI網絡物理層底座: 大算力芯片先進封裝技術

先進封裝技術激戰正酣:混合鍵合成新星,重塑芯片領域格局

先進封裝技術激戰正酣:混合鍵合成新星,重塑芯片領域格局

評論