超聲無損檢測技術是根據材料缺陷所顯示的聲學性質對超聲波傳播的影響來探測其缺陷的方法。利用該技術可以測量各種金屬、非金屬、復合材料等介質內的裂縫、氣孔、夾雜等缺陷信息。由于超聲波檢測具有穿透力強,檢測靈敏度高等優點,因而在航空航天、冶金造船、石油化工、鐵路等領域起著廣泛的作用。一般采用超聲無損檢測技術的超聲探傷儀有模擬式和數字式之分,隨著計算機技術、微電子技術及數字信號處理技術的發展,傳統的模擬式超聲探傷儀正逐漸被功能先進的數字式超聲探傷儀所取代。

超聲波的回波信號是高頻信號,其中心頻率最高達到20 MHz以上,常用的超聲波探頭中回波信號的頻率一般為2.5~10 MHz,要使這樣的高頻信號數字化,系統就對模/數轉換電路提出了很高的要求。根據Shannon采樣定理和Nyquist采樣準則,在理想的數據采集系統中,為了使采樣信號不失真地復現輸入信號,采樣頻率至少是輸入信號最高頻率的兩倍。在實際使用中,為保證數據采集的準確度,應增加在每個輸入信號周期內的采樣次數,一般每周期采樣7~lO次。有些系統對采樣信號頻率的要求更高。現有的模/數轉換電路方案在可靠性、功耗、采樣速度和精度上都存在諸多不足,不能滿足某些實際情況的需要,而大規模集成電路技術的發展為設計高速、高精度、高可靠性、低功耗的超聲信號采集方案提供了可能性。本文設計了一種采樣速率達100 MHz的超聲波采集模塊,并通過FPGA對采樣數據進行壓縮后進行數據緩存。

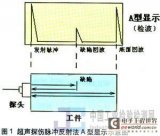

1.數字式超聲探傷儀原理

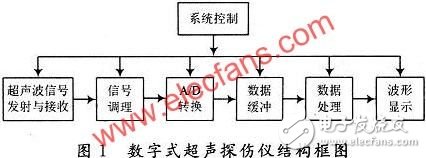

數字式超聲探傷儀結構框圖如圖1所示。

數字化超聲探傷儀一般包括超聲發射單元、超聲接收單元、信號調理單元(包括放大、檢波、濾波等模擬信號處理環節)、模數(A/D)轉換單元、數據緩沖單元、數據處理單元、波形顯示單元以及系統控制與輸入/輸出單元(包括通信、鍵盤操作、報警等)。本文主要討論數字式超聲探傷儀中高速采集的關鍵技術與實現方法,涉及到A/D轉換單元和數據緩沖單元。

2 高速度、高精度采樣硬件結構

2.1 數據采集模塊的結構框圖

圖2給出本文數據采集模塊的硬件結構框圖,它由高速A/D數據轉換器、FPGA、時鐘電路、復位電路及電源電路組成。其中,A/D數據轉換器負責對模擬信號進行采集轉換;FPGA負責采集控制、數據壓縮及數據緩沖。下面對A/D數據轉換器及FPGA進行介紹。

2.2 AD9446簡介

AD9446是一種16 b ADC,具有高達100 MSPS的采樣率,同時集成有高性能采樣保持器和參考電壓源。同大多數高速大動態范圍的ADC芯片一樣,AD9446也是差分輸入,這種輸入方式能夠很好地抑制偶次諧波和共模信號的干擾。AD9446可以工作在CMOS模式和低電壓差分信號(LVD-S)模式,通過輸出邏輯控制引腳進行模式設置。另外,AD9446的數字輸出也是可選擇的。可以為直接二進制源碼或二進制補碼方式。在實際電路的PCB設計中,由于AD9446是對噪聲敏感的模擬器件,所以在具體PCB設計時需做到以下幾個方面:A/D模擬電源單獨供電,模擬地與數字地單點接地,差分輸入線等長,采用精確的參考電壓源等。

2.3 采集控制、數據壓縮及數據緩沖的FPGA實現

FPGA主要實現整個模塊的數據采集控制、數據壓縮及數據緩沖等功能。文中FPGA采用Xilinx公司的Spartan3E系列(XC3S500E)。這款FPGA芯片功能強大,I/O資源豐富,能夠滿足很多實際場合的需要。下面對其中數據采集控制、數據壓縮及數據緩沖FIFO的設計做出介紹。

2.3.1 數據采集控制

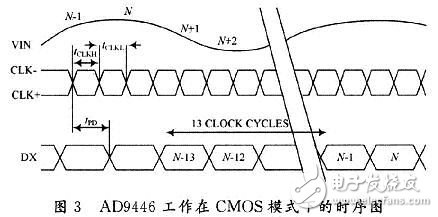

AD9446芯片的控制時序與傳統的低速A/D有所不同,它完全依靠時鐘來控制其采樣、轉換和數據輸出。AD9446通常在CLK第一個時鐘的上升沿開始采樣轉換,并在經過延遲tpd后,開始輸出數據。而數據則在第13個時鐘到來時才出現在D15~D0端口上。圖3是AD9446工作在CMOS模式下的時序圖。

數字時鐘管理單元(DCM)是FPGA內部管理、掌控時鐘的專用模塊,能完成分頻、倍頻、去抖動和相移等功能。通過FPGA的DCM可以很方便地對AD9446的時鐘輸入信號進行掌控。在實際電路中需要注意的是要做到DCM倍頻輸出的時鐘信號與AD9446的時鐘輸入信號保持電平匹配。

下面給出調用DCM后時鐘輸出的VHDL語言描述:

2.3.2 數據壓縮

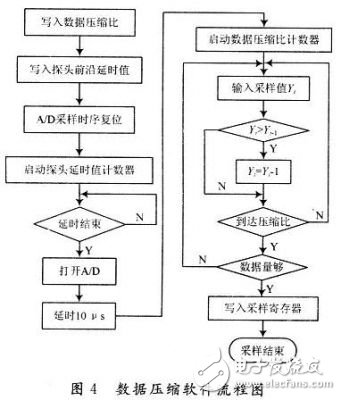

數據壓縮處理是對射頻信號高速采樣后進行前置處理的重要環節之一,需要在保持超聲回波信號基本特征前提下對采樣數據進行在線壓縮,而且要求壓縮后的數據與原始采樣信號的包絡相吻合。為此,在每次壓縮過程中,只取采樣所得的最大值,而舍棄其他采樣值。FPGA將計算所得采樣數據的壓縮比、探頭前沿延時計數值等數據送入相應的鎖存器,然后發出時序復位命令并發射,啟動探頭延時計數,延時到后啟動A/D采樣,同時壓縮比計數器開始計數,在時鐘信號的控制下,每采樣一次,壓縮比計數器減1,并將當前采樣值與前次采樣值比較,如大于則保存,否則舍棄,直至壓縮比計數到零后,得到一個有效的采樣數據。同時壓縮比計數器自動復位,重新開始計數,其工作流程如圖4所示。

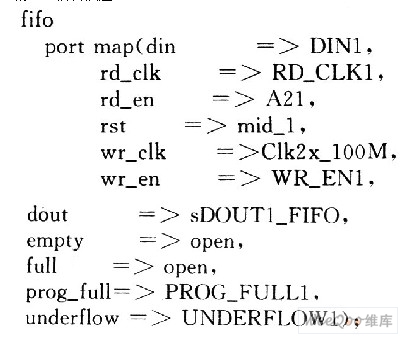

2.3.3 數據緩沖

為了解決前端數據采集與后端數據傳輸在速率上的不匹配問題,在FPGA內部設置一塊數據緩沖FIFO,大小為8K×16 b,壓縮后的數據直接存儲到FIFO中,而微處理器對FIFO中數據的讀取通過中斷方式完成。數據緩沖FIFO通過core generator例化,只需要少量的讀/寫控制邏輯就可以使FIFO正常工作,而且FIFO的大小可以在FPGA提供的RAM位數范圍內靈活設置。下面給出例化后的FIFO的VHDL語言描述:

保存在FIFO中的數據通過這些邏輯控制端口便于微處理器對其進行讀取、清零等操作。

3 結語

設計的基于AD9446的數據采集模塊采用FPGA實現數據采集控制、數據壓縮及數據緩沖等功能,簡化了硬件電路,提高了模塊的可靠性和穩定性,并有利于模塊的功能升級。同時采用高速高精度模/數轉換器滿足了數字式超聲波探傷系統對數據采集精度方面的要求。另外,FP-GA對數據進行的預處理,方便了微處理器對數據的調用和后處理。

-

超聲波

+關注

關注

63文章

2990瀏覽量

138229 -

高頻信號

+關注

關注

1文章

134瀏覽量

21666

發布評論請先 登錄

相關推薦

數字式超聲波探傷儀中高速數據采集模塊設計

ATA-2000系列 高壓放大器——超聲波探傷測試中的典型應用

怎么設計A超數字式探傷系統?

根據超聲波無損探傷儀系統原理在ARM平臺上是如何實現的

70KHZ超聲波換能器傳感器探頭DYA-70-03A相關資料分享

超聲波探傷儀的主要技術參數及檢測方法

數字超聲波探傷儀焊縫探傷實例和DAC曲線繪制探傷步驟

數字式超聲波探傷儀中高速數據采集模塊的設計

數字式超聲波探傷儀中高速數據采集模塊的設計

評論