晶振作為時鐘電路中必不可少的信號傳遞者,單片機要想正常運作就需要晶振存在。因此,在電子電路設計中也少不了晶振的參與。一個好的晶振電路設計,是能夠為電子提供最好的空間利用率,同時發揮最大的功能性作用。

振蕩原理

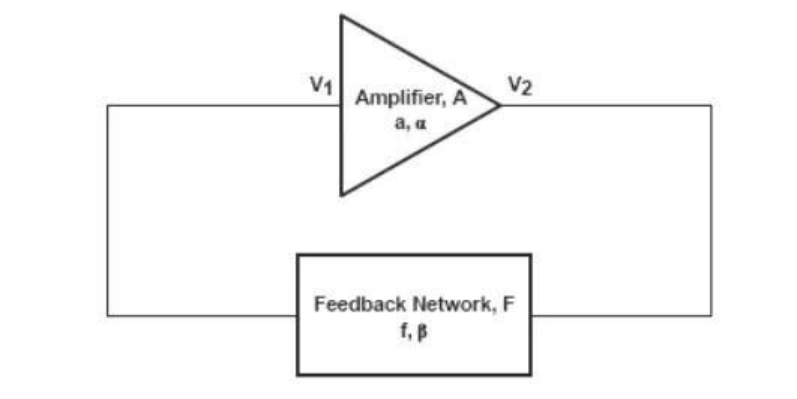

振蕩器是一個沒有輸入信號的帶選頻網絡的正反饋放大器。從能量的角度來說,正弦波振蕩器是通過自激方式把直流電能轉換為特定頻率和幅度的正弦交變能量的電路。對于任何一個帶有反饋的放大電路,都可以畫成下圖所示結構:

▲圖1 振蕩器

當增益滿足∣f∣×∣a∣≥1,且相位條件滿足α+β=2πn時,構成正反饋環路,起振條件得以滿足。上圖即構成一個振蕩器。

晶振原理

當在晶體兩端加上一定的交變電場,晶片就會產生機械形變,石英晶體振蕩器是利用石英晶體的壓電效應制的一種諧振器件,若在石英晶體的兩個電極上加一電場,晶片就會產生機械變形。同時這個機械形變又會產生相應的交變電壓,并且其特征頻率下的振幅比其他頻率點的振幅大得多。根據這個特點,為了得到低的起振電壓和短的起振時間,在晶體兩端施加的交變電壓的頻譜能量應主要集中在晶體的特征頻率附近。

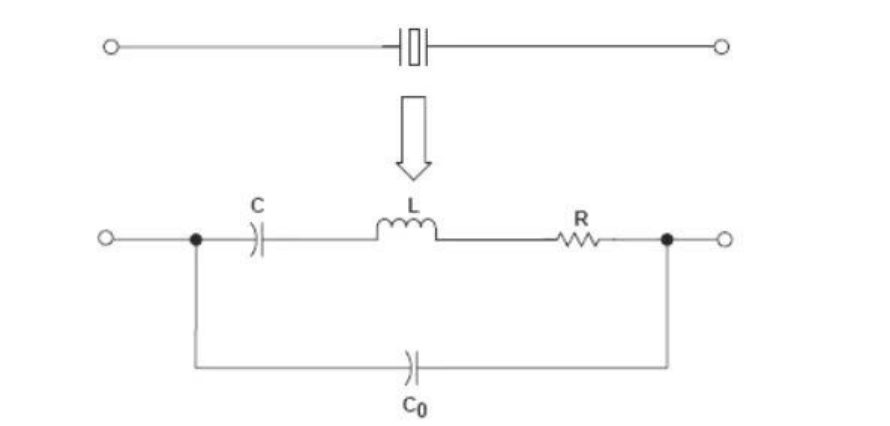

▲圖2 晶振等效電路

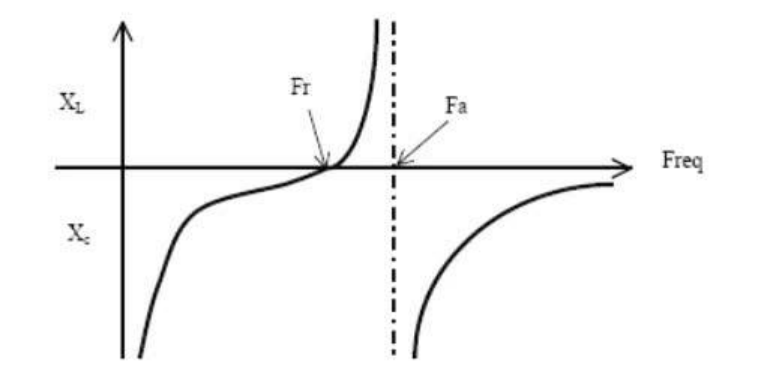

在一般情況下,晶片機械振動的振幅和交變電場的振幅非常微小,但當外加交變電壓的頻率為某一特定值時,振幅明顯加大,比其他頻率下的振幅大得多,這種現象稱為壓電諧振。石英晶體振蕩器的等效電路如圖2所示。當用石英晶體組成并聯諧振電路時,晶體表現為感性,其等效品質因數Q值很高。等效阻抗頻率特性如圖3所示。

▲圖3 晶振等效阻抗

圖3中,Fr為串聯諧振點。在頻率為Fr = 1/(2π√LC)時,圖2中串聯的L、C諧振,串聯支路等效為一個純電阻。Fa為并聯諧振點,此時串聯支路等效為電感,與并聯的C0諧振,Fa= Fr√1+C/C0。此時等效阻抗趨于無窮大。通常這兩個頻率點之間的差值很小。

總的來說,可以認為晶振在串聯諧振時表現為電阻,在并聯諧振時表現為電感。這里建議設計時采用并聯諧振。

電工學上這個網絡有兩個諧振點,以頻率的高低分其中較低的頻率是串聯諧振,較高的頻率是并聯諧振。

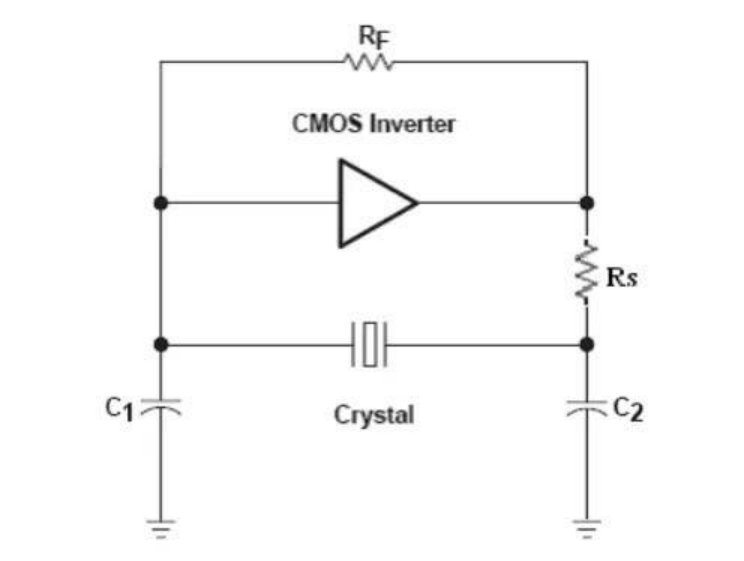

皮爾斯振蕩器

倒相器作為放大器,同時提供180度的相移。而晶振及負阻電容作為反饋回路,提供剩下的180度相移。RF為反饋電阻,用來決定倒相器的直流工作點,使之工作在高增益區(線性區)。這個電阻值不能太小,否則會導致環路無法振蕩。該電路利用晶振的并聯諧振,由于并聯諧振與C0有關,會受寄生電容影響,因此增加負載電容C1、C2,可減小C0對諧振頻率的影響。同時C1、C2的加入會影響起振時間和振蕩頻率的準確度。負載電容的選擇,應根據晶振供應商提供的datasheet的數值選擇。在許可范圍內,負載電容值越低越好。容值偏大雖有利于振蕩器的穩定,但將會增加起振時間。

▲圖4 皮爾斯振蕩器電路

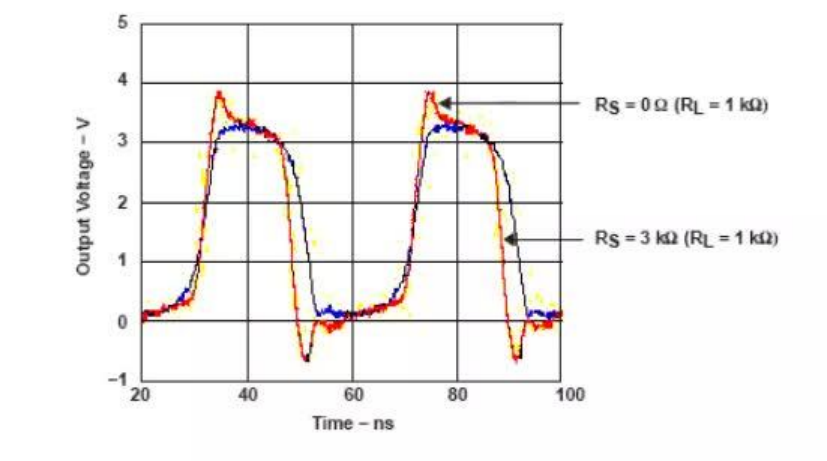

Rs用于抑制高次諧波,從而使振蕩器獲得較為純凈的頻譜。Rs的值若太小的話,可能會導致晶振的過分驅動(overdrive),導致晶振損壞或壽命減短。通常取Rs=XC2。Rs的影響可以由下圖看出。

▲圖5 Rs的影響(來自參考資料)

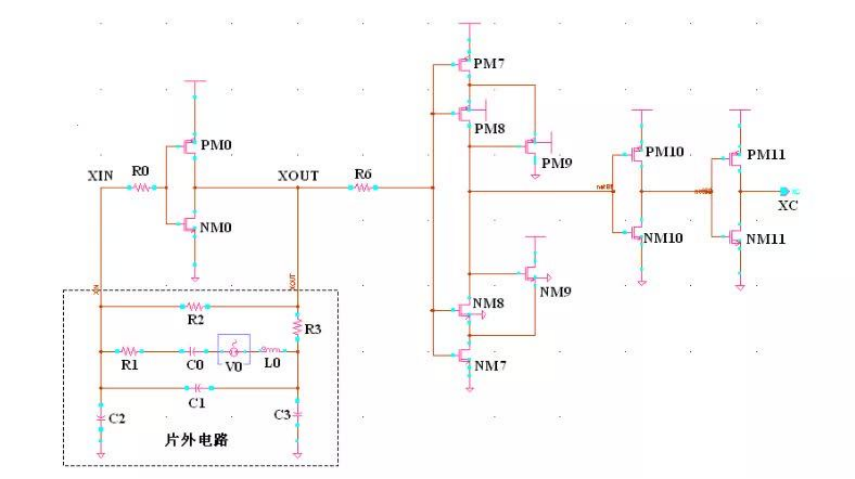

電路設計

如圖6,PM0和NM0構成倒相器,與片外電路共同組成振蕩環路。PM7~PM9和NM7~NM9組成施密特觸發器,對波形進行整形和放大。輸出信號再經過兩級倒相器,以提高輸出級驅動能力。

▲圖6 xtal電路原理圖

仿真結果演示

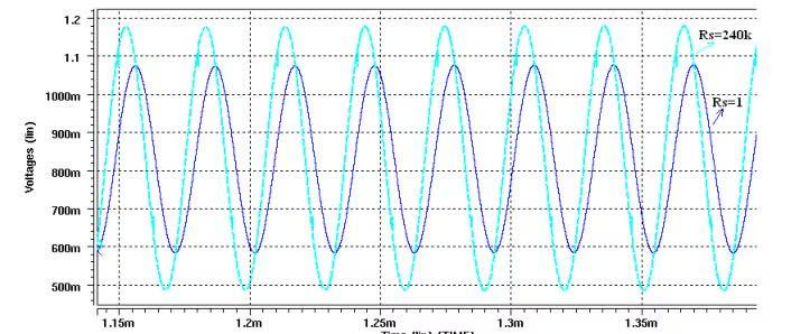

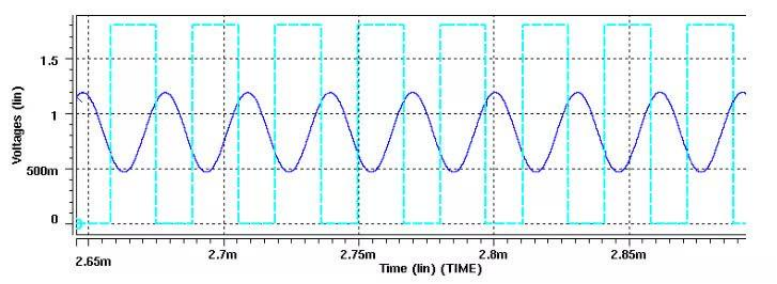

Rs小的時候,在同樣的激勵電壓下,波形幅度比Rs大的情況小很多,導致XC輸出為一根直線。

▲XOUT

▲圖7 XOUT和XC的波形圖

晶振設計注意事項

在低功耗設計中晶體的選擇非常重要,尤其帶有睡眠喚醒的系統,往往使用低電壓以求低功耗。由于低供電電壓使提供給晶體的激勵功率減少,造成晶體起振很慢或根本就不能起振。這一現象在上電復位時并不特別明顯,上電時電路有足夠的擾動,很容易建立振蕩。在睡眠喚醒時,電路的擾動要比上電時小得多,起振變得很不容易。在振蕩回路中,晶體既不能過激勵(容易振到高次諧波上)也不能欠激勵(不容易起振)。

晶體的選擇應考慮以下幾個要素:諧振頻點、負載電容、激勵功率、溫度特性、長期穩定性。換句話說,晶振可靠性工作不僅受到負載電容的影響。對于負載電容的選擇,應根據晶振供應商提供的datasheet的數值選擇。在許可范圍內,負載電容值越低越好。容值偏大雖有利于振蕩器的穩定,但將會增加起振時間。有的晶振推薦電路甚至需要串聯電阻RS,它一般用來來防止晶振被過分驅動。過分驅動晶振會漸漸損耗減少晶振的接觸電鍍,這將引起頻率的上升,造成頻率偏移,加速老化。

設計經驗總結

01首先要選擇一個低的等效串聯電阻的晶體。晶體串聯電阻低有利于解決起振的問題。因為低的晶體等效阻值有利于增加環路增益。

02通過縮短印制電路板的連線間距來減低寄身電容。從而可以幫助解決起振問題和晶振頻率穩定度的問題。

03應該保持對晶振應用溫度和電壓范圍保持監控,從而保持晶體起振頻率有必要的話要調整電容電阻的值。

04想要得到最佳效果,晶振設計應該采用Vdd峰峰值的至少40%作為驅動時鐘反相器的輸入信號。僅僅調節晶振兩端是不能達到這一要求的。我們也可以參考晶振制造商的使用說明來獲得關于晶振設計進一步的幫助。

05對于推薦最優化的R1的阻值可以這樣得到,首先計算電容C1,C2的值,然后在R1的位置上設置一個電位計,將電位計的初始值設置為XC1。這樣可以通過調節電位計來保證在所需要的頻率下起振以及維持晶體穩態振蕩。

-

振蕩器

+關注

關注

28文章

3812瀏覽量

138868 -

晶體

+關注

關注

2文章

1339瀏覽量

35368 -

晶振

+關注

關注

34文章

2824瀏覽量

67900 -

晶體振蕩器

+關注

關注

9文章

616瀏覽量

29057 -

揚興科技

+關注

關注

1文章

126瀏覽量

1765

發布評論請先 登錄

相關推薦

晶振電路設計訣竅,工程師必備技巧!

晶振電路設計訣竅,工程師必備技巧!

評論