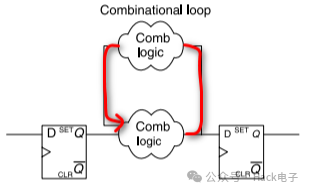

什么是組合邏輯環路?

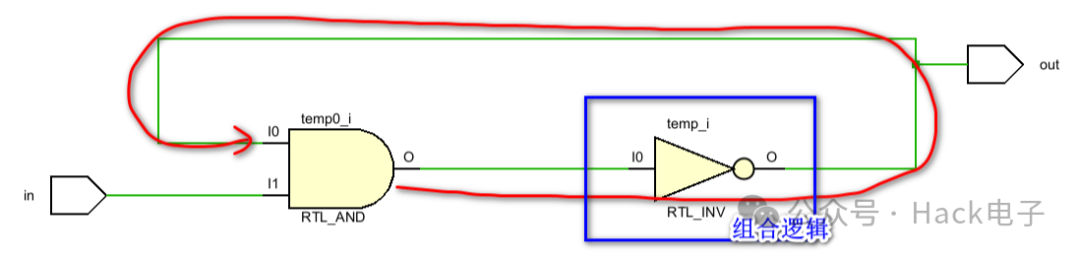

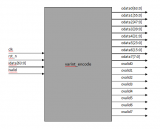

組合邏輯環路(Combinational Loops):指組合邏輯的輸出信號不經過任何時序邏輯電路(FF等),而直接反饋到輸入節點,從而構成的電路環路。

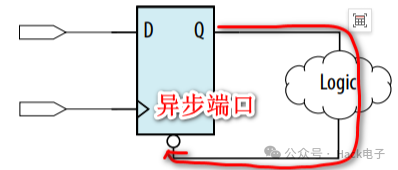

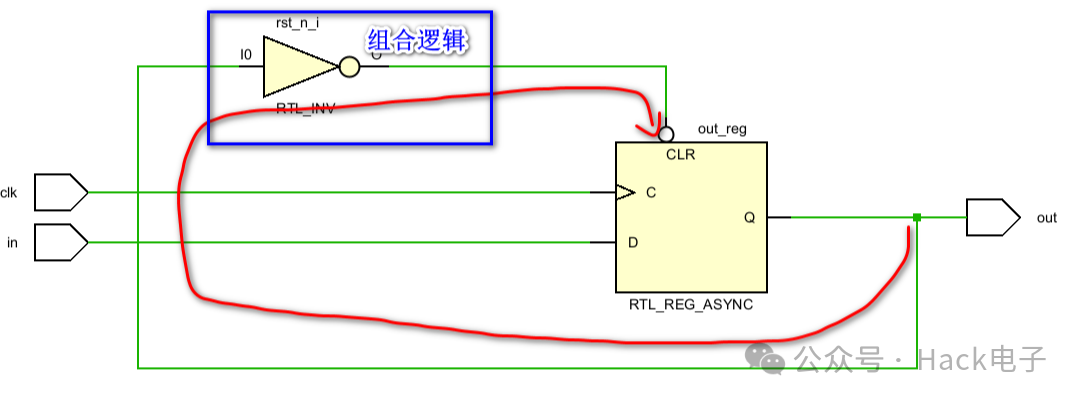

此外,如果直接將寄存器的輸出端通過組合邏輯反饋到該寄存器的異步端口(異步復位或異步置位),也會形成組合邏輯環路。

為什么要避免組合邏輯環路?

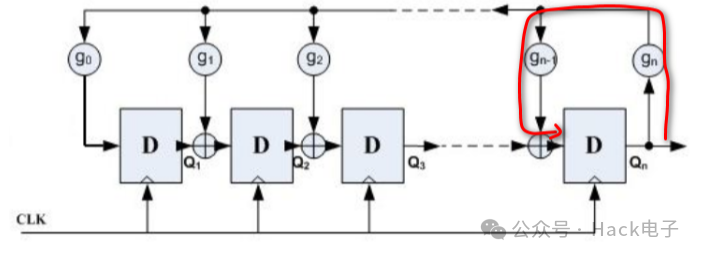

在FPGA設計中,絕大多數的應用場景都不需要使用組合邏輯環路,我暫時能想到的例外只有隨機數發生器(評論區可以補充一下)。

在實踐中,避免使用組合邏輯環路主要是因為它的特性所導致的危害:

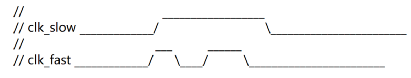

組合邏輯環路違反了同步設計原則,容易振蕩,從而導致整個設計不穩定和不可靠。

組合邏輯環路的行為功能取決于該環路上的延遲(邏輯延遲和布線延遲),一旦延遲發生變化,整個設計的行為功能將變得無法預測。

組合邏輯環路的振蕩將導致EDA軟件做無窮無盡的計算。為了完成這種計算,EDA軟件將會切割環路。不同的EDA軟件的切割方式不盡相同,這可能會與設計者的設計目的相違背,從而導致邏輯功能錯誤。

組合邏輯環路無法進行靜態時序分析(STA),可能會出現時序違例,或者導致STA過程時間過長。

什么情況會導致組合邏輯環路?

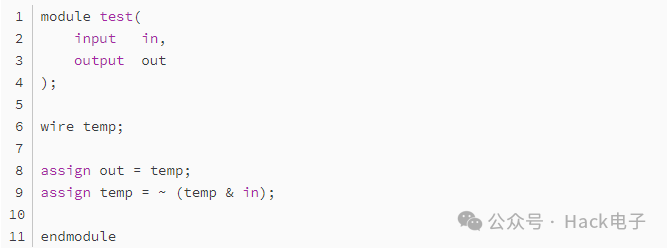

情況1:組合邏輯的輸出信號僅經過組合邏輯電路后又反饋到了輸入節點。比如下面的代碼:

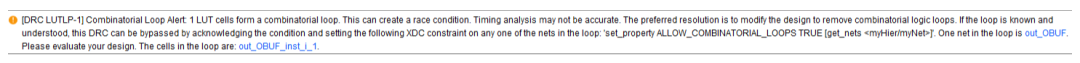

這樣的設計在Vivado中不會報錯,但會報嚴重警告(Critical warning)。

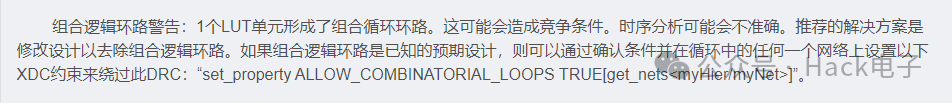

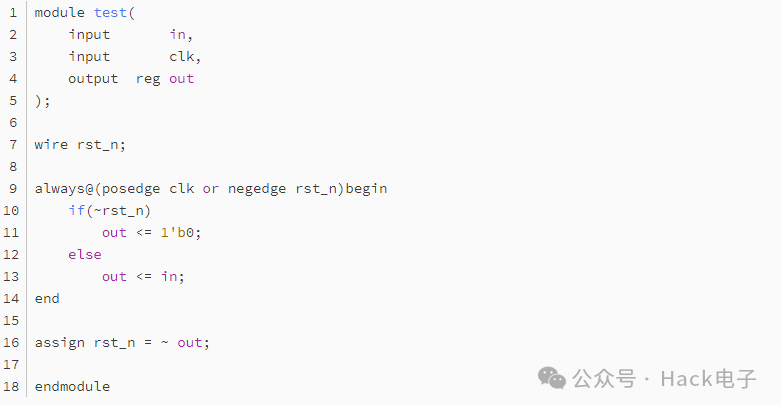

情況2:寄存器的輸出端通過組合邏輯直接反饋到該寄存器的異步端口(異步復位或異步置位)。比如下面的代碼:

這種情況所導致的組合邏輯環路在實踐中還是比較少出現的,因為一般情況下,寄存器的異步端口都是直接由模塊外部連接的信號所驅動。

如何處理組合邏輯環路?

最重要的一點:一定要堅決避免組合邏輯環路!現在的EDA工具基本上都可以把組合邏輯環路識別出來,并報錯或者報警告。寫完RTL代碼后請一定要記得看EDA工具的報告的錯誤和警告信息Message!

組合邏輯環路的避免首先應該通過良好的編碼習慣來避免。上述的兩種示例代碼就是典型的錯誤,請不要在設計中使用類似的代碼。

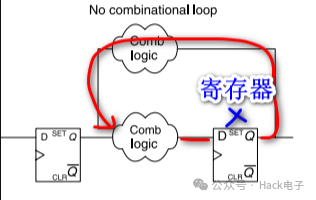

如果出現了組合邏輯環路且當前設計修改困難,那么請修改你的RTL代碼--通過添加寄存器的方式來切斷反饋回路。就像這樣:

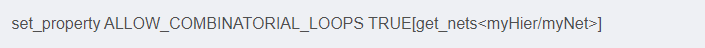

如果組合邏輯環路的出現是符合預期設計目的的(比如隨機數發生器),想將其保留該如何操作?只要在XDC約束文件中添加這一句即可:

什么是語言模板?

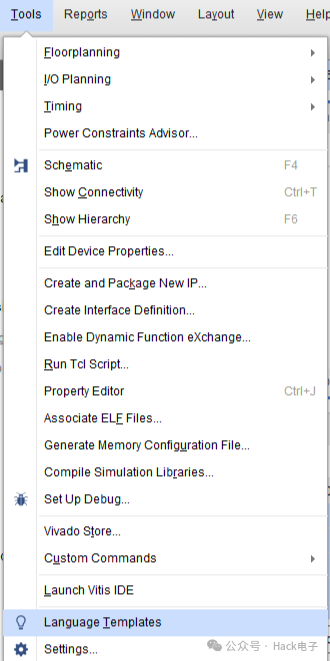

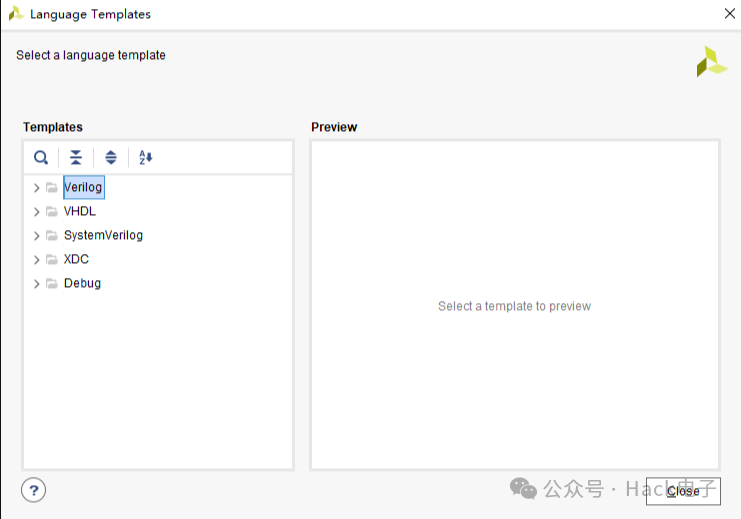

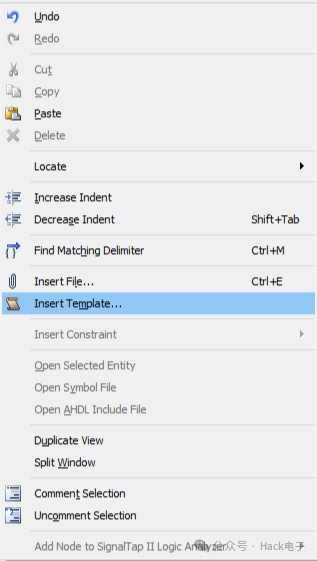

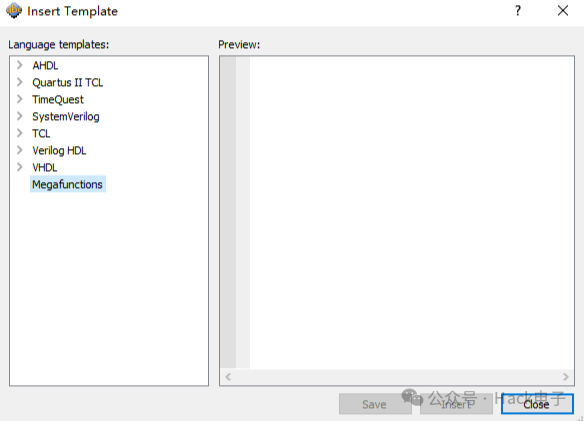

不論是Xilinx的Vivado,還是Altera的Quartus II,都為開發者提供了一系列Verilog、SystemVerilog、VHDL、TCL、原語、XDC約束等相關的語言模板(Language Templates)。

在Vivado軟件中,按順序點擊Tools----Language Templates,即可打開設計模板界面。

在Quartus II軟件中,需要設計文件(.v文件等)的需要處點擊右鍵,然后點擊Inset Templates,即可打開模板界面。

設計模板有什么用?

語言模板的內容還是非常豐富的,比如你可以看看xilinx推薦的文件頭是什么樣的:

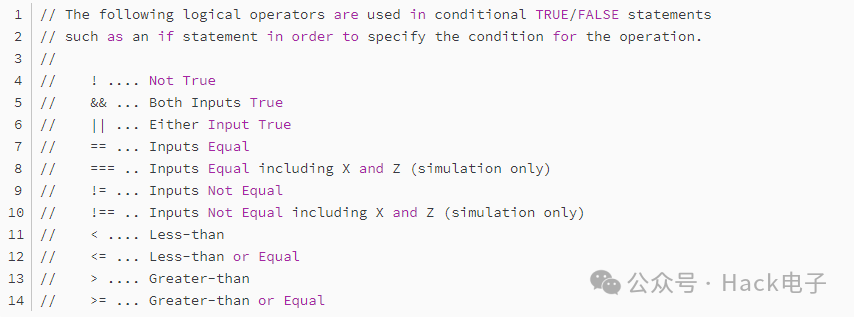

Verilog語法(邏輯運算符):

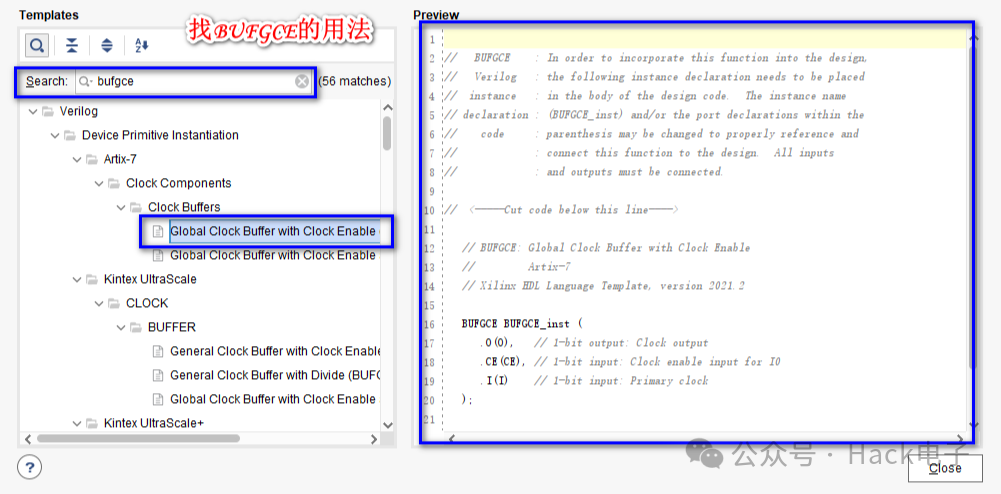

找不到原語使用方式的時候,也可以來這里查找(當然你也可以查xilinx的官方文檔):

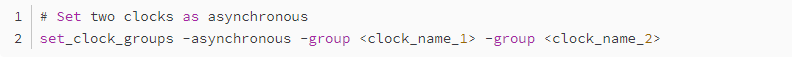

有些時序約束語法不太好記,你可以用這個工具查找,比如:

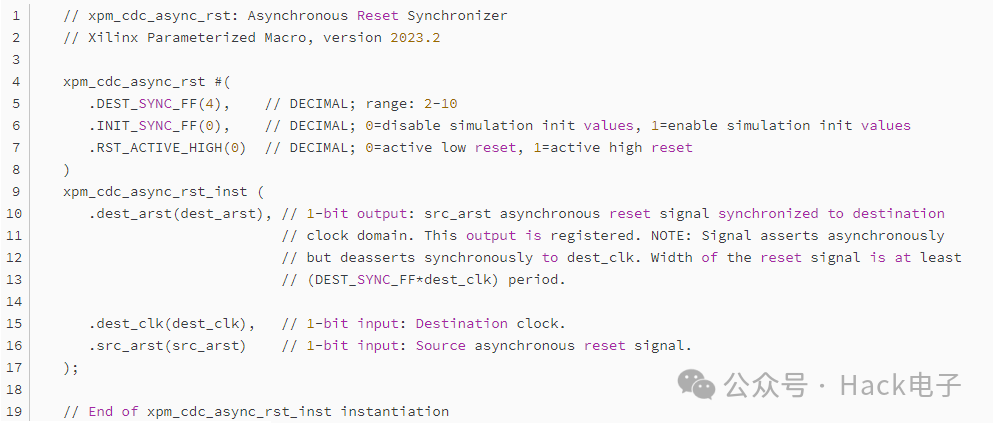

看看xililnx提供的宏XPM(Xilinx Parameterized Macro)是怎么用的,比如CDC這部分的:

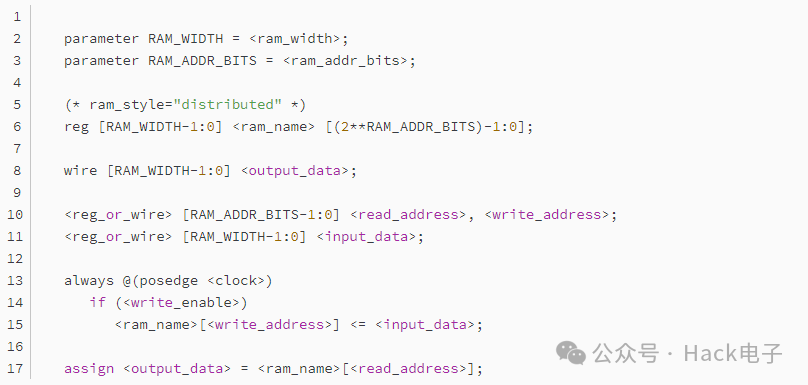

最最重要的一點是,它提供了很多典型電路的設計方法。

由于各家FPGA的結構差異,可能相同的代碼在不同的器件上生成的結構會存在很大差異。比如有時候,可能你想設計的是一個分布式DRAM,但是由于你的代碼風格和綜合工具的原因,它給你生成的事BRAM,那這樣就和你的設計初衷相違背了(當然隨著綜合工具的發展,這類情況是越來越少了)。所以在設計相關電路時,請盡量參考xilinx提供的代碼,以確保vivado能正確生成你想要的電路(Altera 的FPGA類似)。

總 結

● 語言模板可以學習HDL語言語法、綜合屬性等;

● 語言模板可以快速查找設計內容、模板;

● 語言模板提供的電路設計模板可以保證綜合工具能正確推斷出對應的電路。

-

FPGA

+關注

關注

1626文章

21665瀏覽量

601805 -

組合邏輯

+關注

關注

0文章

47瀏覽量

10032 -

環路

+關注

關注

0文章

48瀏覽量

12000

原文標題:FPGA編碼風格集錦

文章出處:【微信號:Hack電子,微信公眾號:Hack電子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

FPGA實戰演練邏輯篇39:代碼風格與書寫規范

FPGA實戰演練邏輯篇41:代碼風格

Linux內核編碼風格(編程代碼風格推薦)

Gowin HDL編碼風格要求及編碼實現

基于FPGA的非編碼無線模塊的應用設計

基于FPGA的非編碼無線模塊的應用設計

基于FPGA的Varint編碼設計原理和實現

關于Linux的內核代碼風格

Gowin HDL編碼風格用戶指南

FPGA編碼風格介紹

FPGA編碼風格介紹

評論