本文檔介紹了采用C2000系列雙核(CM3+C28x)微控制器實現(xiàn)的,基于PRIME標準的電力線通信(PLC)數(shù)據(jù)集中器方案。本方案通過一顆Concerto MCU加SDRAM實現(xiàn)完整的PRIME協(xié)議棧,提供波特率115200bps的UART異步串行端口給客戶端主機進行網(wǎng)絡管理及數(shù)據(jù)通信,為需要低成本實現(xiàn)數(shù)據(jù)集中器功能的場合提供了有效的解決方案。

簡介

PRIME-PoweRline Intelligent Metering Evolution標準是由西班牙Iberdrola電力公司聯(lián)合有關的PLC芯片、系統(tǒng)、電表等廠商,為窄帶PLC電力線通信制定的遠程抄表技術標準,包括物理層和MAC層的數(shù)據(jù)傳輸標準。該技術的協(xié)議開放,實施無版權費用,不同廠商的產品能夠實現(xiàn)互聯(lián)互通。TI采用低成本的DSP控制器,以軟件的方式來實現(xiàn)PRIME協(xié)議,相較其他廠商以專用芯片ASIC的實現(xiàn)方式,提高了應用的靈活性。

事實上,早前TI已經(jīng)采用OMAP1808實現(xiàn)了PRIME數(shù)據(jù)集中器的完整功能。本文介紹的方案,主要是將OMAP平臺的DC方案移植到單芯片Concerto上,實現(xiàn)一顆芯片完成PRIME的上層和底層MAC協(xié)議以及物理層協(xié)議,適用于低成本的嵌入式數(shù)據(jù)集中器應用,因此,我們也把該數(shù)據(jù)集中器方案簡稱為EDC,即Embedded Data Concentrate。

OMAP1808平臺的DC方案基于Linux操作系統(tǒng),而本EDC方案基于TIRTOS操作系統(tǒng),上層和下層MAC通信采用內部數(shù)據(jù)共享,不但系統(tǒng)精簡很多,占用資源少,而且數(shù)據(jù)更加可靠,除了沒有TCP/IP接口之外,所能管理及連接的節(jié)點數(shù)量與OMAP平臺的DC方案無異。

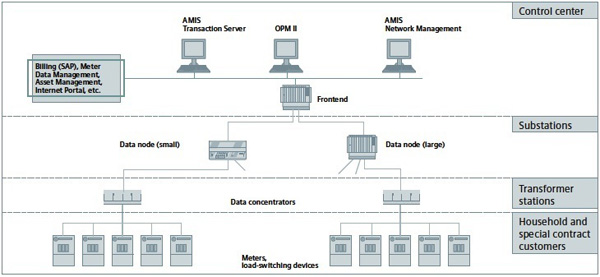

1 EDC系統(tǒng)架構

本方案采用Concerto系列芯片F(xiàn)28M35H52C1作為主芯片,處理PRIME協(xié)議的UPPER MAC及LOW MAC, PHY層協(xié)議。F28M35H52C1是一款雙核的MCU,它內部包含了Cortex m3主系統(tǒng)和TI C28x控制子系統(tǒng)兩個MCU系統(tǒng),每個系統(tǒng)分別有512KB的Flash空間,Cortex m3獨立使用32KB RAM,TI C28x獨立使用36KB RAM,另外還有可配置使用權的 64KB的共享RAM(在EDC系統(tǒng)中全部被分配給C28x使用)和2KB的IPC Message RAM。在EDC系統(tǒng)應用中,Cortex m3核工作主頻為75MHz,它負責處理Upper MAC協(xié)議,C28x核工作主頻為150MHz,它負責處理Low MAC及PHY層協(xié)議,兩個核之間通過IPC內部數(shù)據(jù)共享區(qū)機制進行通信。主芯片MCU外加一個8M Bytes的SDRAM,由CM3核進行訪問,用來存儲節(jié)點信息數(shù)據(jù)庫等數(shù)據(jù),目前系統(tǒng)使用的大小約為3M Bytes;另外有一個128KByts 的EEPROM,由C28x訪問,用來存儲系統(tǒng)掉電參數(shù);模擬前端采用TI AFE031,支持三相和單相連接,由C28x核通過SPI接口對其進行控制。系統(tǒng)框圖如圖1 所示。其中,CM3 通過1個GPIO口控制一個LED,在系統(tǒng)正常工作時以1Hz頻率進行顯示;C28x通過3個GPIO控制另外三個LED,分別指示C28x工作狀態(tài)及PLC通信狀態(tài)。

圖1 PRIME EDC系統(tǒng)架構示意圖

2 EDC方案特性

單芯片實現(xiàn)PLC PRIME DC完整功能。

提供UART接口與PC或用戶Host Processor進行通信,通信速率115200bps,8位數(shù)據(jù)位,1位停止位,無奇偶校驗。

提供PC(Ubuntu Linux OS)客戶端軟件進行模擬測試,客戶端軟件通過mgmt及IEC-432 API接口與EDC上運行的服務器端進行通信,用戶可參考這些客戶端軟件示例代碼實現(xiàn)Host代碼設計,客戶端軟件包括:

Management tool application

Base node conference tool application

IEC 61334-4-32 data transfer application

硬件設計保留C28x的SCIA UART通信接口,便于客戶使用TI提供的PC端ZCG工具軟件,通過連接PC的COM口或USB-UART轉接板至該接口來單獨對PLC PHY層參數(shù)進行測試。

3 硬件設計

3.1 參考原理圖

硬件相關的原理圖部分設計請參考圖2,圖3,圖4 所示。

圖2 主芯片MCU參考設計原理圖

圖3 SDRAM及UART接口參考設計原理圖

圖4 AFE031周邊電路參考設計原理圖

-

電力線

+關注

關注

1文章

89瀏覽量

23466

發(fā)布評論請先 登錄

相關推薦

采用數(shù)據(jù)集中器設計為智能電網(wǎng)提供電力線通信

基于AM335x ARM Cortex-A8 處理器的數(shù)據(jù)集中器參考設計包含原理圖和物料清單

可進行電力線通信的智能電表開發(fā)平臺 (SMB 3.0)包括原理圖,物料清單及光繪文件

G3-PLC電力線通信PLC數(shù)據(jù)集中器參考設計

基于TIRTOS操作系統(tǒng)的PRIME電力線通信數(shù)據(jù)集中器

如何為數(shù)據(jù)集中器選擇合適的處理器

一種新型自動抄表系統(tǒng)數(shù)據(jù)集中器的設計

什么是轉發(fā)器/PLC數(shù)據(jù)集中器

電力線通信數(shù)據(jù)集中器設計方案

Atmel攜手威勝開發(fā)基于PLC的智能電表和數(shù)據(jù)集中器的MoU

德州儀器智能數(shù)據(jù)集中器評估板提供靈活平臺,可連接并管理超過2000個電表

數(shù)據(jù)集中器將AFE,MCU和無線電智能電網(wǎng)效率的關鍵

基于C2000的集成電力線載波通信功能(PLC)光伏逆變系統(tǒng)

TI基于Concerto雙核MCU的PRIME電力線通信數(shù)據(jù)集中器方案應用說明

采用C2000系列雙核實現(xiàn)電力線通信(PLC)數(shù)據(jù)集中器方案

采用C2000系列雙核實現(xiàn)電力線通信(PLC)數(shù)據(jù)集中器方案

評論