1.1指路

延續使用芯片 CH340E 。

1.2數據手冊重要信息提煉

1.2.1概述

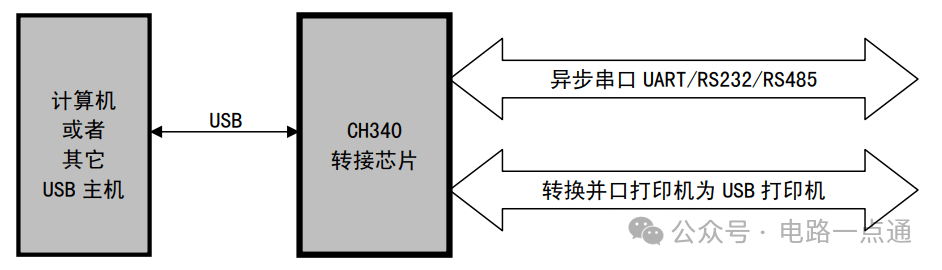

CH340 是一個 USB 總線的轉接芯片,實現USB 與串口之間的相互轉化。

1.2.2特點

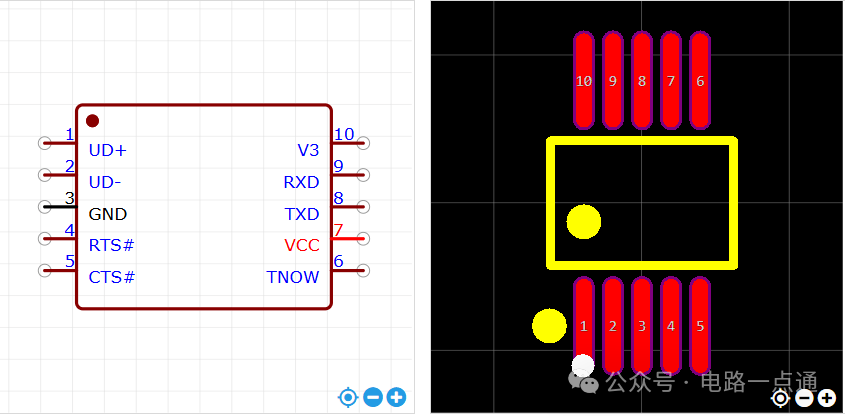

1.2.3引腳

| 引腳號 | 引腳名稱 | 類型 | 引腳說明 |

| 1 | UD+ | USB信號 | 直接連到 USB 總線的 D+ 數據線,不要串聯電阻 |

| 2 | UD- | USB信號 | 直接連到 USB 總線的 D- 數據線,不要串聯電阻 |

| 3 | GND | 電源 | 公共接地端,直接連到 USB 總線的地線 |

| 4 | RST# | 輸入 | CH340B:外部復位輸入,低電平有效,內置上拉電阻 |

| 5 | CTS# | 輸入 | MODEM 聯絡輸入信號,清除發送,低(高)有效 |

| 6 | TNOW | 輸出 | CH340T/E/X/B:串口發送正在進行的狀態指示, 高電平有效。CH340X 外加電阻可切換為 DTR# |

| 7 | VCC | 電源 | 3.3V 正電源輸入端,需要外接 0.1uF 電源退耦電容 |

| 8 | TXD | 輸出 | 串行數據輸出 |

| 9 | RXD | 輸入 | 串行數據輸入,內置可控的上拉和下拉電阻 |

| 10 | V3 | 電源 | 在 3.3V 電源電壓時連接 VCC 輸入外部電源 在 5V 電源電壓時外接容量為 0.1uF 退耦電容 |

1.2.4其他說明

支持常用的 MODEM 聯絡信號 RTS(請求發送)、DTR(數據終端就緒)、DCD(數據載波檢測)、RI(振鈴指示)、DSR(數據設備就緒)、CTS(清除發送)。

通過外加電平轉換器件,提供 RS232、RS485、RS422 等接口。

支持 5V 電源電壓和 3. 3V 電源電壓。

CH340C/N/K/E/X/B 內置時鐘,無需外部晶振。

CH340 未用到的 I/O 引腳可以懸空。

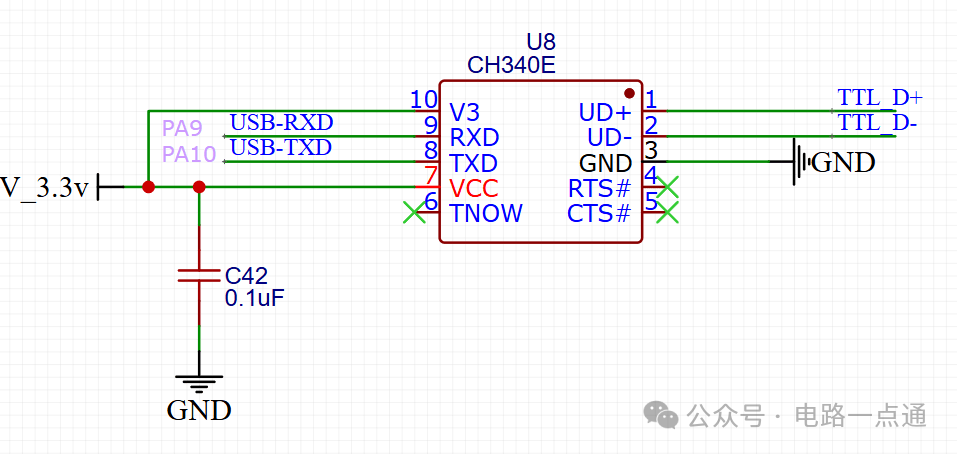

CH340 芯片支持 5V 電源電壓或者 3.3V 電源電壓。當使用 5V 工作電壓時,CH340 芯片的 VCC 引腳輸入外部 5V 電源,并且 V3 引腳應該外接容量為 0.1uF 的電源退耦電容。當使用 3.3V 工作電壓時,CH340 芯片的 V3 引腳應該與 VCC 引腳相連接,同時輸入外部的 3.3V 電源,并且與 CH340 芯片相連接的其它電路的工作電壓不能超過 3.3V。

CH340 芯片內置了 USB 上拉電阻,UD+ 和 UD- 引腳應該直接連接到 USB 總線上。

異步串口方式下 CH340 芯片的引腳包括:數據傳輸引腳、MODEM 聯絡信號引腳、輔助引腳。

數據傳輸引腳包括: TXD 引腳和 RXD 引腳。串口輸入空閑時,RXD 應為高電平。串口輸出空閑時,CH340G/C/N/E/X/B/T 芯片的 TXD 為高電平。

TNOW 引腳以高電平指示 CH340 正在從串口發送數據,發送完成后為低電平,在 RS485 等半雙工串口方式下,TNOW 可以用于指示串口收發切換狀態。

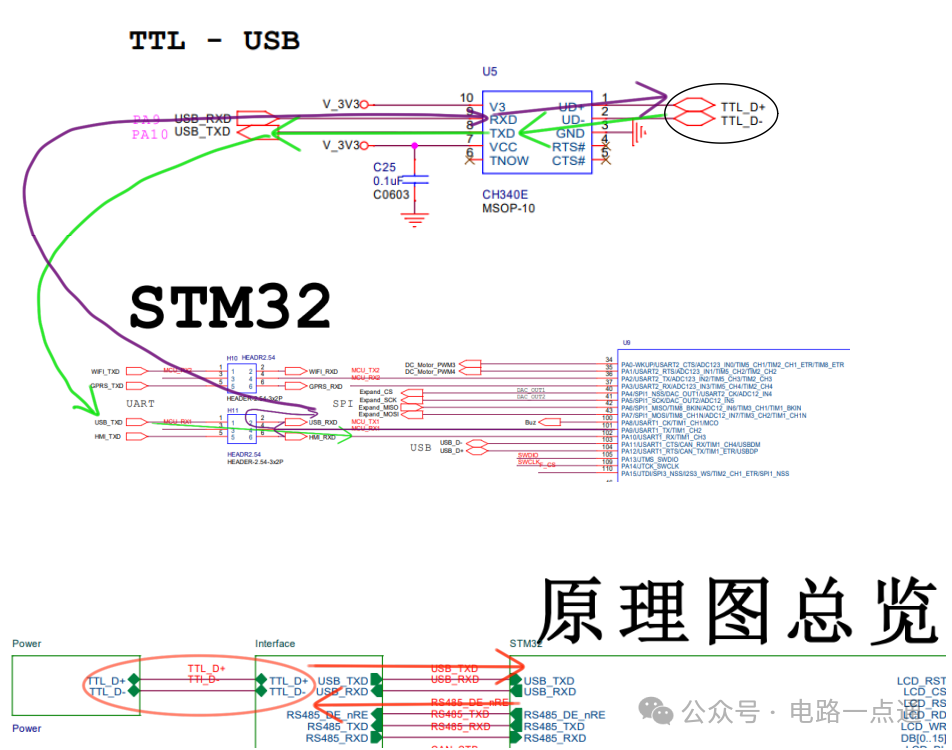

1.3原理圖

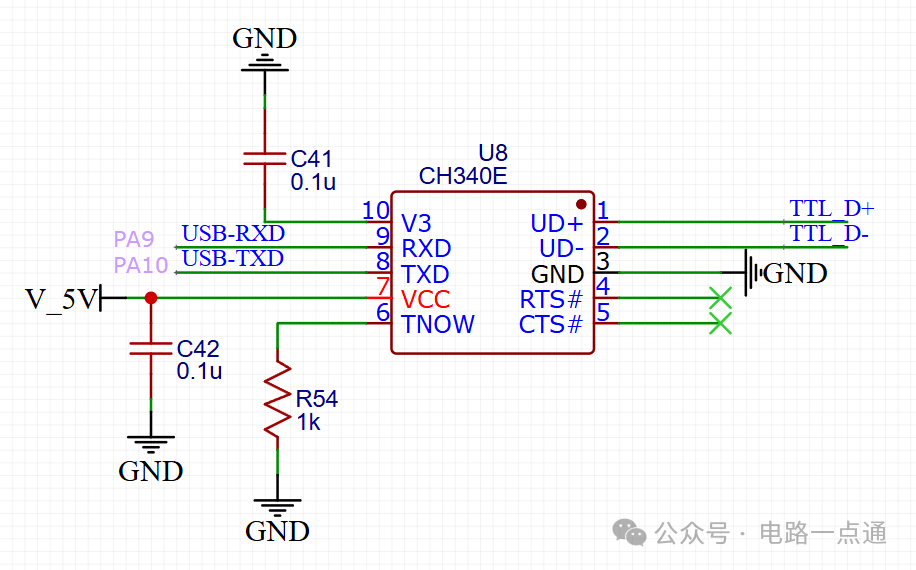

1.3.1 v1.0

存在的錯誤:

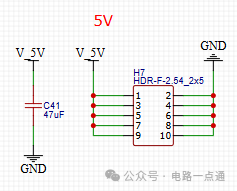

(1)5V 供電

你的依靠原理不成立:雖然之前電源原理圖中 USB 口進行了 5V 供電,但是 5V 供電是為了全局供電,其中的 TTL_D+、TTL_D- 是單純的數據傳輸。

元器件浪費:5V 供電除了 0.1uF 電容濾波之外(數據手冊的意思),還需要 100uF 鋁電解大電容或10uF 電容濾波。

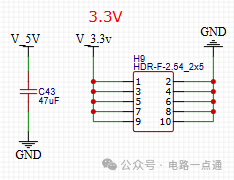

數據手冊中說:3.3V 供電時與 CH340 芯片相連接的其它電路的工作電壓不能超過 3.3V。

信息傳輸后一級的 STM32 和其他主要組件工作在 3.3V,應當選擇3.3V供電,而不是 5V 。

(2)TNOW 引腳

無需進行串口正在發送狀態指示,可以懸空,不用接電阻耗能。

1.3.2 v2.0

1.4 USB信號的全局理解

USB 的 “寫” 是 STM32 的 “讀串口”,USB 的 “讀” 是 STM32 的 “寫串口”。

STM32 原理圖部分應該是通過跳線帽的方式來確認數據的路線。

USB 部分既可以用來供電,又可以用來數據的兩方向傳輸。

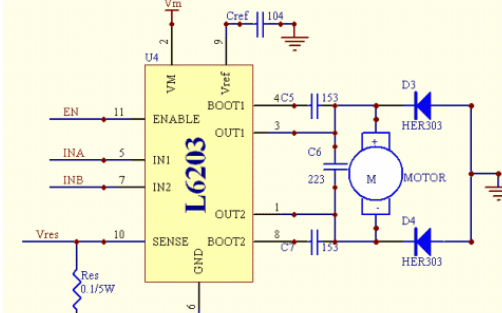

二、RS-485 接口設計

2.1指路

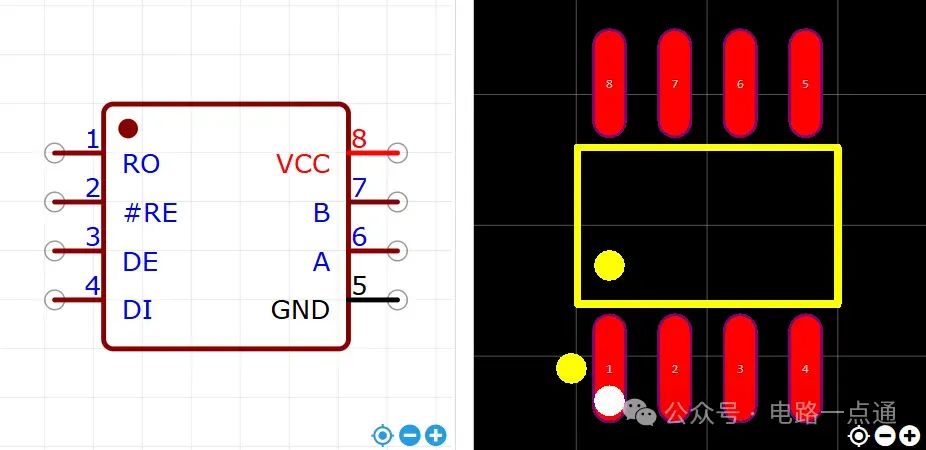

延續使用芯片 SP3485EEN,封裝為SOP-8。

原理圖與PCB圖

2.2.1功能

將外界采用 RS485 通信的設備轉成 串口 通信,得以和單片機進行通信。

2.2.2引腳

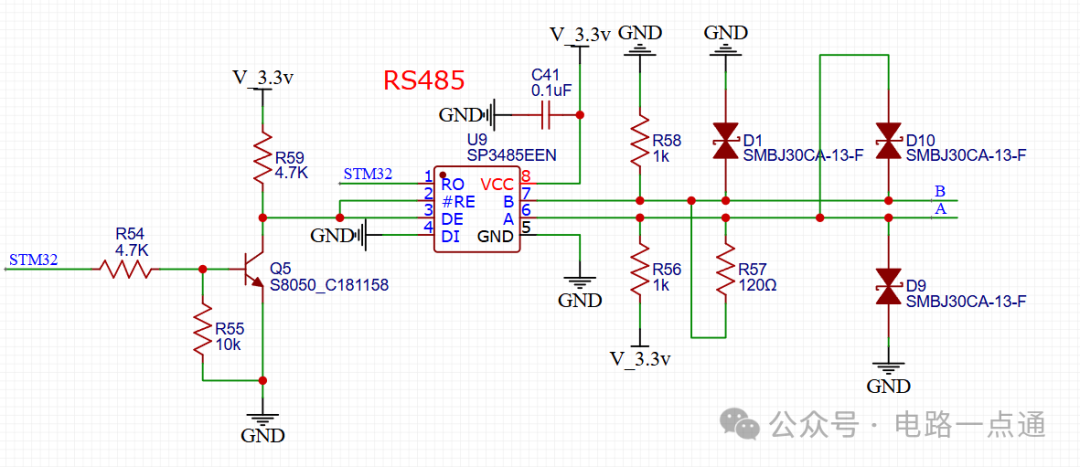

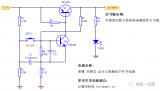

2.3原理圖V1.0

自己根據之前的筆記設計:

(見UART、RS232、RS485基礎知識+硬件知識_uart rs485-CSDN博客)

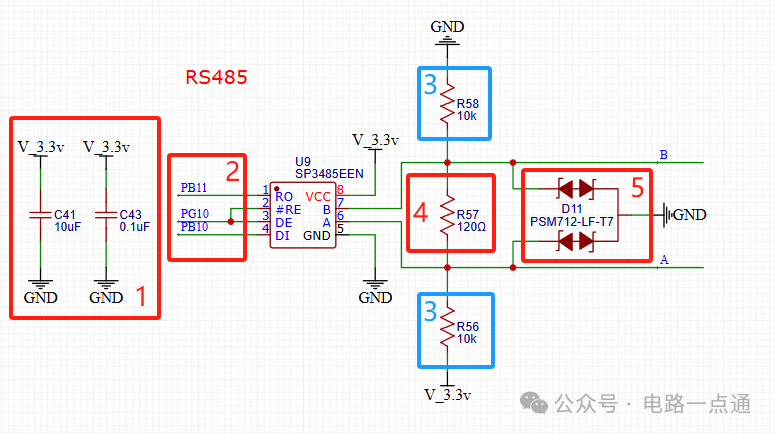

2.4原理圖V2.0

2.4.1濾波電容

我知道你肯定好奇:都是3.3V供電,為什么有的模塊濾波要 0.1uf ,10uf,0.1uf +10uf 濾波?

在這里我只解釋這個模塊的原因,后面再寫博客統一歸納總結。

0.1μF電容:通常用于高頻濾波,抑制高頻噪聲。它們具有較低的等效串聯電感(ESL),適合濾除電源線上高頻噪聲和瞬態干擾。

10μF電容:主要用于低頻濾波,提供較大的電流儲備,能夠平滑電壓波動,穩定電源供應。

組合使用 0.1μF 和 10μF 電容:RS-485 通信需要穩定的電源來保證長距離傳輸的可靠性。0.1μF 電容用于高頻濾波,而 10μF 電容則提供低頻穩定性和電流儲備,從而避免電源波動影響通信質量。

2.4.2引腳

單片機的引腳足夠,不需要 V1.0 的方案來節約引腳,DI 直接接到單片機引腳上,在電路 V1.0 中我選擇是 1K ,老師選擇的是 10K ,分析如下:

2.4.3上下拉電阻

上拉和下拉電阻用于在 RS-485 總線空閑時將總線保持在一個已知的狀態。

(1)10KΩ電阻

陳氏:電阻大,電流小,影響小,功耗低。遠距離或設備多時,可能不足以提供足夠的電流。

優點:功耗較低,適用于大多數情況下的偏置電阻。由于阻值較大,它不會對通信信號產生明顯的負載影響。

缺點:在長距離傳輸或總線電容較大時,可能不足以提供足夠的偏置電流,導致總線狀態不穩定。

(2)1KΩ電阻

陳氏:電阻小,電流大,影響大,功耗高。遠距離或設備多時,提供更足夠的電流。

優點:提供更強的偏置電流,在長距離和較大電容負載情況下能更好地保持總線穩定。

缺點:功耗較高,并且在總線上的負載影響更大,可能在某些情況下影響通信信號的質量。

根據該項目的具體情況,485 設備少,距離近,選擇 10K。

2.4.4 阻抗匹配

2.4.5 TVS管

參考老師建議使用 PSM712-LF-T7 (STO-23封裝),該 TVS 管專用于靜電和浪涌保護。數據手冊中說明常應用于 RS485 端口。

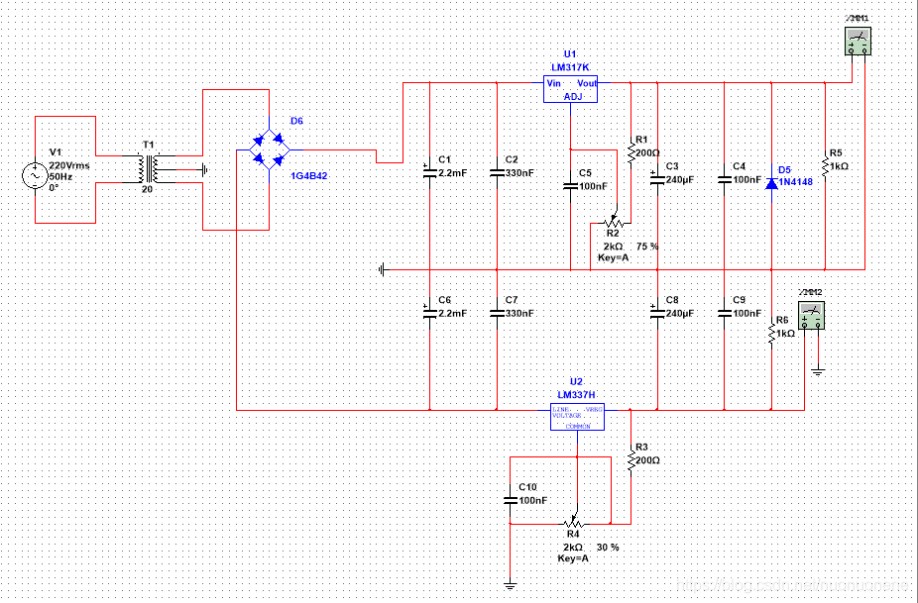

三、CAN 總線接口設計

3.1指路

延續使用芯片 TJA1040T-JSM,封裝為SOP-8。

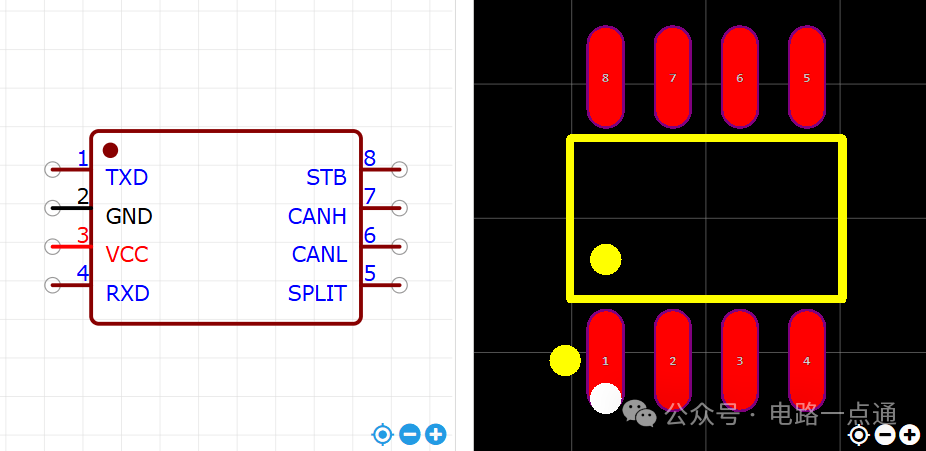

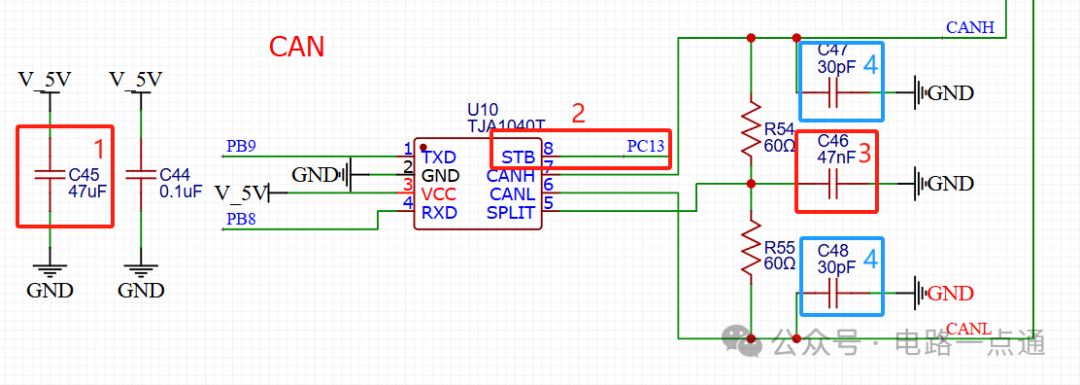

原理圖與PCB

3.2數據手冊

3.2.1概述

TJA1040T 是 CAN 收發器,能夠為信號傳輸速率高達 1Mbps 的 CAN 控制器提供差分傳輸和接收。

3.2.2引腳說明

| 引腳 | 符號 | 說明 |

| 1 | TXD | 傳輸數據輸入。TXD 為高 CAN 總線輸出為隱性態,TXD 為低 CAN 總線輸出為顯性態。 |

| 2 | GND | 地。 |

| 3 | VCC | 供電電壓。 |

| 4 | RXD | 接收器數據輸出。當 CAN 總線處于隱性態時候,RXD 為高電平。當 CAN 總線處于顯性態時候,RXD 為低電平。 |

| 5 | SPLIT | 共模穩定輸出端口。 |

| 6 | CANL | 低電平 CAN 總線端口。 |

| 7 | CANH | 高電平 CAN 總線端口。 |

| 8 | STB | 待機模式控制輸入端口。 |

3.2.3 STB

STB 輸入 (引腳 8 ) 用于在兩個不同的運行模式之間做出選擇,即高速模式或低速模式,使用中可通過將 STB 引腳接地來選擇高速運行模式。

(1)正常模式

通過將 STB 引腳設置為低,選擇芯片的正常工作模式。CAN 總線驅動器和接收器完全工作,CAN 總線雙向通信。驅動器將 TXD 引腳的數字輸入信號轉換為 CANH 和 CANL 引腳的差分輸出電平。接收器將來自 CANH 和 CANL 引腳的差分電平轉換為 RXD 引腳的數字輸出信號。

(2)待機模式

在此模式下,驅動器和接收器關閉,低功耗差分接收器監控總線狀態。引腳 STB 上的高電平激活低功耗接收器和喚醒濾波器,在 tus 時間之后,CAN 總線的狀態會反映在引腳 RXD 上。VCC 上的電源電流降低到最小值,以降低電磁干擾( EM ),同時對總線上喚醒標識進行辨識。在這種模式下,總線接地可將供電電流 ( lcc ) 降至最低。

(3)喚醒

在待機模式下,芯片通過低功耗差分比較器監測總線。一旦低功耗差分比較器檢測到顯性總線電平超過時間 tBus,引腳 RXD 將變為低電平。

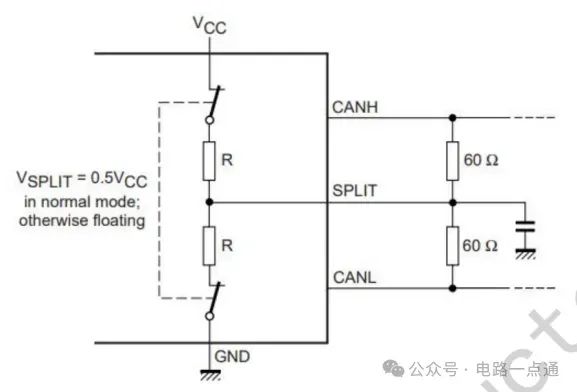

3.2.4 SPLIT

CAN 總線大量節點需要 TJA1040T 這類具有高輸入阻抗和寬共模范圍的收發器收發器。

高輸入阻抗意味著收發器對總線信號的負載很小,減少了每個節點對總線的影響。在大規模網絡中,如果每個節點的輸入阻抗較低,會顯著增加總線的負載,導致信號衰減和失真,進而影響通信的可靠性。高輸入阻抗的收發器允許更多節點同時連接到總線而不會導致上述問題。

共模范圍是指收發器能夠接受的信號電壓范圍。寬共模范圍意味著收發器能夠在較大的電壓范圍內正確地接收信號。CAN總線通信使用差分信號線,但由于不同節點的接地電位可能存在差異,信號線上的電壓可能會有共模偏移。具有寬共模范圍的收發器能夠在存在這些偏移的情況下仍然可靠工作,確保在復雜電氣環境中的穩定通信。

SPLIT典型應用方案

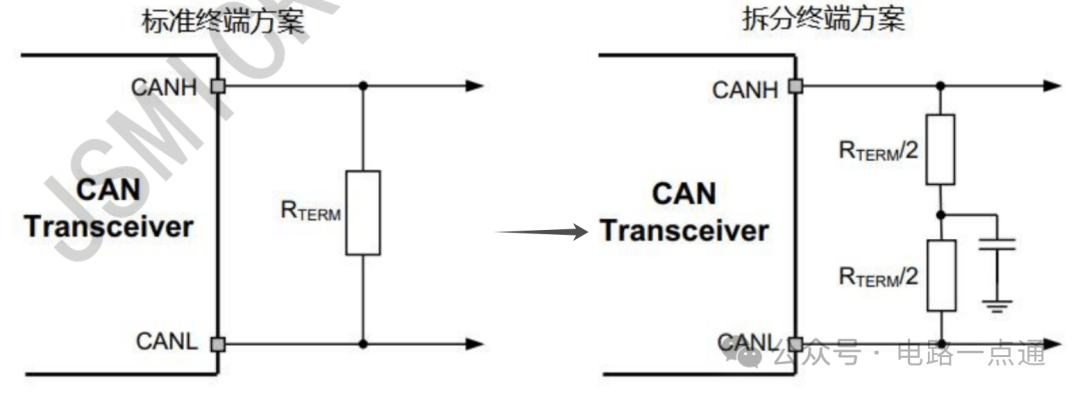

ISO11898 標準規定互連為 120Ω 的雙絞線纜 ( 屏蔽或非屏蔽 ) 特性阻抗 ( Zo ) ,應在線纜終端的兩端使用等于線纜阻抗特性的電阻以防止信號反射,連接節點未端的接入線到總線的距離應保持盡可能短,以最小化信號反射。

總線兩端的匹配終端通常是 120Ω 電阻,如果需要對總線的共模電壓進行濾波和穩定,可使用拆分終端方案(見下圖)。拆分終端方案使用兩個 60Ω 電阻,兩個電阻中間有一個電容接地。拆分終端方案可以消除信號傳輸開始和結束時總線共模電壓的波動,從而改善總線網絡的電磁輻射。

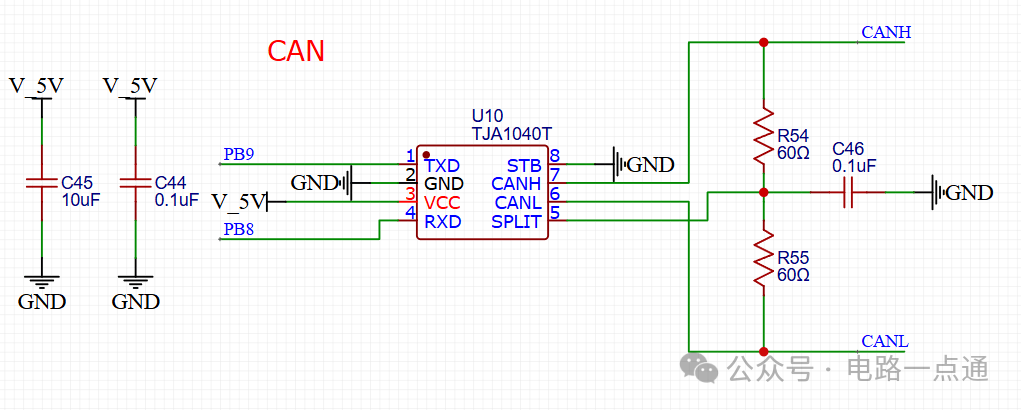

3.3原理圖V1.0

加上參考筆記畫的:CAN總線基礎知識+硬件知識_can總線技術基礎-CSDN博客

3.4原理圖V2.0

第一版設計的電路并沒有什么問題,只是老師設計的電路在實際調試時可能更佳。

器件的數值不用過多糾結,更多的是經驗值或實際調試中效果更好。

根據老師的原理圖有以下改進:

(1)47uF的電源濾波電容:更好地濾除低頻噪聲,穩定電源電壓,尤其是在電流變化較大的情況下更為有效。

(2)STB:接入單片機引腳,改為可以由單片機選擇高速模式或低速模式。

(3)47nF 電容:提供穩定的參考電壓,并濾除中頻噪聲,可以減少電磁干擾,提高總線的信號完整性。

(4)30pF 電容:這些電容用于濾除CAN總線中的高頻噪聲,保護總線的信號完整性。高頻噪聲可能來自于外部的電磁干擾或者內部的高頻開關動作,這些電容可以有效地濾除這些干擾信號,確保CAN總線通信的穩定性。

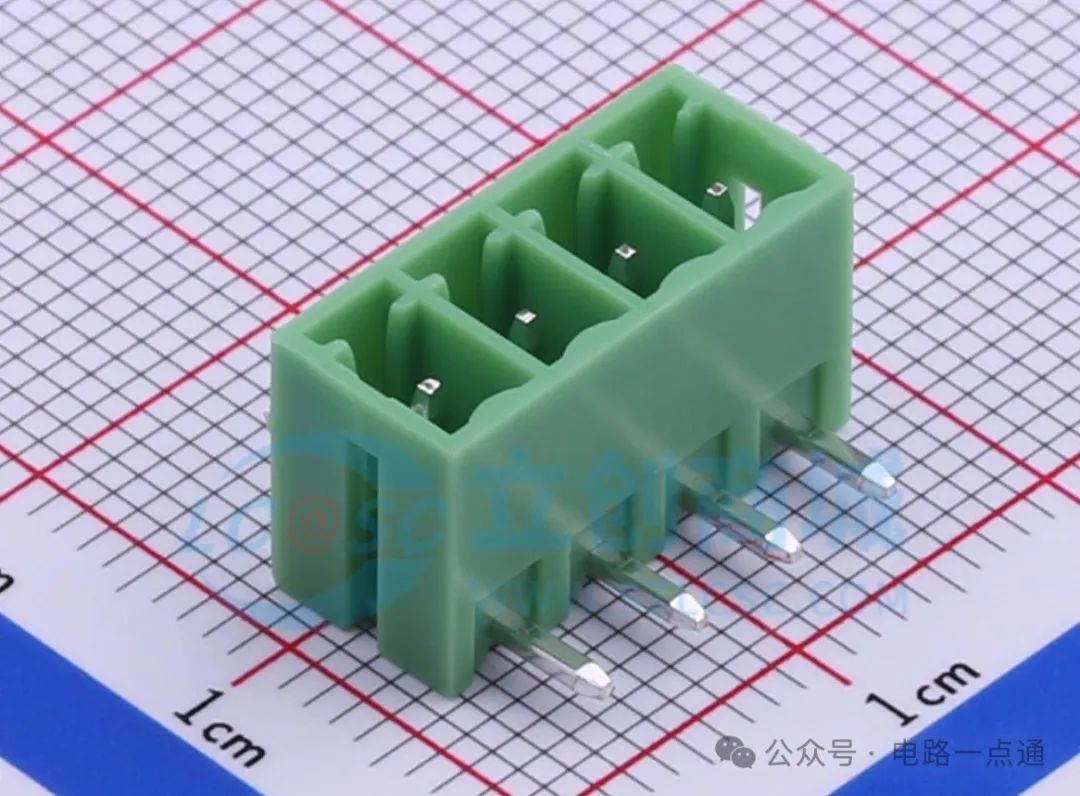

(5)最后 RS485 和 CAN 總線都連接到 KF2EDGR-3.81-4P 插拔式接線端子,方便連接、斷開、調試與維護。

插拔式接線端子實物圖

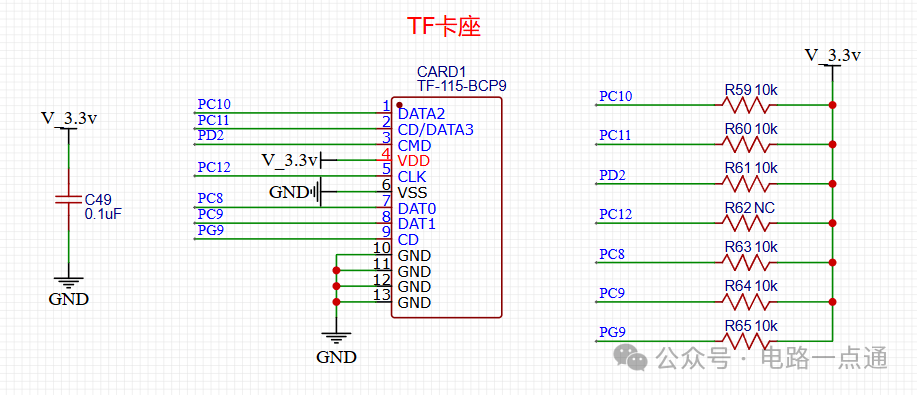

四、TF卡座設計

4.1指路

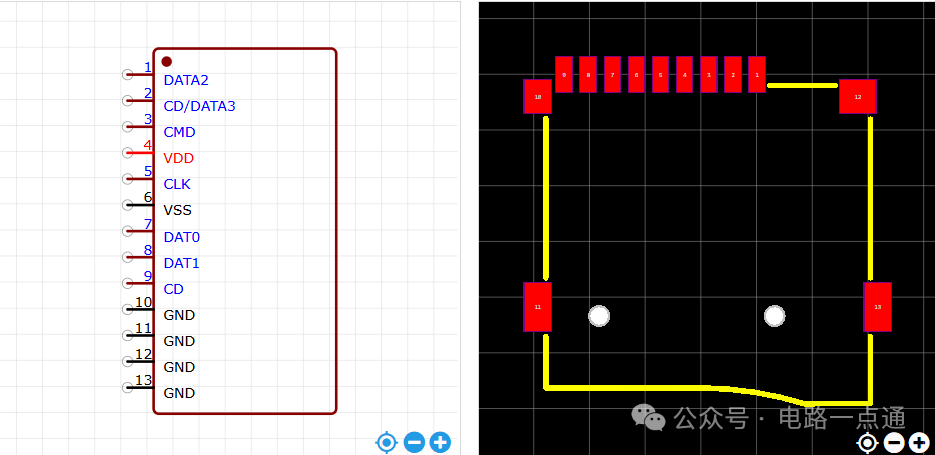

使用芯片:TF-115-BCP9 ,封裝: SMD,描述: 9P 自彈式 TF 卡座,類目:SD卡/存儲卡連接器。

原理圖與PCB圖

4.2引腳說明

| 序號 | 名稱 | 類型 | 說明 |

| 1 | DAT2 | I/O/PP | 數據線(位2) |

| 2 | CD/DAT3 | I/O/PP | 卡檢測 / 數據線(位3) |

| 3 | CMD | PP | 命令響應 |

| 4 | VDD | S | 電源電壓(3.3V) |

| 5 | CLK | I | 時鐘 |

| 6 | VSS | S | 電源地 |

| 7 | DAT0 | I/O/PP | 數據線(位0) |

| 8 | DAT1 | I/O/PP | 數據線(位1) |

4.2.1“類型”說明:

I:輸入。

O:輸出。

PP:推挽輸出。表示該引腳可以輸出高電平或低電平,而不是高阻態。

S:電源引腳。

4.2.2詳細說明

(1)DAT2、DAT0、DAT1 數據線

功能:用于與 TF 卡交換數據,其中 DAT0 是主要的數據傳輸線,DAT1 是一個輔助數據傳輸線。。

接線方式:通常連接到主控芯片的數據總線相應引腳。

(2)CD / DATA3 卡檢測 / 數據線3

功能:在 SPI 模式下,作為數據線 3;在 SD 模式下,還可以用于卡插入檢測。

說明:SPI模式適用于簡單、低速通信,SD模式適用于高速、大容量存儲需求。選擇何種模式取決于應用需求和主控芯片的支持情況。

接線方法: 連接到主控芯片的數據總線或卡檢測電路。

(3)CMD 命令/響應

功能:用于發送命令和接收來自 TF 卡的響應。

接線方法:連接到主控芯片的命令引腳。

(4)CLK 時鐘

功能:提供時鐘信號以同步數據傳輸。

接線方法:連接到主控芯片的時鐘引腳。

4.2.3上拉電阻

該 TF 卡座,不是一直都有卡插入其中,故電路中的上拉電阻是非常必要和常見的,有以下作用:

(1)確保引腳有確定的電平:

在沒有連接外部信號時,上拉電阻可以確保引腳處于一個確定的高電平(3.3V),避免浮空狀態。浮空狀態會導致引腳處于不確定的電平狀態,可能會引發噪聲和誤操作。

(2)提高信號穩定性:

上拉電阻能夠提升信號的抗干擾能力,增強系統的穩定性。尤其是在長線通信或高頻信號環境下,上拉電阻可以減少噪聲對信號的影響。

(3)預防未初始化引腳干擾:

在系統初始化過程中,如果某些引腳尚未被軟件配置,外部信號未連接或信號源暫時關閉,上拉電阻可以避免這些引腳的意外翻轉或錯誤觸發。

4.2.4 NC電阻

在 CLK 電路中,電阻處標明 NC ,表示此處空貼,即此處不貼任何電子器件。如果安裝的話,電路會有另外的功能,或許在性能上會有變化。

(1)時鐘線(CLK)的特殊性

CLK 引腳負責傳輸時鐘信號,這種信號通常是快速且連續的脈沖。在這種情況下,上拉電阻并不總是必要的,因為時鐘信號是主動驅動的,不會處于高阻抗狀態。

時鐘信號由主控芯片直接驅動,當時鐘線沒有時鐘信號時,其電平狀態由主控芯片決定,不會浮動。

(2)避免不必要的干擾

由于時鐘信號頻率較高,上拉電阻可能會引入不必要的干擾或阻抗匹配問題,影響信號完整性。去掉上拉電阻可以減少這種可能性,提高信號的穩定性和傳輸質量。

(3)簡化電路設計

有時候,在設計中簡化電路、減少元件數量也可以提高系統的可靠性和易維護性。對于不需要上拉電阻的引腳,標記為NC可以明確設計意圖,避免誤操作。

4.3電路圖

五、USB2.0 設計

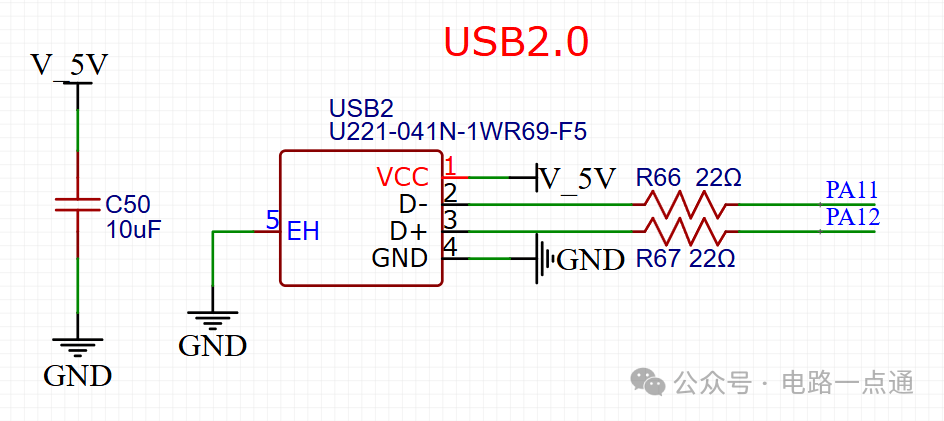

使用 U221-041N-1WR69-F5 器件,設計簡單,直接上圖。

實物圖

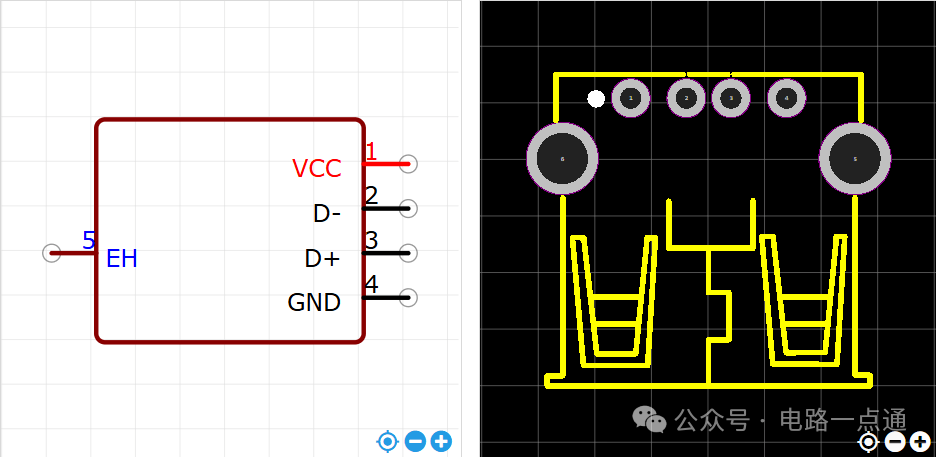

原理圖與PCB圖

設計原理圖

D- 和 D+ 通過 22Ω 電阻連接到 PA11 和 PA12 的設計,是為了匹配阻抗、抑制噪聲、保護微控制器引腳,并提高信號的完整性和穩定性。這種設計實踐在 USB 2.0 應用中廣泛采用,是確保高速數據傳輸可靠性的重要措施,后續有總結筆記總結不同的通信、接口需不需要電阻的問題。

六、IIS

6.1 IIS簡介

IIS(Inter-IC Sound)是一種專門用于數字音頻設備之間傳輸音頻數據的串行總線標準。IIS協議被廣泛應用于數字音頻設備之間的通信,如數字音頻播放器、數字音頻處理器、音頻解碼器等。

6.1.1 IIS的特點

同步傳輸:IIS 是一種同步串行總線,利用時鐘信號來同步數據的傳輸,保證數據的準確性和時序。

多聲道支持:IIS 支持多聲道音頻數據的傳輸,如立體聲、5.1 聲道等。

高質量音頻傳輸:IIS 允許高精度的音頻數據傳輸,通常支持16位、24位甚至32位的音頻數據位深。

分離的數據和時鐘信號:IIS 使用獨立的時鐘信號和數據線來傳輸音頻數據,減少了抖動和失真,保證了音頻的高保真。

6.1.2 IIS接口的引腳和信號

IIS 通常有以下幾個主要信號引腳:

SCK(Serial Clock):串行時鐘信號,用于同步數據傳輸。

WS(Word Select):字選擇信號,用于區分左聲道和右聲道的數據。

SD(Serial Data):串行數據線,用于傳輸音頻數據。

MCLK(Master Clock,可選):主時鐘信號,有些設備使用該信號作為更高頻率的基準時鐘。

6.1.3 IIS接口設計

(1)確定音頻設備和微控制器引腳分配

查閱音頻編解碼器和 STM32 的數據手冊,確定 IIS 信號(SCK、WS、SD、MCLK)的引腳。

在原理圖中,將這些信號對應連接到 STM32 的相應引腳。

(2)時鐘配置

配置 STM32 的外設時鐘,使其滿足 IIS 通信的時序要求。

(3)添加必要的電容和電阻:

在電源引腳(VCC 和 GND)上添加退耦電容(如 0.1uF 和 10uF)。

在時鐘線(SCK、MCLK)和數據線(WS、SD)上添加適當的匹配電阻(如 33 歐姆)以減少信號反射。

(4)設計 PCB 布線:

布線時要注意減少噪聲和干擾,盡量使數據線和時鐘線短且直。

考慮在信號線上加地平面隔離,減少電磁干擾。

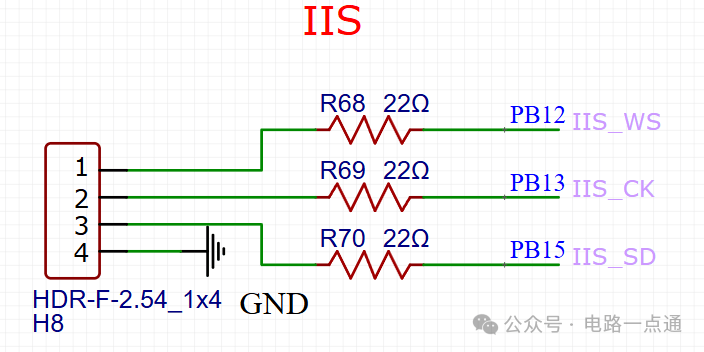

6.2原理圖

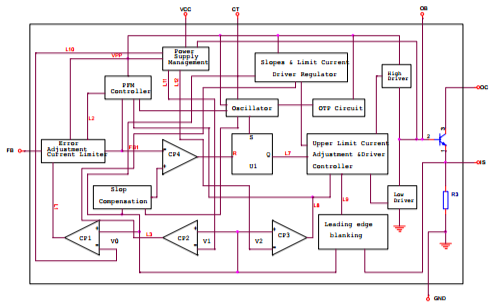

七、電源

八、擴展接口

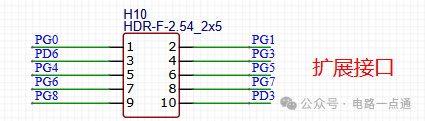

在原理圖中預留了 10 個 GPIO 口用于需要的時候擴展接口。

還可以有以下擴展。

-

接口

+關注

關注

33文章

8496瀏覽量

150834 -

驅動電路

+關注

關注

152文章

1520瀏覽量

108368 -

RS-485

+關注

關注

11文章

679瀏覽量

84174

原文標題:多種接口電路原理圖解析

文章出處:【微信號:fcsde-sh,微信公眾號:fcsde-sh】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

USB接口電路圖解析

多種遙控小車電路圖解析

電動機電氣聯控控制和單向直接啟動控制原理圖解析

鉦銘科電源芯片DK1203兼容RM6203方案原理圖解析及設計思路圖下載

模擬電源和數字電源的原理圖解析

多種接口電路原理圖解析

多種接口電路原理圖解析

評論