人工智能 (AI) 半導體和封裝技術正在快速發展,這得益于 AI 和高性能計算 (HPC) 應用的高性能和復雜需求。隨著 AI 模型的計算量越來越大,傳統的半導體封裝方法難以滿足實現最佳 AI 功能所必需的效率、散熱和信號完整性要求。先進的半導體封裝技術旨在通過提高功率效率、帶寬和小型化來應對這些挑戰。

以下是該領域主要趨勢和技術的細分:

異構集成:異構集成允許將多種類型的半導體(通常采用不同的工藝技術制造)集成到單個封裝中,從而增強計算能力和效率。這種方法在 AI 應用中至關重要,其中 CPU、GPU 和 AI 加速器協同工作,每個都針對特定任務進行了優化。通過堆疊或并排放置這些組件,異構集成可顯著提高 AI 任務的計算速度和能效。

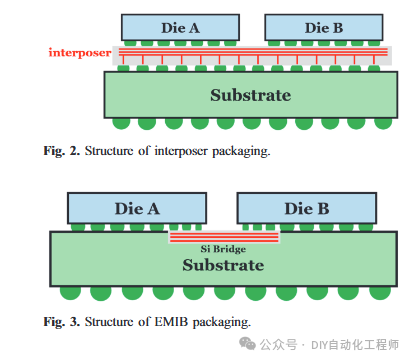

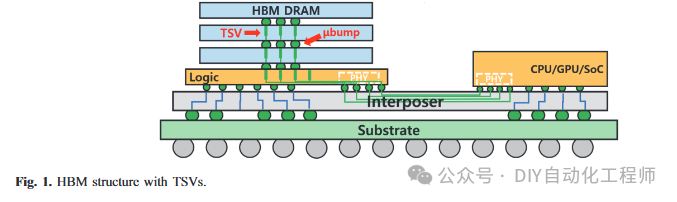

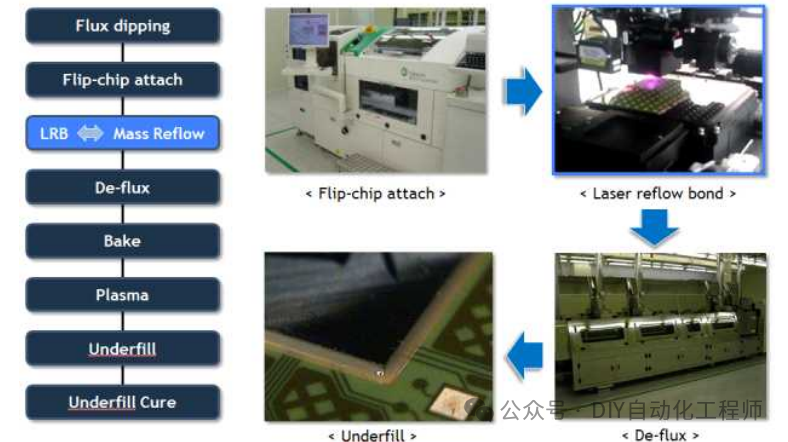

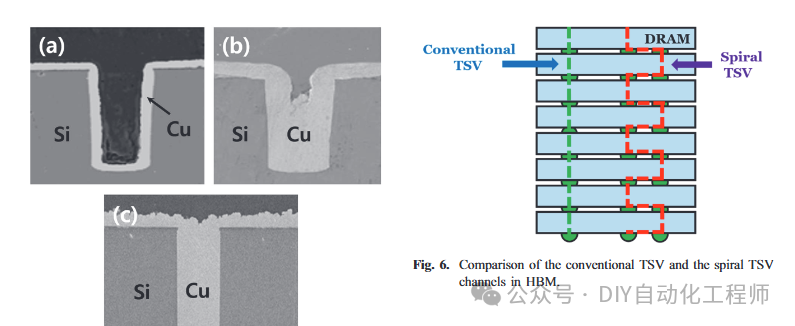

3D 集成和硅通孔 (TSV):硅通孔 (TSV) 是一種用于 3D 集成的方法,其中垂直連接穿過硅晶圓或芯片。該技術縮短了層間互連距離,從而降低了延遲和功耗。在 AI 中,TSV 可實現內存和處理單元之間的高帶寬連接,這對于實時數據處理至關重要。通過 TSV 進行的 3D 集成還有助于小型化,這對于邊緣計算模塊和嵌入式多芯片互連橋 (EMIB)** 等緊湊型 AI 設備至關重要:中介層是先進封裝的一個重要方面,它提供了一個放置多個芯片的基礎層,并通過精細的布線將它們連接起來。這種結構允許高數據傳輸速率和組件之間的可靠連接。英特爾的嵌入式多芯片互連橋 (EMIB) 是這種方法的一種變體,它僅在需要時使用較小的中介層式橋,為復雜的 AI 半導體設計提供了有效的解決方案。中介層和EMIB技術增強了內存和計算核心的性能,使AI應用能夠更快地處理數據密集型任務。

混合鍵合:結合了傳統的銅-銅和氧化物-氧化物鍵合,可在芯片之間創建高度可靠、低功耗的連接。在AI應用中,這種鍵合方法可以實現緊密的芯片集成,從而提高速度并降低功耗。混合鍵合可用于內存和邏輯組件的3D堆疊,減少占用空間并提高數據傳輸速率,這對于需要高速數據移動的AI任務至關重要。

系統級封裝:(SiP)技術將多個組件(如內存、邏輯和通信模塊)封裝在一個封裝中。在AI和HPC應用中,SiP允許組合不同的技術,這些技術可以針對特定任務進行優化,從而減少延遲并提高能源效率。這種模塊化方法正在獲得關注,尤其是在空間有限但處理能力仍然至關重要的AI邊緣計算中。

扇出型晶圓級封裝:扇出型晶圓級封裝 (FOWLP) 擴展了晶圓以允許更多互連,從而提供高性能和更小的占用空間。與傳統封裝方法相比,該技術在 AI 半導體封裝中具有優勢,因為它支持更高的 I/O 密度、更好的熱性能和功率效率。FOWLP 正被用于 AI 加速器和處理器,其中高密度互連和散熱對于處理 AI 的密集處理需求是必不可少的。

未來發展方向:AI 半導體封裝技術面臨著散熱、功率效率和生產復雜性等挑戰。集成這些先進的封裝技術需要克服產量管理、生產可擴展性和成本方面的問題。然而,隨著對高性能、低功耗 AI 芯片的需求不斷增長,旨在克服這些障礙的投資和研究也在不斷增長。未來趨勢表明,多芯片集成、先進互連和混合鍵合技術將繼續改進,以支持 AI 不斷變化的需求。

人工智能驅動的半導體和封裝技術進步有助于滿足下一代人工智能和高性能計算系統對高數據傳輸、處理能力和效率的需求。隨著封裝技術的發展,它們將在提高人工智能硬件的計算效率、可靠性和可擴展性方面發揮重要作用,最終支持人工智能在各個行業的廣泛發展和應用。

-

半導體

+關注

關注

334文章

27063瀏覽量

216485 -

人工智能

+關注

關注

1791文章

46896瀏覽量

237663 -

先進封裝

+關注

關注

1文章

379瀏覽量

224

原文標題:人工智能半導體及先進封裝技術發展趨勢

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

開關電源的最新技術發展趨勢

《AI for Science:人工智能驅動科學創新》第一章人工智能驅動的科學創新學習心得

變阻器的未來發展趨勢和前景如何?是否有替代品出現?

risc-v在人工智能圖像處理應用前景分析

名單公布!【書籍評測活動NO.44】AI for Science:人工智能驅動科學創新

AI芯片制造新趨勢:先進封裝崛起

人工智能芯片先進封裝技術

人工智能半導體及先進封裝技術發展趨勢

人工智能半導體及先進封裝技術發展趨勢

評論